芝能智芯出品

在半导体科技的快速演进中,台积电一直是全球先进制程技术的引领者。近期台积电宣布了一系列雄心勃勃的工艺路线图更新,预示着半导体制造即将迈入一个前所未有的时代——Ångström 级工艺节点到来。

在2025年至2026年间,台积电即将推出的几项关键工艺技术,包括N3X、N2、N2P,以及革命性的A16工艺,揭示它们如何推动技术边界,以及这些进步对电子产品性能、能耗和未来技术发展的影响。

工艺时间表

● 2024年下半年:N3P

◎ 特性:作为N3工艺的增强版,N3P在性能、功耗和密度方面进一步优化,为客户提供更多选择。

● 2025年下半年:

◎ N3X:面向极致性能的3纳米级工艺,通过降低电压至0.9V在相同频率下减少功耗,同时在相同面积下提升性能或提高晶体管密度。

◎ N2:台积电首个采用全栅(GAA)纳米片晶体管的节点,显著提升PPA(性能、功耗、面积)特性,相较于N3E有明显进步。

● 2026年下半年:

◎ N2P:N2的性能增强版本,进一步优化功耗和性能,适合对这两方面都有较高要求的应用。

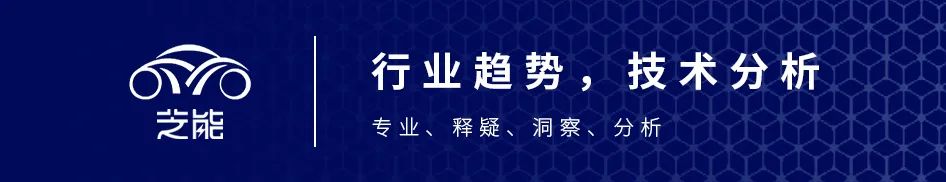

◎ A16:台积电的1.6纳米级工艺,首次引入背面供电网络技术(BSPDN),结合GAAFET纳米片晶体管,目标是在性能和能效上有显著提升。A16将成为首个“埃级”工艺节点,标志着半导体制造进入一个新的时代。

● 工艺迭代背后的关键创新点:

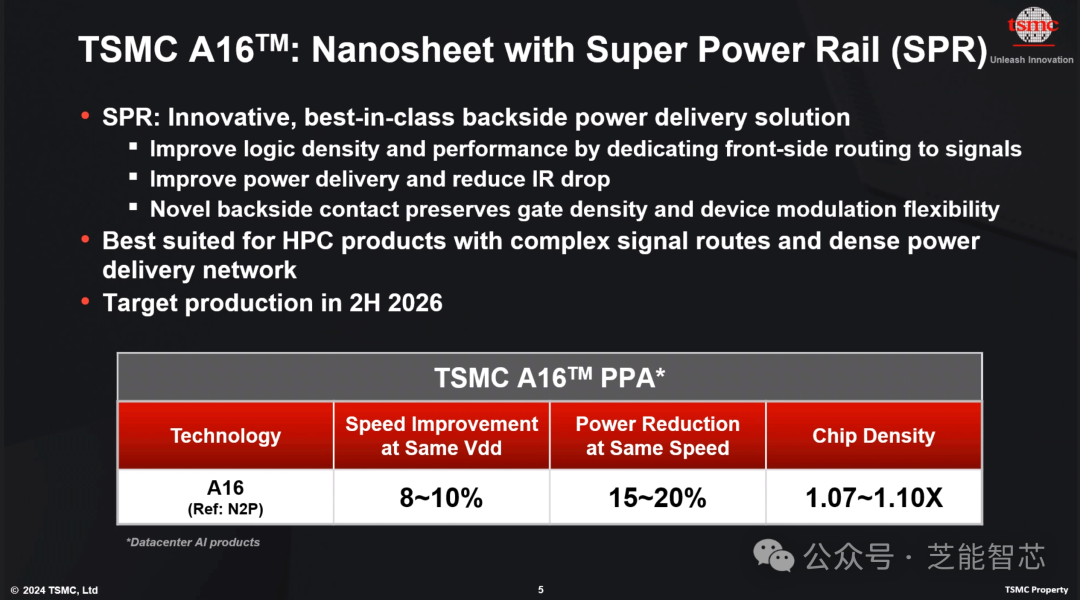

◎ 背面供电网络(BSPDN):A16的最大亮点,直接将电源网络连接到晶体管的源极和漏极,虽复杂但提供了最大的面积缩减效果,代表了台积电在先进封装技术上的重大突破。

◎ GAAFET纳米片晶体管:N2及以后节点的核心,取代传统的FinFET结构,为更高性能和能效提供基础。

N3X:极致性能的3纳米级工艺

技术亮点:

● N3X是台积电3纳米(N3)系列中的高端成员,专为追求极致性能的应用设计。相较于N3P,N3X通过降低操作电压至0.9V,在相同频率下能实现7%的功耗降低,同时在相同面积下提升5%的性能或增加约10%的晶体管密度。对于需要在高频环境下工作的设备,如高性能GPU和服务器处理器,N3X提供了理想的解决方案。

● N2:台积电首探全栅(GAA)纳米片晶体管

◎ 技术里程碑:台积电的N2工艺标志着其首次采用全栅(Gate-All-Around, GAA)纳米片晶体管技术,这是一种与传统FinFET结构截然不同的设计。GAA晶体管通过环绕沟道四周的栅极提高了对电流的控制能力,从而在功耗、性能和晶体管密度上带来显著提升。与前代N3E相比,N2可使功耗降低25%-30%,性能提升10%-15%,晶体管密度增加15%。

● N2P:N2的性能增强版

◎ 优化方向:N2P是N2工艺的性能优化版本,针对特定应用进一步优化了功耗和性能。在相同晶体管数量和频率下,N2P预计能降低5%-10%的功耗,同时提升5%-10%的性能。它为那些寻求在现有N2基础上获得边际性能提升的客户提供了一个更优选项。

● A16:引领埃级工艺时代的到来

◎ 革命性创新:A16工艺技术是台积电进入“埃”级制造的标志性节点,定于2026年下半年推出。A16不仅采用了GAAFET纳米片晶体管,更重要的是引入了背面供电网络(BSPDN)技术,这一创新直接将电源供应集成到晶体管的背面,极大地提升了电力传输效率和晶体管密度。

与N2P相比,A16在相同电压和复杂度下,预计性能提升8%-10%,或在相同频率和晶体管数量下功耗降低15%-20%。这一技术的引入,将为高性能计算产品,尤其是那些对能源效率和信号路径有极高要求的应用,开启新的可能性。

小结

台积电的这一系列工艺技术创新不仅展示了其在半导体制造领域的持续领导力,更为未来电子产品的性能升级、能源效率提升以及更广泛的技术革新奠定了坚实基础。

随着“埃”级工艺节点的到来,半导体行业正步入一个充满挑战与机遇的新时代,台积电的这些技术突破无疑将深刻影响未来十年的科技发展轨迹。从智能手机到数据中心,再到未来的量子计算和人工智能应用,台积电的工艺技术进步都将扮演着不可或缺的角色。