关于LDO话题,很多电源工程师工作中会遇到不同的问题。其实找到问题的根源,才能对症下药。下面给大家分享几篇不错的文章,供大家学习~

LDO(Low Dropout Regulator)是嵌入式系统中广泛使用的器件,也是最基本的模拟类电源,由于其输出噪声小,电路简单,所以在各种应用中都是不可或缺的器件,其中有一些重要的参数对电路的性能影响很大,PSRR就是其中的一个,本文以MIC5235-ADJ输出可调整类型的LDO为例,通过仿真详细分析一下PSRR的曲线及周边电路对其有哪些影响,以便在设计中引起注意。

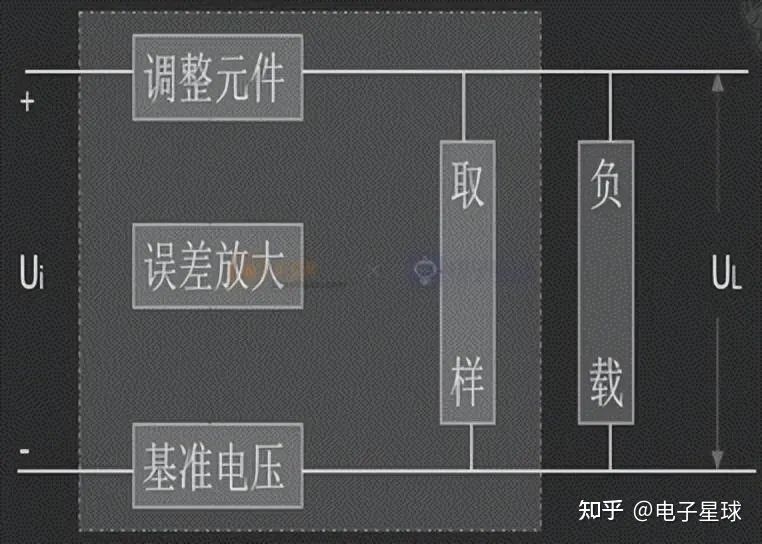

一.LDO的基本概念

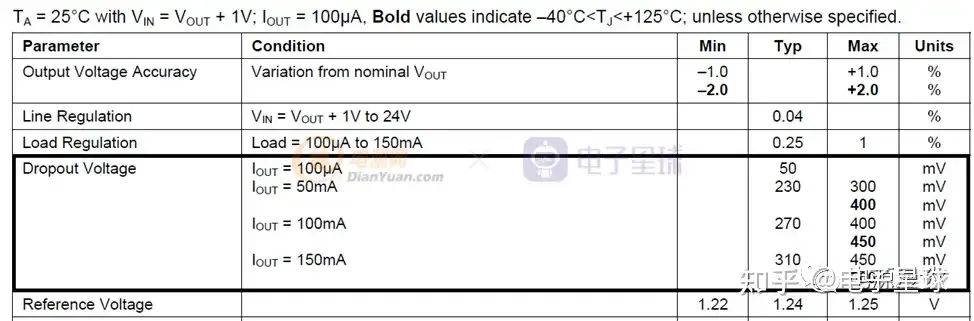

首先,我们简要回顾一下LDO的基本概念,由于LDO本质的结构,导致其效率比较低,在应用中,一般需要保持输入电压和输出电压有一定的压差,当压差越大时,效率就会越低。这里有一个可以做到的最小压差的指标(Dropout),会在规格书中有说明,以MIC5235-ADJ为例,如图1所示。

可以看到,随着负载电流的增加,这个压差参数也会增加,这是一般的特性。在应用中,压差Dropout参数越小,则越容易保持输出电压不变的前提下降低输入电压,提高效率,在电池供电应用中,也更容易提高电池的使用寿命。

PSRR(Power SupplyRejection ratio), 它是指LDO对输入端的AC分量的衰减的参数,PSRR越大,则纹波及噪声从输入端到输出端的衰减比例越大,如图3表达式所示……

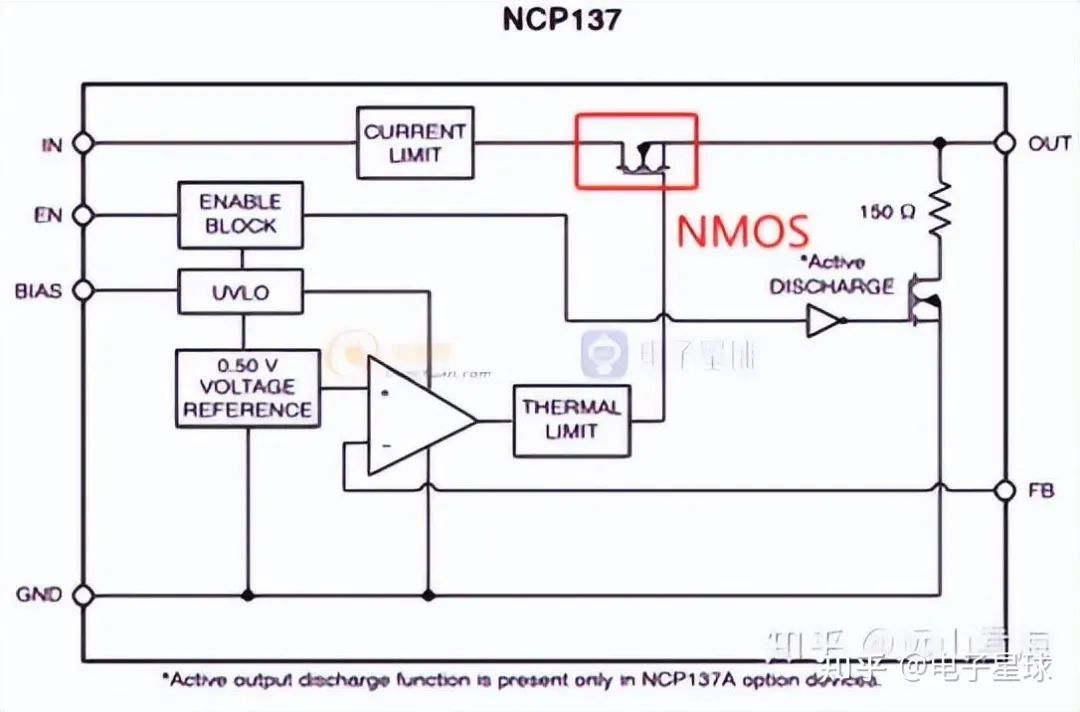

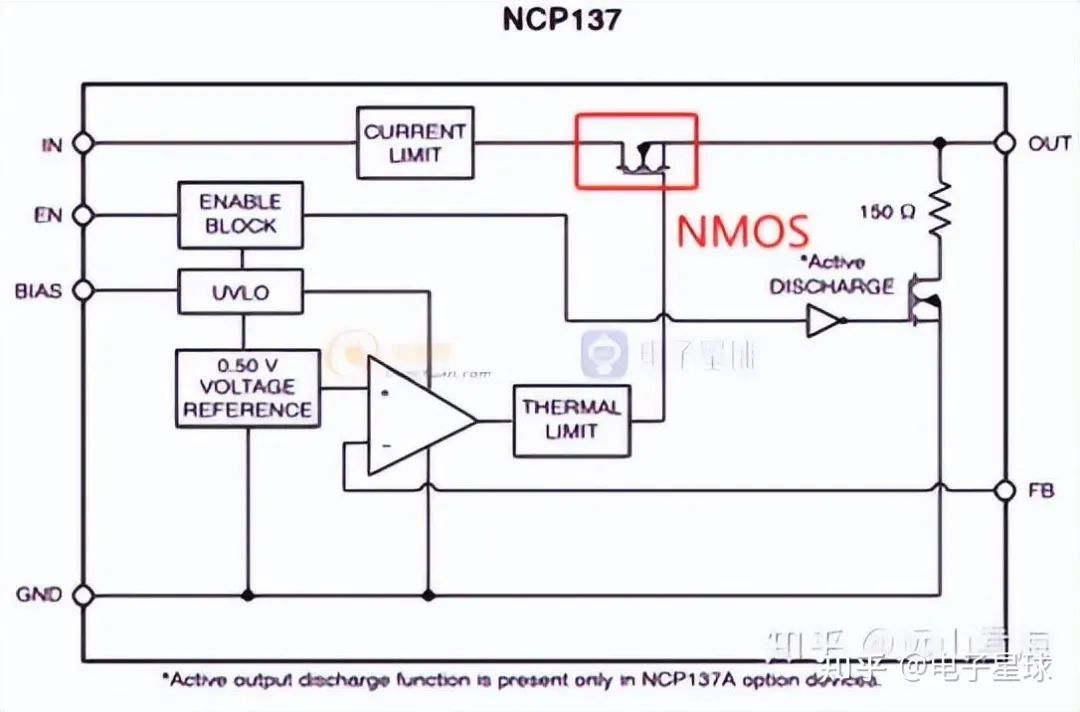

以前文章介绍了PMOS结构线性电源的基本工作原理,今天结合仿真介绍大电流LDO使用的NMOS 架构基本工作原理,以及其他一些重要的LDO参数,包括PSRR、Dropout Voltage等。

NMOS LDO工作简介

下图是一个NMOS LDO的基本框图,NMOS LDO一般也工作在饱和区(特殊时会在可变电阻区),所以Vg要大于Vs,因此NMOS LDO除了有Vin引脚,一般还会有个Vbias引脚来给MOS G极提供高压驱动源;或者只有一个Vin,而内部集成了CHARGE BUMP来为G极提供高压驱动源。大体工作流程同PMOS LDO:当Vout下降时,反馈回路中的Vfb也会下降,误差放大器输出端Vg就会增加,随着Vg增加,Ids电流也增加,最终使得Vout又恢复到原始电平,状态如下:

Vout↓——>Vfb↓——>Vg↑——Iout↑——>Vout↑

2. NMOS LDO详细工作原理

下图是某NMOS输出特性曲线,让我们结合上图和下图分析,当Vout下降,Vin不变,则Vds=Vin-Vout,Vds增加,MOS工作点由A转移到B;紧接着反馈回路开始工作,Vfb电压减小,经过误差放大器后,Vg增加,那么Vgs=Vg-Vs,Vgs也增加,从下图可以看到,随着Vgs增加,MOS的电流Id逐渐上升,进而使得Vout逐渐升高,MOS工作点由B转移到C,LDO又回到原始工作电平……

LDO英文low dropout regulator,意为低压差线性稳压器,是相对于传统的线性稳压器来说的。

传统的线性稳压器,如78xx系列的芯片都要求输入电压要比输出电压高出2v~3V以上,否则就不能正常工作。

但是在一些情况下,这样的条件显然是太苛刻了,如5v转3.3v,输入与输出的压差只有1.7v,显然是不满足条件的。

针对这种情况,才有了LDO类的电源转换芯片。

LDO 是一种线性稳压器,线性稳压器使用在其线性区域内运行的晶体管或 FET,从应用的输入电压中减去超额的电压,产生经过调节的输出电压。

所谓压降电压,是指稳压器将输出电压维持在其额定值上下 100mV 之内所需的输入电压与输出电压差额的最小值。

正输出电压的LDO(低压降)稳压器通常使用功率晶体管作为 PNP,这种晶体管允许饱和,所以稳压器可以有一个非常低的压降电压,通常为 200mV 左右。

与之相比,使用 NPN 复合电源晶体管的传统线性稳压器的压降为 2V 左右,负输出 LDO 使用 NPN 作为它的传递设备,其运行模式与正输出 LDO 的 PNP设备类似。

更新发展使用的 CMOS 功率晶体管,它能够提供最低的压降电压,使用 CMOS,通过稳压器的唯一电压压降,是电源设备负载电流的 ON 电阻造成的,如果负载较小,这种方式产生的压降只有几十毫伏。

DC-DC的意思是直流变(到)直流(不同直流电源值的转换),只要符合这个定义都可以叫DC-DC转换器,包括LDO,但是一般的说法是把直流变(到)直流由开关方式实现的器件叫DCDC。

LDO是低压降的意思,低压降(LDO)线性稳压器的成本低,噪音低,静态电流小,这些是它的突出优点,它需要的外接元件也很少,通常只需要一两个旁路电容……

本来不打算介绍LDO,毕竟这一章是开关电源拓扑专题嘛,但因为LDO和BUCK电路有千丝万缕的联系,大部分开关电源学习都是从线性电源(LDO是线性电源的一种)引入的,而且二者在某些小功率场合也可以相互替代使用。所以还是把LDO部分拿出来作为一篇总结一下吧,以基本原理为重点。

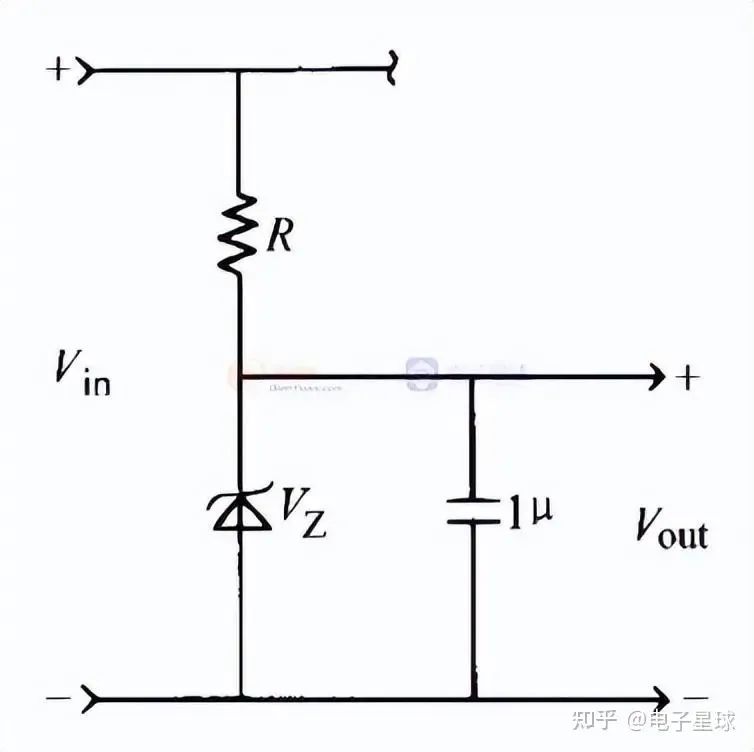

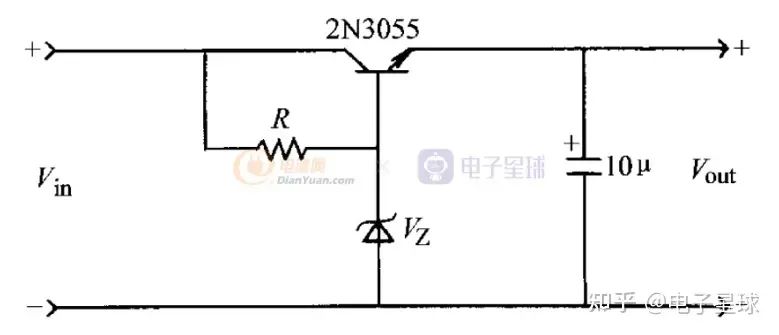

下图1是模拟电路中学习过的最基本的稳压电路,核心器件是稳压管,它的稳压工作区间决定了输出稳压的范围,通过这种简单电路,可以实现小电流(百mA级别),小动态范围内的稳压。图1右边电路仅多了一个2N3055三极管,目的就是提升输出带载能力,同时三极管还引入了电压负反馈,起到稳定输出电压的作用。

当输入电压Vin增大或输出负载电阻增大,输出电压Vout会瞬间增加,三极管的射极电Ve压随之增大,如果基极电压Vb不变,则Vb-Ve就会减小,进而输出电流减小,Vout减小。上述基本调整管稳压电路存在两个问题:(1)输出电压不可调(2)输出电压Vout会受到Vbe电压波动的影响,稳定性较差。因此,目前LDO或线性稳压器通常会引入运算放大器,加深负反馈的同时提高输出电压稳定性。

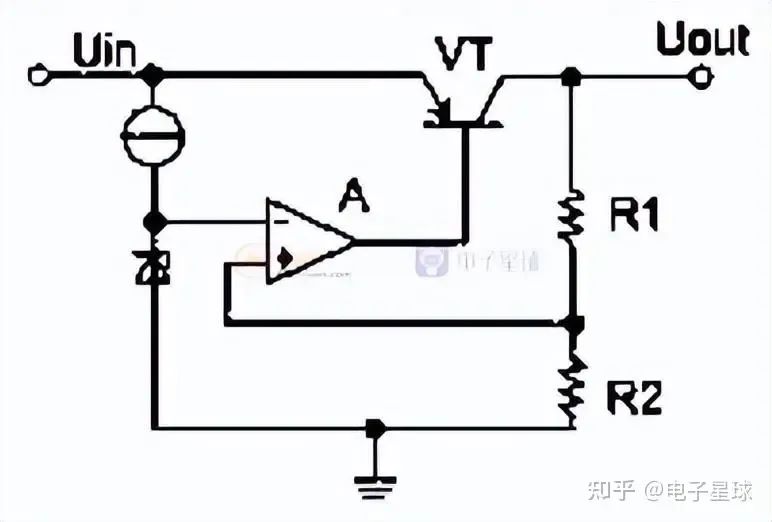

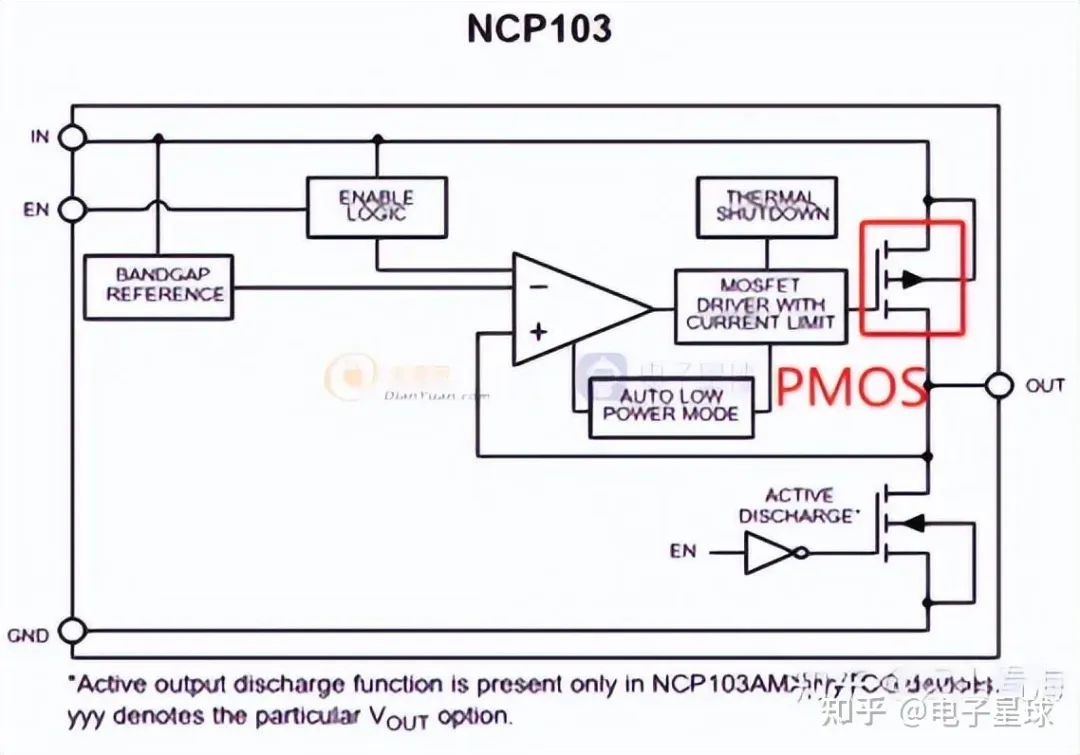

图2所示为通用LDO的原理结构图:在基本稳压管调整电路基础上增加了运算放大器A和分压电阻采样网络R1和R2。当输入电压Vin增大或输出负载电阻增大,输出电压Vout会瞬间增加,通过R1、R2分压采样得到的电压也增加,由于是反向端输入,运放A的输出会相应减小,则Vb-Ve就会减小,进而输出电流减小,Vout减小。下面介绍几种目前常用的LDO或线性稳压器结构……

LDO是我们常用的电源解决方案,dropout voltage(压差)是LDO最常见的参数之一,但是并不是所有的工程师都能够正确的设计LDO dropout voltage,导致产品可靠性具有隐患,降低平均无故障时间。

和DCDC开关电源架构不同,LDO内部的管子是工作在放大状态的,在这样的大前提下,LDO输入输出必须要满足一定的压差条件,LDO才能有效进行反馈调节,正常工作。

对于Dropout Voltage我们一共有两个必关注因素:

第一个因素是Droput Voltage自身的范围,这个在IC内部基本已经固定了,这部分是应用工程师无法管控的,我们只能根据需求合理选型与应用。

先介绍LDO内部影响Dropout Voltage的几个原因,指导大家来正确选型。

LDO内部除了基本的LDO控制电流外,往往还有一些保护电路、放电电路、逻辑控制电路等,有的LDO内部还有电荷泵等接口,这些电路都是要吃电的,所以LDO的dropout voltage除了考虑内部管子的工作状态之外,还要考虑内部其他电路的供电需求。

比如下面的LDO,输出是1V@Iout=130mA时,Dropout voltage 为140mV,但是输入却不能选择1.14V,这是小于输入电压1.4V的要求,设计将不会保证性能和稳定性,有很多工程师其实是知道这点的,但是在设计时非常容易忘记这一项,一定要仔细检查……

1.要基于输入电源与输出电压范围以及负载范围来确定合适Vdo的LDO方案。

2.要基于系统会性能的具体要求选择

1、根据噪音的要求选择PSRR.噪声等相关指标。

2.是否有待机功耗选择合适静态电流,工作电流等指标。

3.是否有输出电容类型的要求如全陶瓷电容等选择合适拓扑结构。

一定要确定LDO封装是否满足散热要求。

确定封装热阻

1.so8 83°C/W.最小布局面积。

2.so8 48°C/W.1平方英寸铜皮散热面积。

3.TO-263 37°C/W.1平方英寸铜皮散热面积。

4.TO-220 20°C/W.17°C/W 散热器。

温升计算方法:

DT为最大容许的温升(125°)

PD=VIN X Iq+(Vin-Vout)X ILOAD

Iq是稳压器的地管脚电流。

1.需要尽量避免设计使得LDO进入Drop out影响区域

2.如果选择MOS型的LDO,需要考虑RDSON的温度特性对Drop out的影响。

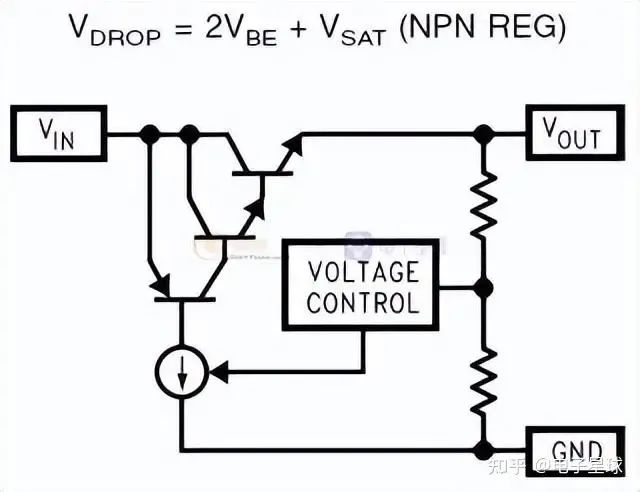

NPN型线性稳压器

1.高性能

2.非常低的工作电流

3.对输出电容几乎没有要求.

4.较高的drop out 电压=2Vbe+Vcesat(典型值>2V)

5.PNP给NPN提供偏置

6.dropout电压2Vbe(0.7+0.7)+Vcesat(0.3V) ,所以输入输出电压差大

7.静态电流随负载电流的变化而变化,主要是影响NPN,PNP的导通程度

8.较高的drop out电压1.5-2.5V

9.几乎不需要外部补偿

10.较低的静态电流……

1.前言:

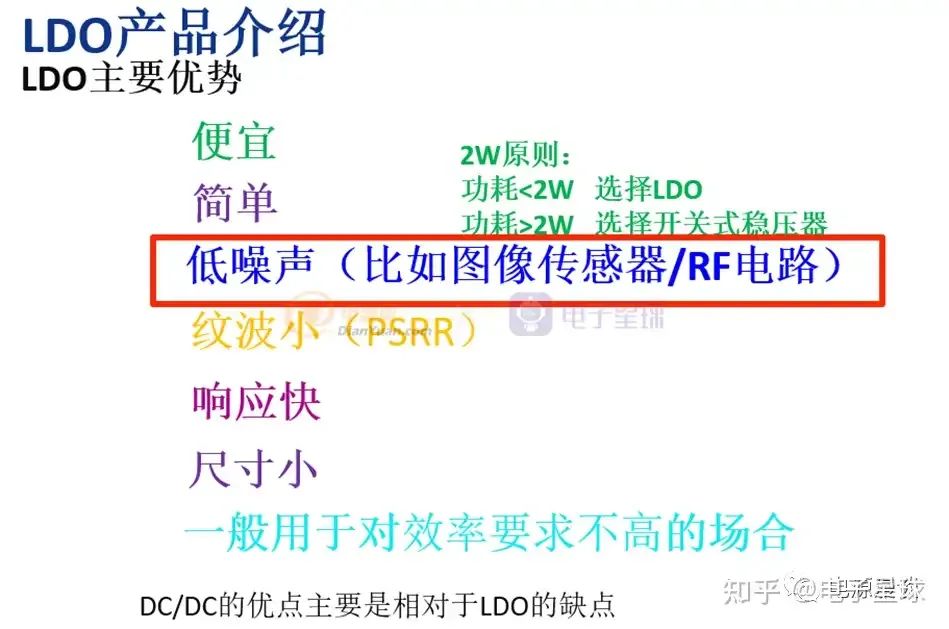

目前市场上无论什么电子产品,只要涉及到电就必须用到电源,电源的分类有很多种,比如开关电源、逆变电源、交流电源等等。在移动端消费类电子产品中,常用的有DCDC电源和LDO电源两种,DCDC的优点是效率高,但是噪声大;LDO正相反,它是效率低,噪声小。

这两种电源具体在什么场景下使用不能一概而论,通常而言,对于噪声不太敏感的数字电路多可以优先考虑DCDC,而对于模拟电路,由于对噪声比较敏感,可以优先考虑LDO。

目前由于技术的进步,DCDC的噪声已经可以减小很多了,但是相比于LDO还是稍逊一筹,今天我们来讨论下LDO的基本工作原理,仿真一个简单的LDO模型,介绍一下LDO使用过程中的相关注意事项。

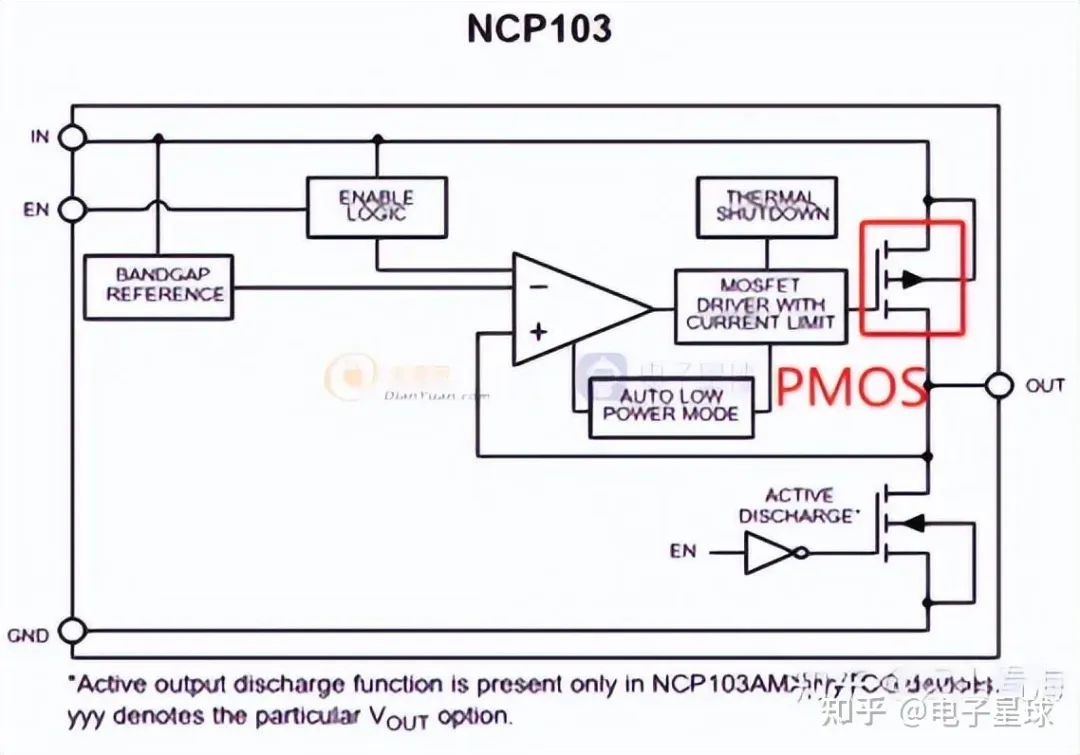

2. LDO分类

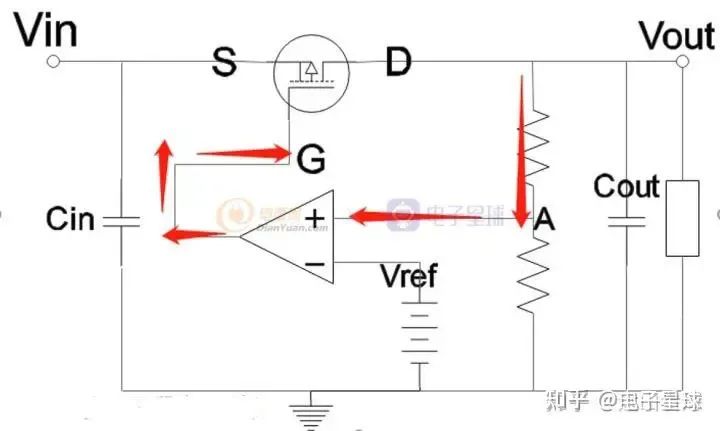

常见的LDO是由P管构成的,由于LDO效率比较低,因此一般不会走大电流。针对某些大电流低压差需求的场合,NMOS LDO应运而生。下图是PMOS和NMOS LDO的系统框图对比。我们暂且忽略系统的传递函数,把目光集中到LDO调节稳定的工作过程,下面我们就着重来介绍下PMOS LDO的基本工作原理。

3. PMOS LDO基本原理

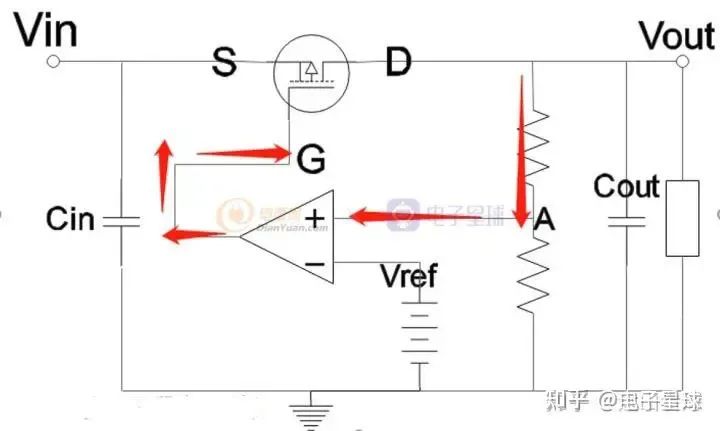

下面是一个PMOS LDO最基本结构框图。我们可以看到LDO主要由PMOS、运放、反馈电阻和基准参考电压构成。LDO主要工作流程是将输出电压通过分压电阻分压,Va和基准参考电压做比较,通过运放输出Vg来调节输出,反馈回路已用红色轨迹标识出,具体原理分两个方面详细介绍。

A.反馈回路

当Vout由于负载变化或其他原因电压下降时,两个串联分压电阻两端的电压也会下降,进而A点电压下降,A点的电位和Vref电位相比较,误差放大器会减小它的输出,使得G电位下降,Vs电压不变,进而使得|Vgs|的压差增加(我们用Vgs和Vds的绝对值描述PMOS更直观),输出电流Isd会增加,输出电流Isd增加就会使得Vout上升,完成一次反馈控制,使得Vout又回到正常电位……

1.前言:

目前市场上无论什么电子产品,只要涉及到电就必须用到电源,电源的分类有很多种,比如开关电源、逆变电源、交流电源等等。在移动端消费类电子产品中,常用的有DCDC电源和LDO电源两种,DCDC的优点是效率高,但是噪声大;LDO正相反,它是效率低,噪声小。

这两种电源具体在什么场景下使用不能一概而论,通常而言,对于噪声不太敏感的数字电路多可以优先考虑DCDC,而对于模拟电路,由于对噪声比较敏感,可以优先考虑LDO。

目前由于技术的进步,DCDC的噪声已经可以减小很多了,但是相比于LDO还是稍逊一筹,今天我们来讨论下LDO的基本工作原理,仿真一个简单的LDO模型,介绍一下LDO使用过程中的相关注意事项。

2. LDO分类

常见的LDO是由P管构成的,由于LDO效率比较低,因此一般不会走大电流。针对某些大电流低压差需求的场合,NMOS LDO应运而生。下图是PMOS和NMOS LDO的系统框图对比。我们暂且忽略系统的传递函数,把目光集中到LDO调节稳定的工作过程,下面我们就着重来介绍下PMOS LDO的基本工作原理。

3. PMOS LDO基本原理

下面是一个PMOS LDO最基本结构框图。我们可以看到LDO主要由PMOS、运放、反馈电阻和基准参考电压构成。LDO主要工作流程是将输出电压通过分压电阻分压,Va和基准参考电压做比较,通过运放输出Vg来调节输出,反馈回路已用红色轨迹标识出,具体原理分两个方面详细介绍。

A.反馈回路

当Vout由于负载变化或其他原因电压下降时,两个串联分压电阻两端的电压也会下降,进而A点电压下降,A点的电位和Vref电位相比较,误差放大器会减小它的输出,使得G电位下降,Vs电压不变,进而使得|Vgs|的压差增加(我们用Vgs和Vds的绝对值描述PMOS更直观),输出电流Isd会增加,输出电流Isd增加就会使得Vout上升,完成一次反馈控制,使得Vout又回到正常电位……

6月20日-21日将在上海举办一期高级电源管理芯片设计课程,本课程将讲述电源管理电路中最常见的模块LDO和DC-DC的相关知识、设计技巧和前沿揭秘,包括模拟LDO,数字LDO,电感型DC-DC,电容型DC-DC和最近关注度很高的混合型DC-DC。

--点击图片即转至课程页面

7月16日-17日将在上海举办一期高级数模转换器(ADC)课程,本次课程首先深入探讨大规模时间交织 ADC 的交织器拓扑结构,探讨非理想情况、设计注意事项、建模技术和详细案例研究。随后,特别关注对高性能大规模 TI ADC 至关重要的外设块的设计挑战和解决方案,包括输入缓冲器和参考缓冲器。此外,还研究了极限采样器、残差放大器和时钟等关键 SAR ADC 块,通过全面的案例研究介绍了基本概念和先进技术。

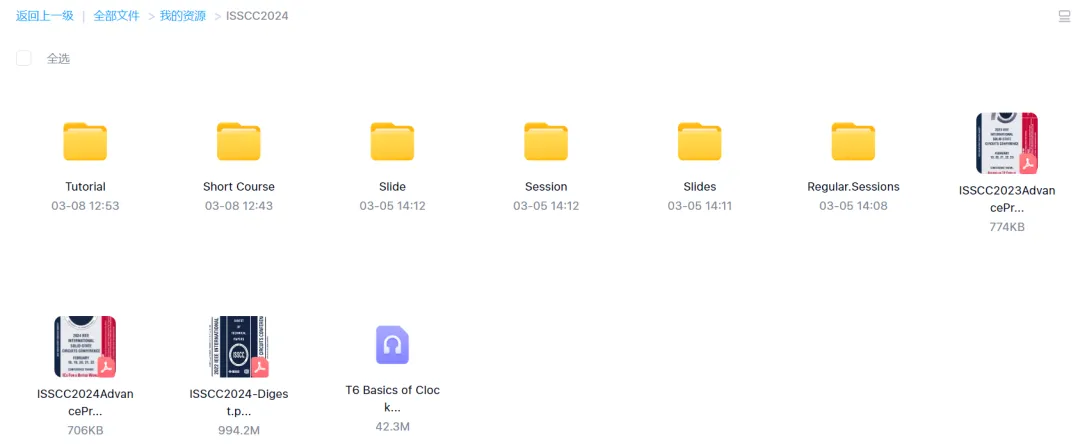

今天小编带来了:ISSCC2024套餐,里面有文章、Short Course、PPT、Tutorial等,同学可以拿回去自己学习研究。

ISSCC2024完整资料领取方式如下

1、深入理解SerDes(Serializer-Deserializer)之一

2、深入理解SerDes(Serializer-Deserializer)之二

3、科普:深入理解SerDes(Serializer-Deserializer)之三

4、资深工程师的ESD设计经验分享

5、干货分享,ESD防护方法及设计要点!

6、科普来了,一篇看懂ESD(静电保护)原理和设计!

7、锁相环(PLL)基本原理 及常见构建模块

8、当锁相环无法锁定时,该怎么处理的呢?

9、高性能FPGA中的高速SERDES接口

10、什么是毫米波技术?它与其他低频技术相比有何特点?

11、如何根据数据表规格算出锁相环(PLL)中的相位噪声

12、了解模数转换器(ADC):解密分辨率和采样率

13、究竟什么是锁相环(PLL)

14、如何模拟一个锁相环

15、了解锁相环(PLL)瞬态响应

16、如何优化锁相环(PLL)的瞬态响应

17、如何设计和仿真一个优化的锁相环

18、锁相环(PLL) 倍频:瞬态响应和频率合成

19、了解SAR ADC

20、了解 Delta-Sigma ADC

21、什么是数字 IC 设计?

22、什么是模拟 IC 设计?

23、什么是射频集成电路设计?

24、学习射频设计:选择合适的射频收发器 IC

25、连续时间 Sigma-Delta ADC:“无混叠”ADC

26、了解电压基准 IC 的噪声性能

27、数字还是模拟?I和Q的合并和分离应该怎么做?

28、良好通信链路性能的要求:IQ 调制和解调

29、如何为系统仿真建模数据转换器?

30、干货!CMOS射频集成电路设计经典讲义(Prof. Thomas Lee)

31、使用有效位数 (ENOB) 对 ADC 进行建模

32、以太网供电 (PoE) 的保护建议

33、保护高速接口的设计技巧

34、保护低速接口和电源电路设计技巧

35、使用互调多项式和有效位数对 ADC 进行建模

36、向 ADC 模型和 DAC 建模添加低通滤波器

37、揭秘芯片的内部设计原理和结构

38、Delta-Sigma ADCs中的噪声简介(一)

39、Delta-Sigma ADCs中的噪声简介(二)

40、Delta-Sigma ADCs 中的噪声简介(三)

41、了解Delta-Sigma ADCs 中的有效噪声带宽(一)

42、了解Delta-Sigma ADCs 中的有效噪声带宽(二)

43、放大器噪声对 Delta-Sigma ADCs 的影响(一)

44、放大器噪声对 Delta-Sigma ADCs 的影响(二)

45、参考电压噪声如何影响 Delta Sigma ADCs

46、如何在高分辨率Delta-Sigma ADCs电路中降低参考噪声

47、时钟信号如何影响精密ADC

48、了解电源噪声如何影响 Delta-Sigma ADCs

49、运算放大器简介和特性

50、使用 Delta-Sigma ADCs 降低电源噪声的影响

51、如何设计带有运算放大器的精密电流泵

52、锁定放大器的基本原理

53、了解锁定放大器的类型和相关的噪声源

54、用于降低差分 ADC 驱动器谐波失真的 PCB 布局技术

55、干货!《实用的RFIC技术》课程讲义

56、如何在您的下一个 PCB 设计中消除反射噪声

57、硅谷“八叛徒”与仙童半导体(Fairchild)的故事!

58、帮助你了解 SerDes!

1、免费公开课:ISCAS 2015 :The Future of Radios_ Behzad Razavi

2、免费公开课:从 5 微米到 5 纳米的模拟 CMOS(Willy Sansen)

3、免费公开课:变革性射频毫米波电路(Harish Krishnaswamy)

4、免费公开课:ESSCIRC2019-讲座-Low-Power SAR ADCs

5、免费公开课:ESSCIRC2019-讲座-超低功耗接收器(Ultra-Low-Power Receivers)

6、免费公开课:CICC2019-基于 ADC 的有线收发器(Yohan Frans Xilinx)

7、免费公开课:ESSCIRC 2019-有线与数据转换器应用中的抖动

8、免费公开课:ISSCC2021 -锁相环简介-Behzad Razavi

9、免费公开课:ISSCC2020-DC-DC 转换器的模拟构建块

10、免费公开课:ISSCC2020-小数N分频数字锁相环设计

11、免费公开课:ISSCC2020-无线收发器电路和架构的基础知识(从 2G 到 5G)

12、免费公开课:ISSCC2020-从原理到应用的集成变压器基础

13、免费公开课:ISSCC2021-射频和毫米波功率放大器设计的基础

14、免费公开课:ISSCC 2022-高速/高性能数据转换器系列1(Prof. Boris Murmann)

15、免费公开课:ISSCC 2022-高速/高性能数据转换器系列2(Dr. Gabriele Manganaro)

16、免费公开课:ISSCC 2022-高速/高性能数据转换器系列3(Prof. Pieter Harpe)

17、免费公开课:ISSCC 2022-高速/高性能数据转换器系列4(Prof. Nan Sun)

点击下方“公众号”,关注更多精彩

半导体人才招聘服务平台