今日碎碎念

今天有号友问,接收机课程(有兴趣的看文章底部)中有没有ADS系统链路仿真的内容。

当然是有的了,而且占比很多。每个分指标的计算后面,都跟着一个仿真验证。所有指标都分配完了以后,还会有一个整体链路的仿真。

整体链路仿真,还分单音时候的验证+调制信号的验证;ADS仿完,再用SystemVue走一遍。

这些仿真步骤,该采用什么模板,各个参数该怎么设置,该用什么等价标准来判断,都是我花了很长时间探索,才联通起来的。

我觉得大概率是全网独一份,因为这些都是我结合软件自带的help文件和模板,再结合项目,一点一点探索出来的,有很多自己的想法在里面。

有的号友会怀疑仿真的意义,我觉得可能都没有经历过仿真带来的益处。假设你接了一个项目,但是并没有师父来带你,或者也没啥前人的经验可以借鉴,那这个时候,能帮忙的也许就只有仿真。大多数的理论猜测,电路验证,系统指标验证,都可以求助于仿真。

今日正文

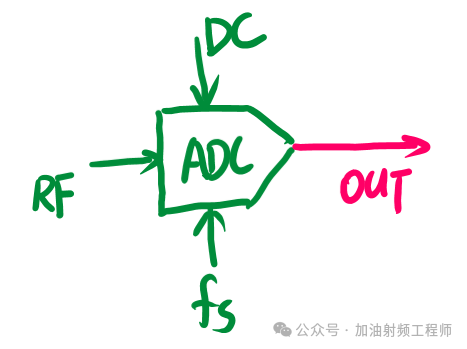

(1) 怎么看ADC

一个ADC,可以把它简单的看成这样一个器件,三个输入,一个输出。

三个输入分别是模拟射频信号输入,时钟输入和电源输入。

一个输出为数字采样信号输出。

(2)ADC的电源选型

市面上有很多型号的LDO和DC-DC,到底应该选择哪种呢。按理说,指标最高的一般都没问题,但是关键指标高的那不是贵么?所以要是能选个指标没那么好,但是和所用ADC搭配刚刚好的器件,那不是又便宜又性能OK么?

与ADC的电源选型相关的,就是ADC的PSSR和PSMR。

当噪声从ADC的电源端引入的时候,噪声可能会直接出现在ADC的输出端,也有可能是噪声与模拟输入信号产生的调制信号出现在ADC的输出端。

举个例子,假设叠加在DC上的噪声信号的频率为1MHz,模拟输入信号为100MHz,而PSSR关注的是ADC输出端的1MHz频率处的幅度,而PSMR则关注的是ADC输出端在101MHz和99MHz频率处的幅度。

ADC厂家的手册上,很多都没有PSSR和PSMR的详细指标。

如果我们对LDO和DCDC的成本敏感的话,比如说出货量很大,单个器件省点就能省下一大笔钱的话,可能就需要自己做些预研工作,测试一下ADC的PSSR和PSMR随频率变化的曲线,以此来选择合适的电源器件。

如果不敏感的话,可能就不费那个事了,直接高指标的电源器件+高抑制的电源滤波,完事。

(3) ADC的时钟电路

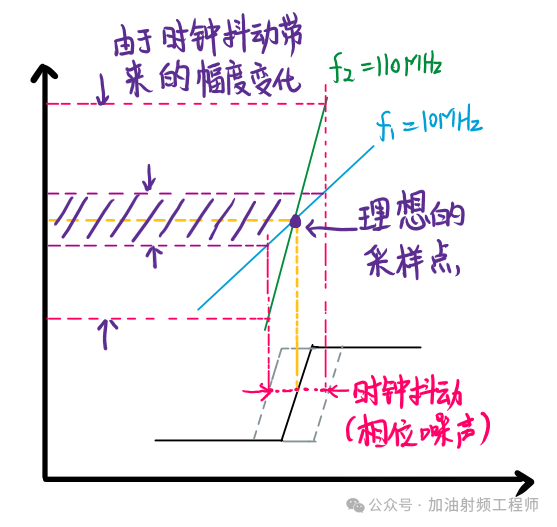

如上图所示,当时钟边沿有抖动的时候,采样的时刻也会有抖动,这样对应的采样数据也会有抖动,而且输入频率越高,由于时钟抖动带来的幅度变化越大。

所以,在评估ADC的时钟是否符合要求的时候,需要综合考虑时钟的抖动带来的影响。

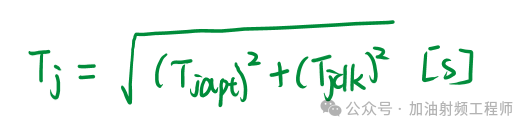

采样时钟抖动Tj是由时钟源(Tjclk)和内部ADC孔径抖动(Tjapt)产生的抖动的组合,即:

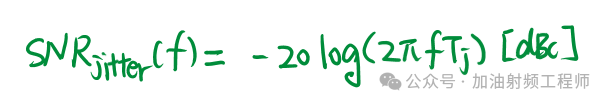

由总抖动导致的ADC的SNR下降,可按以下公式进行计算:

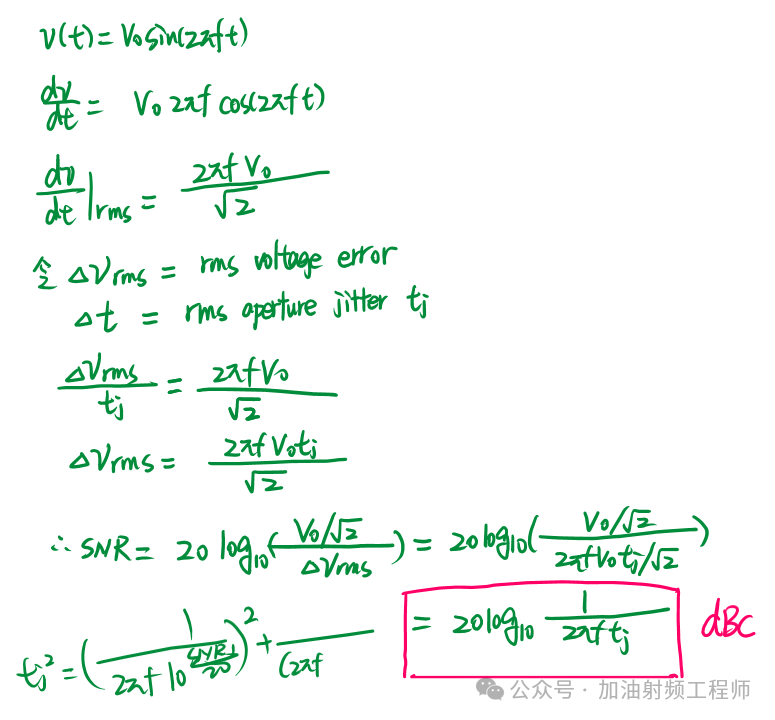

具体推导如下:

这个公式,是假定影响ADC的SNR的只有抖动本身,而ADC的SNR为无穷大。

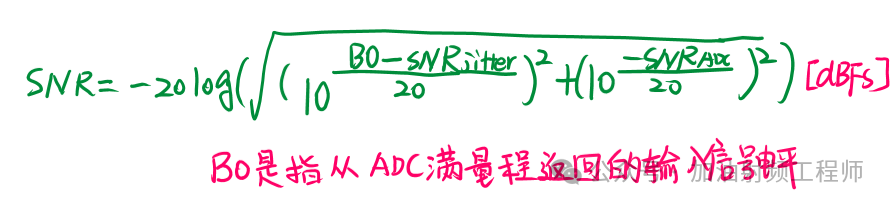

但是,ADC本身受量化噪声和热噪声的影响,所以自身有一个SNR,假设为SNRADC,则:

这边的单位会有点绕,本质上就是由抖动计算出来的SNR的单位是dBc,也就是说以信号的大小为基准的;但是加上ADC本身的SNR之后,由于手册上计算SNR时,都是基于-1dBFS来得到的,所以两者结合起来的时候,划归到统一的单位,即dBFS,所以会有BO这一项。

(4) ADC的输入电路

对ADC的输入电路进行设计的时候,需要根据具体要求,来设计电路。

同时还要考虑抗混叠滤波器。

设计完的电路,拿不准的时候,可以用仿真来验证。

参考文献:

[1] Rob Reeder,MS-2210_Designing Power Supplies for High Speed ADC.pdf

[2] https://www.ti.com.cn/cn/lit/an/zhcab17/zhcab17.pdf?ts=1703650251872&ref_url=https%253A%252F%252Fwww.ti.com.cn%252Fproduct%252Fcn%252FLMX2820

[3] https://www.analog.com/media/en/training-seminars/tutorials/MT-007.pdf

完结接收机课程吆喝处哈(已在平台上购买的同学,加我微信,领课件资料哈!)

想了解接收机的底层理论知识,可以选择这门课;

想了解ADS的系统仿真,可以选择这门课;

想了解SystemVue的系统仿真,可以选择这门课。

想报名的同学,可以海报底部扫码哈!

☜左右滑动查看更多

Slide for more photos