大侠好,欢迎来到FPGA技术江湖,江湖偌大,相见即是缘分。大侠可以关注FPGA技术江湖,在“闯荡江湖”、"行侠仗义"栏里获取其他感兴趣的资源,或者一起煮酒言欢。“煮酒言欢”进入IC技术圈,这里有近100个IC技术公众号。

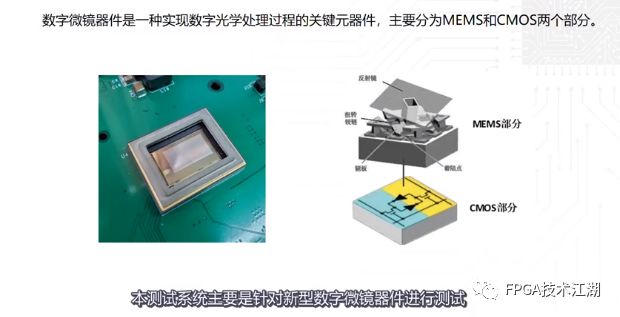

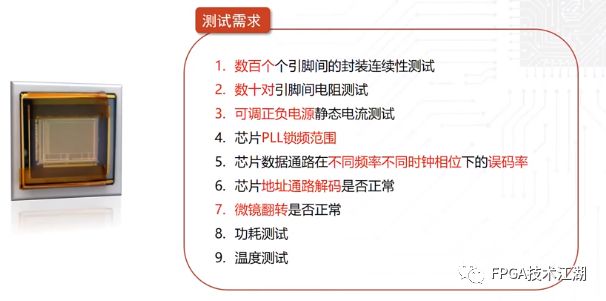

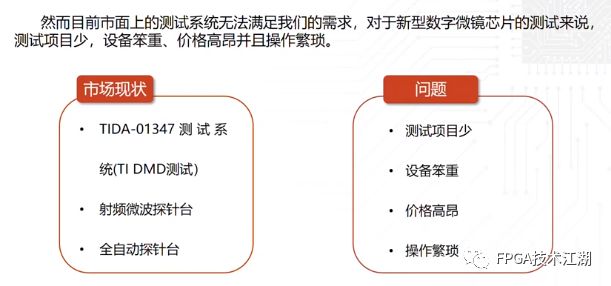

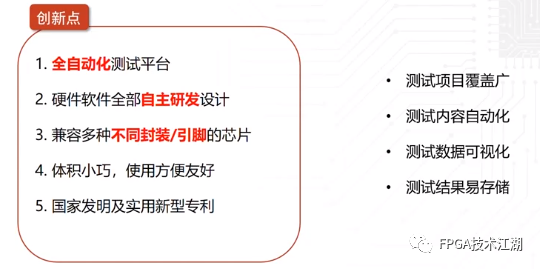

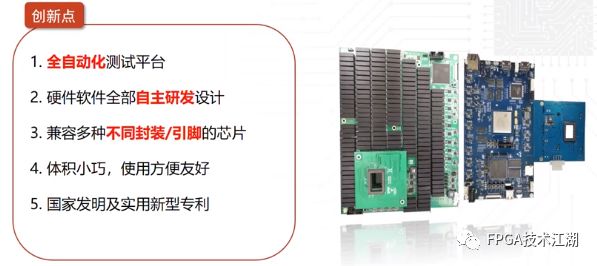

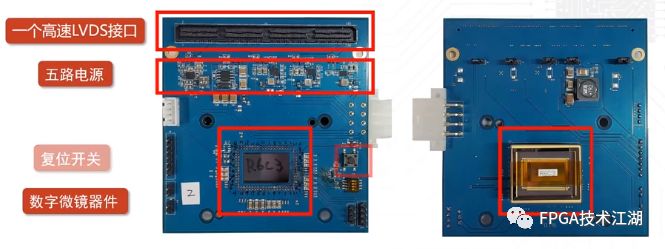

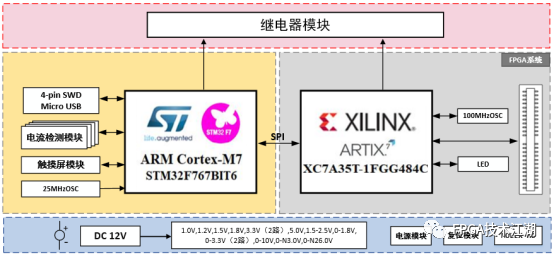

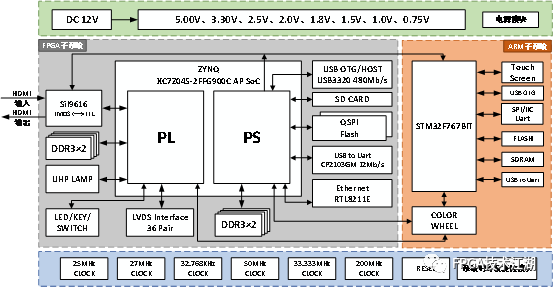

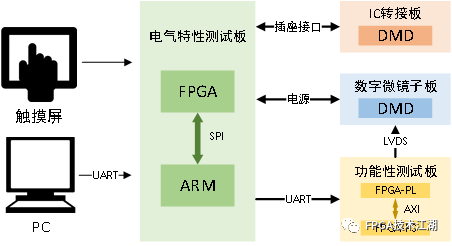

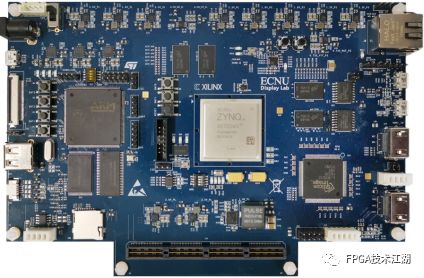

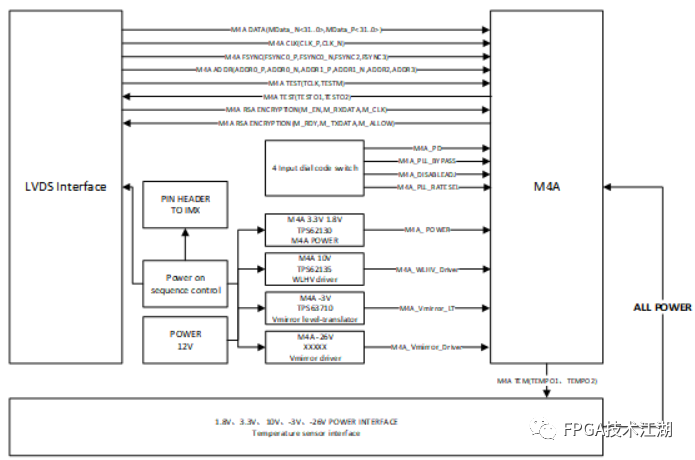

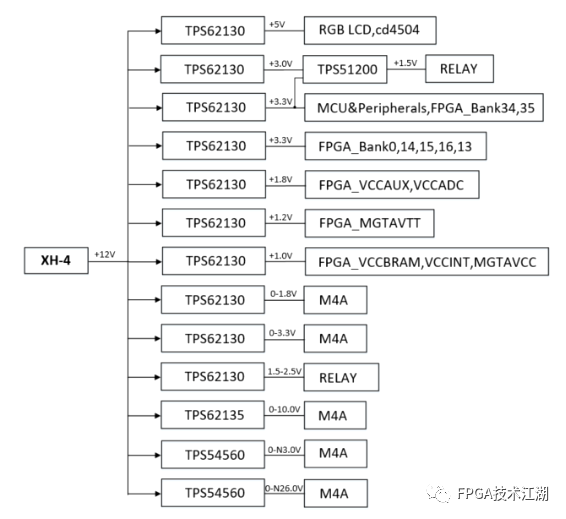

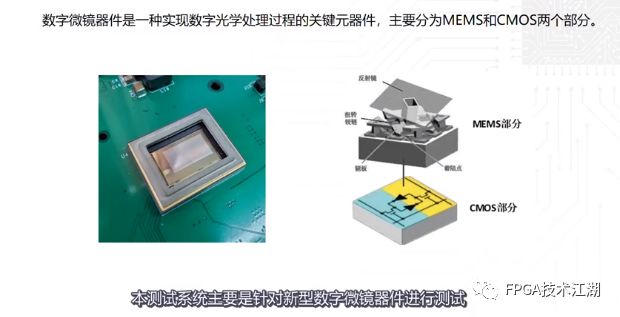

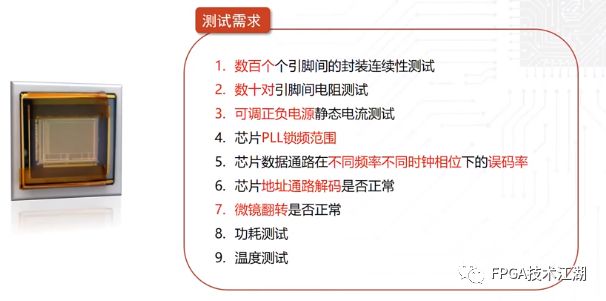

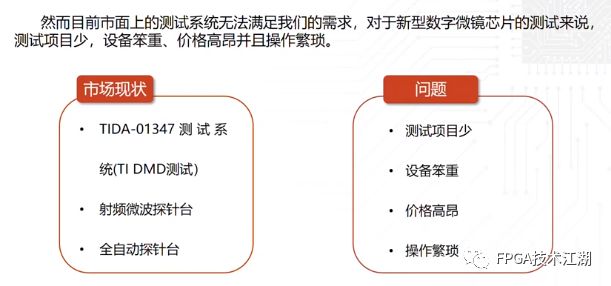

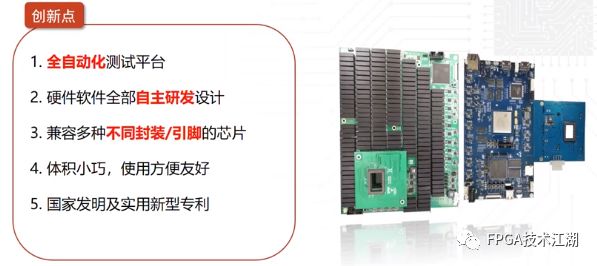

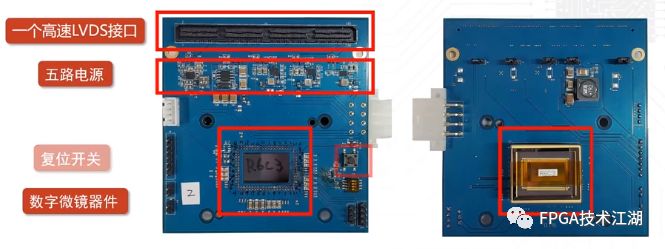

2014年,国务院印发《国家集成电路产业发展推进纲要》,将集成电路发展上升为国家战略。在集成电路产业蓬勃发展的同时,集成电路测试行业成为了不可缺少的一环。目前国内大多ICT企业,尤其是中小型企业依旧采用人工方法进行IC功能测试和性能测试。随着集成电路规模的增大与频率的提升,人工测试方法已经不能适应高速、集成化和小型化的电路结构。并且重复性的测试工作不仅提高了人工成本,也影响了IC生产测试的进度。本团队所在实验室与日本合作研发了一款新型数字微镜芯片,芯片制作存在着大量不确定因素,对于新制作的芯片,合作方对我们提出了基础性能测试以及功能性测试的要求。然而目前一些企业自主生产的测试仪器自动化程度低,测试性能不高,测试不全面且价格昂贵,并且市面上的测试设备很少针对专门芯片提供可定制化的测试平台。因此,本作品针对现有的技术不足,设计了一套新型数字微镜芯片(以下简称DMD芯片)测试系统,可以实现DMD芯片包括从前期的电气特性测试、芯片各部分功能测试和完全功能测试;满足了DMD芯片基础性能测试以及功能测试的需求,填补了国内相关领域内的技术空白,实现了完整的DMD芯片测试方案。电气特性测试包括芯片的封装连续性测试、芯片内端接电阻(ODT)测试以及静态电流测试;芯片各部分功能测试包括时钟测试、数据通道测试以及地址通路测试;完全功能测试包括DMD芯片整体的显示测试、工作时的动态电流测试以及工作温度检测。由于测试项目众多与测试操作复杂度高,本作品对测试方案进行了周密详实的设计,实现了全自动的芯片测试。整套系统采用双FPGA+ARM架构,使用经济的A7系列FPGA芯片控制DMD芯片的所有引脚进行电气特性测试;容量更大速度更快的ZYNQ 7000系列FPGA芯片对DMD芯片进行高速的功能性测试,并使用ARM Cortex-M7 内核的MCU作为系统控制器,完成对两片FPGA芯片的控制操作,从而实现DMD芯片的全方位测试。在此基础上,本作品的三部分测试包含了IC测试中的大部分项目,适用于多种IC测试的应用场景,拥有较好的普适性与可扩展性。基于FPGA芯片的测试系统因为其可编程的特性,拥有良好的可重构定制的能力,可以提供一个高性能的可定制化测试平台,多种接口可满足各类应用的开发需求,拥有广阔的应用前景,具有很大的现实意义。现今,DMD芯片在国内的生产少之又少,而芯片测试方面的产品就更加稀少。本作品为新型DMD芯片的测试提供全自动化测试平台,配合上位机操作界面,具有以下特点:本作品的硬件电路平台、FPGA软件、嵌入式软件、上位机界面均由本团队自主开发设计,没有借助任何现有模块。核心处理平台采用10层以及6层PCB叠层结构,保证了信号完整性、电源完整性及电磁兼容性,工作稳定、性能良好。整个软件系统完整、成熟、稳定性好,且系统的测试、调试程序、编程接口也非常完善,方便用户使用。★ 可兼容多种IC芯片测试,提供高性能、可定制化的测试平台本作品的三部测试包含了绝大部分IC测试中的测试项目,可以适用于多种IC测试,拥有极好的普适性及可扩展性。并且基于FPGA的测试系统拥有很好的可重构特性,可以根据不同的IC芯片做不同的测试需求,提供一个高性能的可定制化的测试平台,多种接口可满足各类应用的开发需求,拥有广阔的应用前景,具有很大的现实意义。本作品体积小巧,便于携带,配合操作界面,可在多种场景下如设计验证、产品检验以及现场维护等各个阶段进行芯片测试。本系统在上位机和触摸屏上均提供了友好的操作界面,便于用户进行实际使用。本作品已申请国家发明专利5项、实用新型专利5项、软件著作权2项。本测试系统的核心包括电气特性测试板以及功能性测试板。电气特性测试板主要以一块STM32F767的高性能ARM芯片作为系统控制芯片进行核心控制,一块A7系列FPGA作为继电器网络部分控制器,含有180个继电器分别用于控制电源上电,回路搭建,电流测量等等功能。同时包括WIFI模块、USB接口、温度传感接口等。功能性测试板板上资源非常丰富,主要以一片ZYNQ 7000系列高性能FPGA芯片为核心,一片Cortex-M7内核的MCU作为系统控制器,并搭载总容量为4Gbits的DDR3高速存储颗粒,最高数据传输速率高达1.8Gbps;拥有36对LVDS高速差分信号;一片SiI9616数字视频收发器;以及电源、复位电路、时钟、千兆网口、USB等其它外设接口,其系统框图如图3-2所示。电气特性测试板的功能有:负责和上位机进行信息互传;将上位机的控制信号发送给功能性测试板并接收来自该测试板的信息;完成对180余路继电器的开关控制;为DMD芯片提供所需要对的电源;实现对待测芯片所有管脚的单独控制。功能性测试板的功能有:通过串口与电气特性测试板通信;产生所需要得到单端与差分测试时钟;为DMD芯片提供驱动信号,进行数据通路以及地址通路的检测;驱动DMD芯片进行测试图案显示。本系统包括:一块电气特性测试板、一块IC转接板、一块功能性测试板、一块数字微镜子板、一台PC以及需要测试的DMD芯片(DMD),其具体结构示意图如图2-1所示,实物图如图2-2所示。PC与电气特性测试板上的ARM连接,通过串口访问控制系统,发送控制命令。电气特性测试板与功能性测试板也通过串口连接。当电气特性测试板就收到PC的控制命令后,分辨出是哪一种测试功能,若是电气特性测试则由电气特性测试板发送控制信号给DMD芯片进行电气特性测试;若是对于芯片部分功能性测试则将控制信号发送给功能性测试板,由功能性测试板接收信号后产生相应时序的控制信号传输给数字微镜子板进行对DMD芯片的功能测试;若是全部功能的测试,则由电气特性测试板以及功能性测试板共同对DMD芯片进行控制,完成测试内容。系统中自主研发的电气特性测试板如图2-3所示。整板以STM32F767型号ARM作为控制核心,一片Artix-7系列的FPGA作为继电器网络控制器。板上搭载180个继电器,通过控制继电器通断,最多形成1560种测试回路。板上还包括电流检测模块、WIFI模块、USB接口等。功能性测试板中如图2-4所示。整板以zynq 7000系列FPGA作为核心,一片Cortex-M7内核的MCU作为系统控制器,并搭载总容量为4Gbits的DDR3高速存储颗粒,最高数据传输速率高达1.8Gbps,板上还包括SII9616高清视频处理模块、LVDS高速信号接口、USB接口、HDMI视频输出模块、千兆网模块等。数字微镜子板如图2-5所示,包含有高速LVDS接口,拥有包括-26V、-3V、1.8V、3.3V以及10V五路电源以及DMD芯片插座,其系统结构图如图2-6所示。1.1固定电源测试

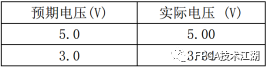

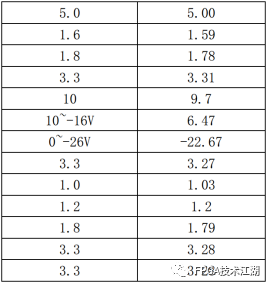

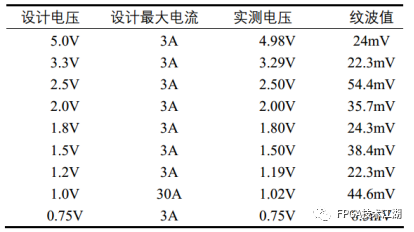

由于某些电源不是外接12V直接输入供电,而是通过板上先生成的电源为其供电的,所以我们将电源测试分为两部分。由12V直接输入后可以正常工作的电源芯片电压测试见表5-1所示。测试好上述表格中所列电源后,开始测试表5-2中电源,结果如表5-2所示。

1.2 可调电源测试

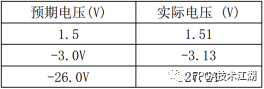

1.2.1两路可调负电源测试

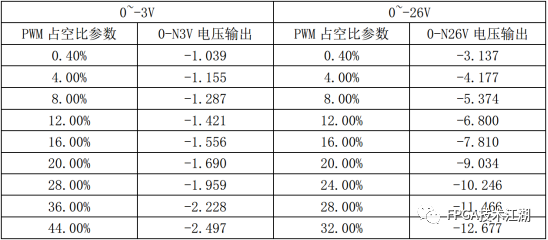

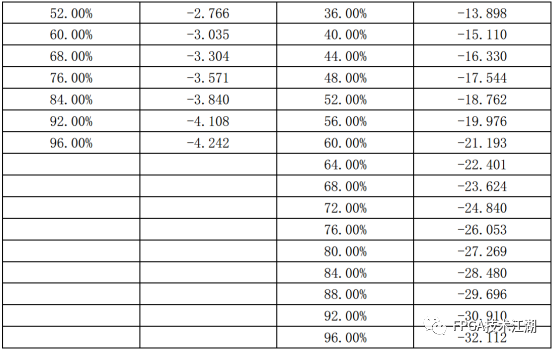

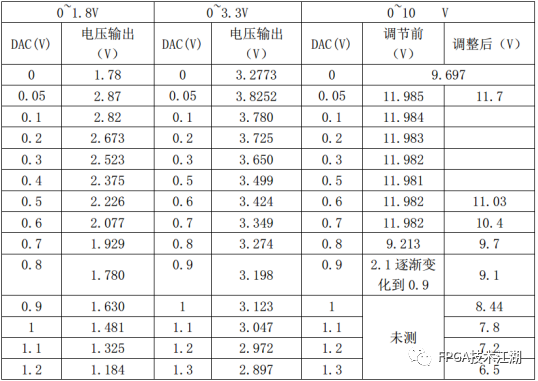

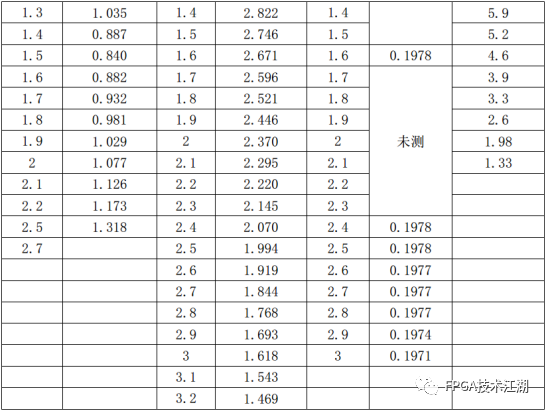

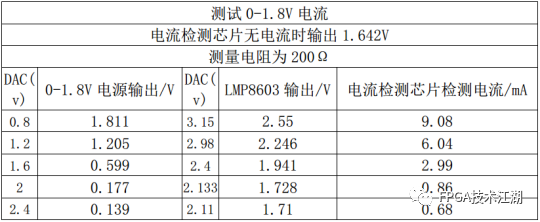

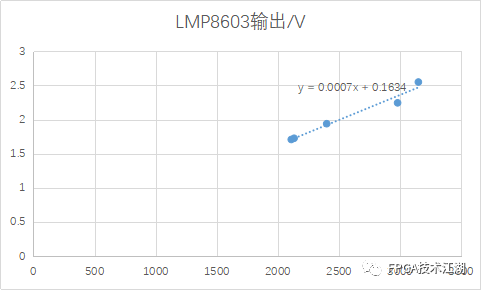

两路可调负电源0~-3V,0~-26V,其对应DAC将输出不能占空比的PWM波以改变电压值,测试记录如下表5-3所示:三路可调正电源0~1.8V,0~3.3V,0~10 V,其对应DAC输出不同参考电压,最可调整输出电压值大小,测试记录如下表所示, 其中0-10V电源,初始变化时可调变化区间极小且不稳定,后将1.33M,100k和10k分别更换为130k,10k和20k,可见右侧改变,有较好改观,可以实现功能。本系统中总共使用了180个12V供电继电器,通过所构建三级继电器网络中146个继电器间组合连接不同ESD二极管两端及LVDS间电阻。STM32烧入代码后与FPGA通信,控制其进行继电器网络的连接。每个继电器连通时都会亮起一个LED灯。调节测量继电器网络时先测试一个,仅烧录一个通路代码后,用万用表笔点通二极管两侧各通路,确认继电器是否正常工作构成合格通路后再进行全部继电器程序烧录,以防逻辑错误或其他错误。根据不同板的元件误差,标准电阻测试后进行软件校准。此处以0~1.8V为例,测试表格如下: 图5-2 0~1.8V电源对应电流检测芯片对应线性拟合2.1 电源测试

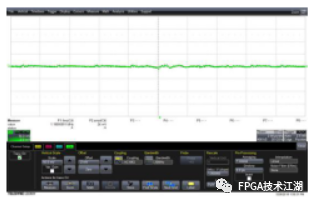

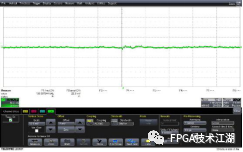

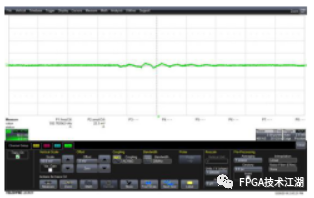

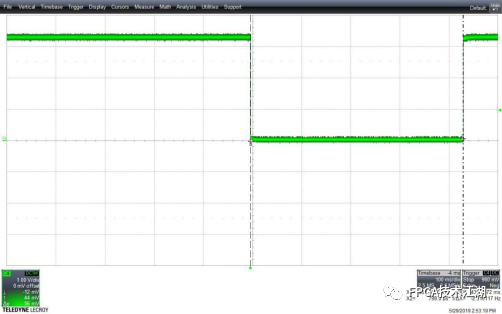

电源是系统能正常工作的基本保障,电源的任何不稳定都会导致整个系统的稳定性受到影响,严重情况下将无法正常工作。本作品使用外部的12V电源作为供电电源。板上采用分布式开关电源的方式为各类芯片进行供电,但是其纹波较大,在一些对电源纹波要求较高的部分我们采用了纹波小的LDO电源.两者在输出端都进行了仔细的滤波操作。根据预留测试点对各电压进行测试,测试结构如表5-1所示。从表中可以看到,各电压均正确且电源纹波均小于60mV,满足系统设计需求。 电压纹波波形如下图所示。2.2 全局信号测试

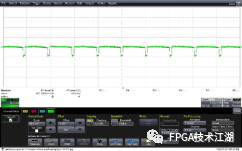

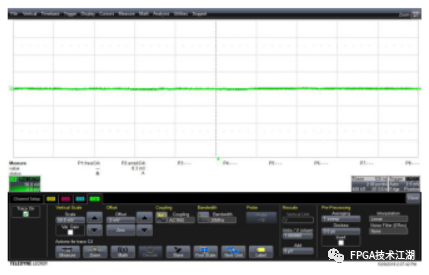

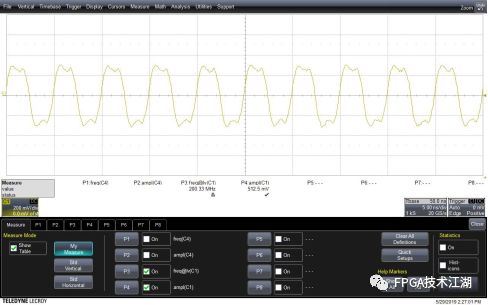

本测试板的时钟频率为:24M、25MHz、27MHz、32.768KHz、50MHz、33.333MHz和200MHz,若电路需要正常工作则必须对所有时钟信号进行测试。本测试板中FPGA的核心系统时钟为200M差分时钟,测试波形如图5-12所示。为保证电路系统能够正常复位,对复位信号进行测试可得如图5-13所示的波形,复位时间约为432.55ms,满足系统复位要求。图5-12 FPGA核心处理器200MHz差分系统时钟波形

2.3 DDR3信号测试

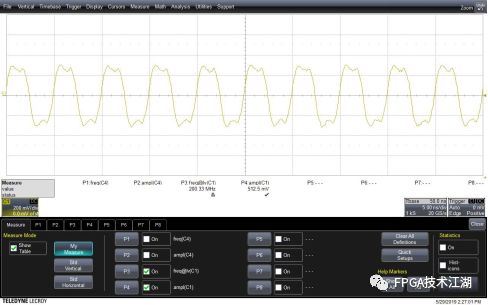

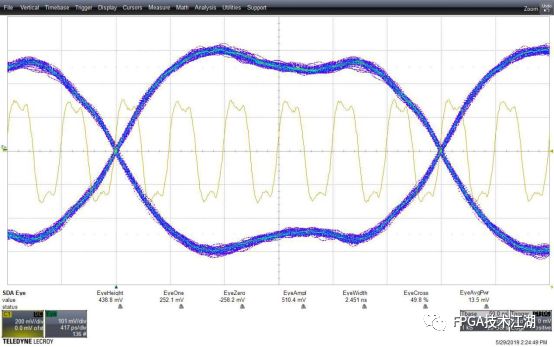

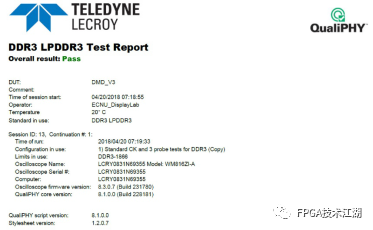

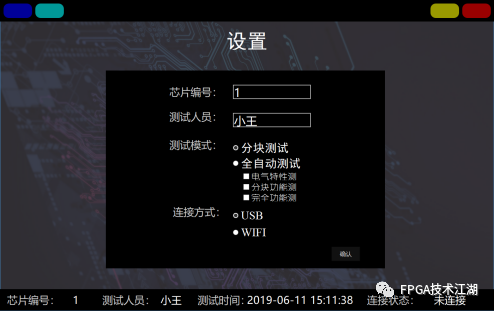

测试DDR3存储颗粒之前,要编写DDR3的驱动程序,对DDR3存储颗粒进行读写操作。发送生成的M序列,传输至DDR3,之后将数据从DDR3中读出后进行对比操作,查看DDR3读写的错误率。最后在示波器上测试DDR3的时钟信号、数据信号,确保信号完整性满足要求,其中时钟信号波形图及眼图分别如图5-14和图5-15所示。此时时钟的频率为200MHz,眼高眼宽等参数也能够满足设计要求[14]。最后使用LeCroy示波器中的专业测试工具对DDR3信号线进行测试,根据所生成的报告结果,可确定DDR3各项性能指标能够满足设计要求。系统完成后,需要对整体系统功能进行联调。系统的实物连接如下图所示:在设置界面,用户可设置芯片编号以及测试人员,如图5-19所示。

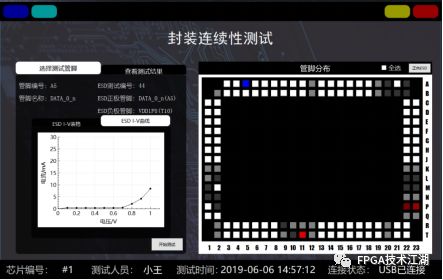

3.1 封装连续性测试

封装连续性测试界面如图5-20所示,用户首先在“管脚分布”栏中选中需要测试的管脚,然后点击“开始测试”按钮即可开始封装连续性测试,测试结果同时以表格与曲线两种形式进行显示。

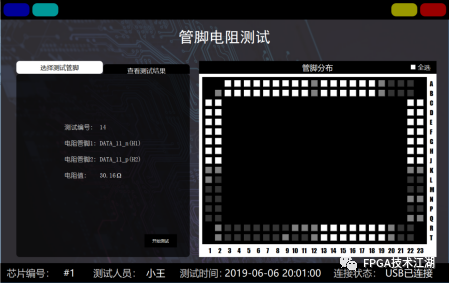

3.2 芯片内端接电阻(ODT)测试

芯片内端接电阻(ODT)测试界面如图5-21所示,用户首先在“管脚分布”栏中选中需要测试的管脚,然后点击“开始测试”按钮即可开始管脚间电阻测试,测试结果会在界面中进行显示。静态电流测试界面如图5-22所示,用户首先进行电压设置,然后在界面中点击“自动更新”即可显示各个电压的电流值。

5.3.4 时钟测试

时钟测试界面如图5-23所示,用户设置时钟频率和相位后即可完成时钟输出。

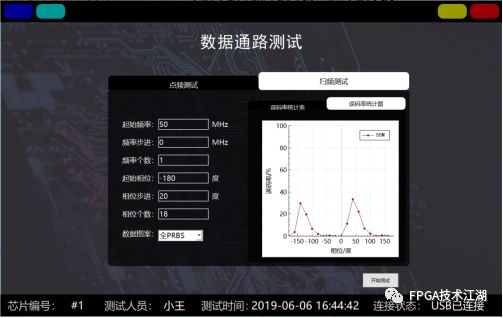

5.3.5 数据通路测试

数据通路测试界面如图5-24所示,用户在界面中输入时钟频率、时钟相位以及数据图案相关参数,误码率测试结果将以表格和曲线两种方式显示。

5.3.6 地址通路测试

地址通路测试界面如图5-25所示,用户在界面中填入起始地址与终止地址,测试结果会在文本框中显示。

5.3.7 MEMS测试

MEMS测试界面如图5-26所示,用户在下拉菜单中选择显示图案,即可使被测DMD芯片显示对应图案。

5.3.8 动态电流测试

动态电流测试界面如图5-27所示,用户首先进行电压设置,然后在界面中点击“自动更新”即可显示各个电压的电流值。

5.3.9 温度测试

温度测试界面如图5-28所示,点击“自动更新”后,被测芯片温度会实时显示在界面上。后续会持续更新,带来Vivado、 ISE、Quartus II 、candence等安装相关设计教程,学习资源、项目资源、好文推荐等,希望大侠持续关注。- THE END -

🍁

【免费】FPGA工程师人才招聘平台

FPGA人才招聘,企业HR,看过来!

系统设计精选 | 基于FPGA的实时图像边缘检测系统设计(附代码)

基于原语的千兆以太网RGMII接口设计

时序分析理论和timequest使用_中文电子版

求职面试 | FPGA或IC面试题最新汇总篇

资料汇总|FPGA软件安装包、书籍、源码、技术文档…(2024.01.06更新)

FPGA就业班,05.04开班,新增课程内容不加价,高薪就业,线上线下同步!

FPGA技术江湖广发江湖帖

无广告纯净模式,给技术交流一片净土,从初学小白到行业精英业界大佬等,从军工领域到民用企业等,从通信、图像处理到人工智能等各个方向应有尽有,QQ微信双选,FPGA技术江湖打造最纯净最专业的技术交流学习平台。

FPGA技术江湖微信交流群

加群主微信,备注姓名+学校/公司+专业/岗位进群

FPGA技术江湖QQ交流群

备注姓名+学校/公司+专业/岗位进群