点击上方名片关注了解更多

点击上方名片关注了解更多

时钟抖动技术广泛适应各类周期性脉冲信号,如电学电子设备PWM电压及数字电路时钟信号等。此类周期性脉冲信号对电路设计构成强大干扰,故须慎重对待。

近期,时钟抖动技术作为有效减少周期性脉冲电路电磁干扰的手段备受关注。其运作机制源于傅立叶变换。

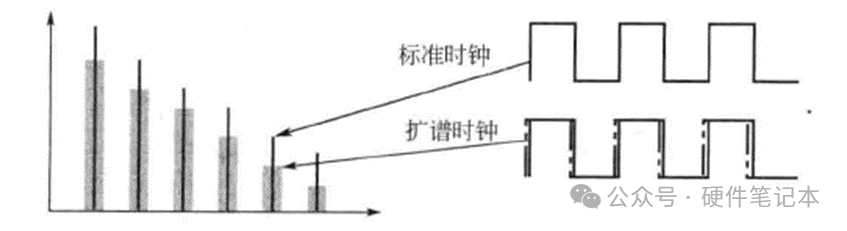

脉冲信号经傅里叶变换后,周期性信号呈现出离散谱线特征,其能量相对集中于该谱线上的对应频率;反之,无周期性脉冲的频谱为连续形式,能量均匀分散于全部频率之中。对于时钟抖动技术,这是一种对于时钟电路的运用,旨在让时钟频率产生微小变化,进而令时钟信号的谱线加宽且峰值减小,如图所示的结果示例。

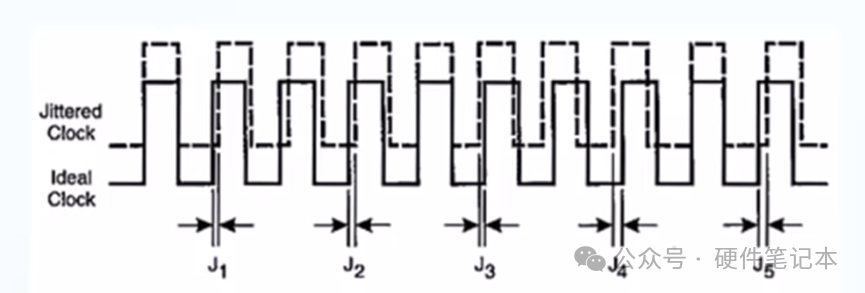

图 理想时钟信号和抖动时钟信号

图 理想时钟信号和抖动时钟信号

图 时钟抖动的概念

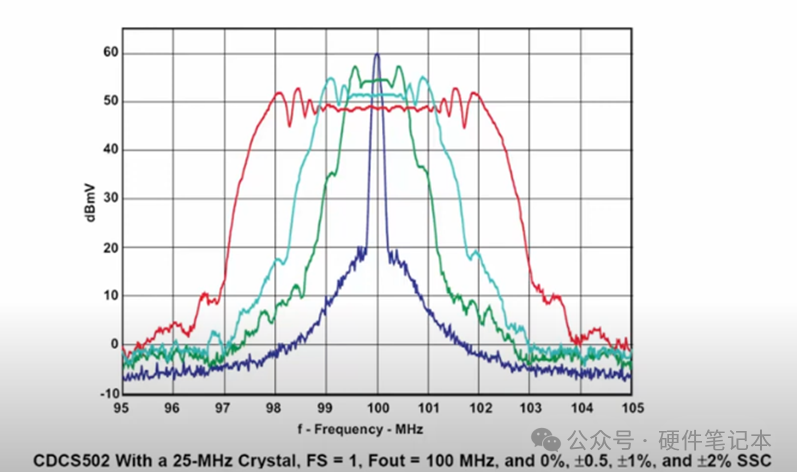

图 不同时钟抖动频率某一谐波频率附近的能量分布

时钟抖动可有效降低电子产品的EMI,其原理在于将高频谐波能量分散至更广泛的频段,产生更宽的时钟谱线。在对设备进行电磁兼容性检测,例如RE102测试时,频率宽度相对狭窄的测试接收机会有部分能量超出接收范围,令被测设备得以顺利通过电磁兼容试验。此项技术尤其适用于商用设备,因其通常缺乏完备的屏蔽与滤波措施。而军用设备需满足更为严苛的标准,因此扩谱时钟的效果并不明显,主要依赖于屏蔽与滤波。

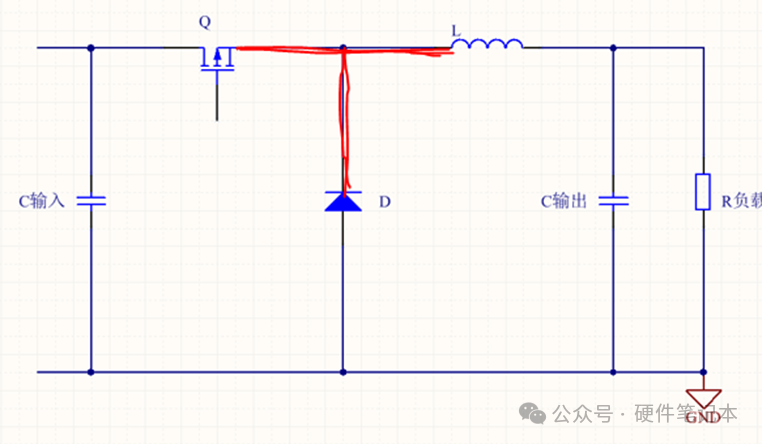

扩谱时钟的理念不仅限于数字电路领域,还可应用于其他脉冲电路,如开关电源中的频率调制PWM脉冲信号,有助于降低干扰辐射。以开关电源中的BUCK电路为例,若驱动Q1通断的PWM信号采用扩谱时钟,则红色共模电压区域的电压波形亦会出现抖动现象,进而导致共模电压谐波能量谱线变宽,峰值降低,从而降低了开关电源各谐波频率下的EMI水平。

图 开关电源BUCK电路

硬件工程师及从业者都在关注我们

声明:

推荐阅读▼

电路设计-电路分析

EMC相关文章

电子元器件

后台回复“加群”,管理员拉你加入同行技术交流群。