FPGA的全称为Field Programmable Gate Array,即现场可编程门阵列,属于可编程逻辑器件,其中,基本可编程逻辑单元是可编程逻辑的主体,可以根据设计灵活地改变其内部连接与配置,完成不同的逻辑功能。FPGA的基本可编程逻辑单元一般都采用了基于SRAM的查找表结构,查找表(LUT,Look Up Table)一般为四输入,用于完成组合逻辑功能。

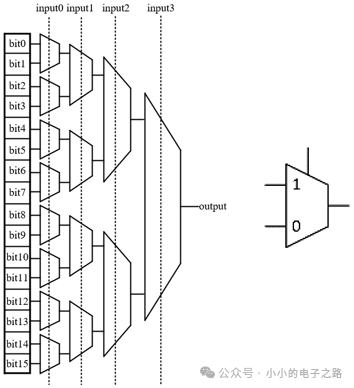

下图是四输入查找表的基本结构,核心元件为二选一多路选择器,四个输入通过控制二选一多路选择器的状态实现所需结果的输出。

接下来通过一个简单的运算来演示一下FPGA是如何利用LUT实现组合逻辑功能的。假设需要实现的组合逻辑功能为A&B&C&D,该逻辑功能的实现可分为三步,分别是求解真值表、数据下载、数据输出。

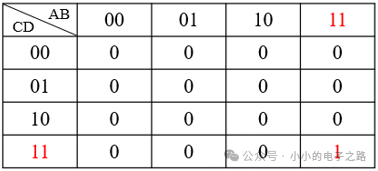

1、求解真值表

在代码编译的过程中,FPGA会根据所需实现的逻辑功能求解出对应的真值表。

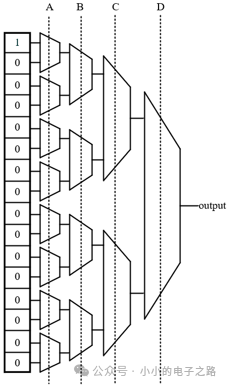

2、数据下载

在代码下载的过程中,真值表中的数据会下载至LUT对应的SRAM中。

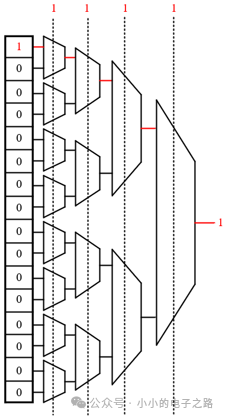

3、数据输出

在代码运行的过程中,四个输入通过控制二选一多路选择器的选通状态来输出不同的数据。

在本例中,当且仅当四个输入A、B、C、D均为1时,LUT才会输出bit0中的数据,即输出1,在其它输入组合下,LUT会输出其它位的数据,但都为0,实现了A&B&C&D的组合逻辑功能。