点击蓝字,关注我们

一个有温度的硬件工程师-文末有惊喜

“大丈夫生当如此,一往无前。”—《霍元甲》

前言

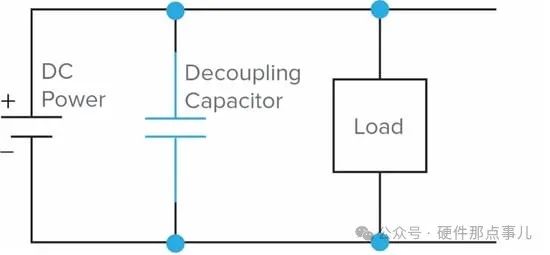

关于电容,经常听到的一个名词就是“去耦”,也有听过“旁路”的说法,个人觉得没必要太纠结这两个的区别,简单点来说,去耦侧重于既隔离开电源->IC的干扰,又隔离开IC->电源的干扰,旁路主要侧重隔离开电源->IC的干扰。

关于去耦电容容值的问题,很多硬件工程师常说无脑放100nF就够了,没出过问题,仿佛100nF去耦电容成了万能药,原因其实是当电路的时钟速度较低或者电路的噪声容限较高时,对去耦电路的要求不高所以一般不会出问题。然而,当涉及到具有高时钟速度、产生大量噪声或对噪声非常敏感的集成电路(IC)时,IC自身会对电源线上的波动更为敏感,或者它们自身可能会产生更多的噪声,此时去耦电路的设计选型就需要慎重。

这种更复杂的去耦电路可能包括多个不同类型和大小的旁路电容器,以及其他的滤波器和电源噪声抑制技术。设计这样的去耦电路需要考虑到IC的工作特性、电源线上的噪声频谱以及电路的布局和连接方式等因素,以确保有效地降低噪声并提供稳定的电源给IC。

实例分析

1.确定芯片的最大瞬态电流

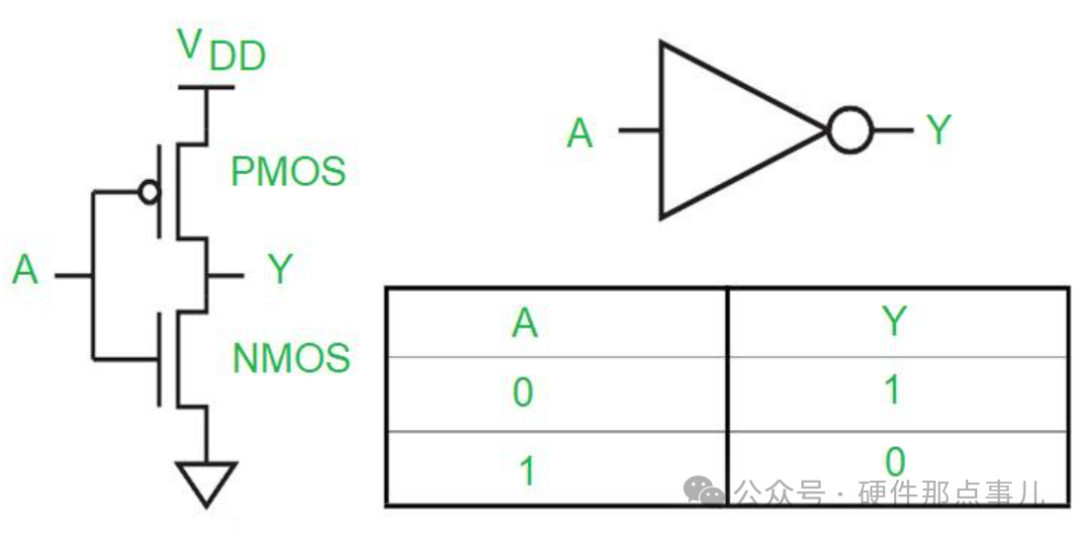

基于C-MOS的数字IC里面会有很多门电路,当这些门电路在进行开或关切换时,MOS的栅极会有电流充放电,VDD和GND之间也会存在短暂的直通电流,电流急剧变化会造成电源电压变化,因此首先要确定芯片的最大瞬态电流。

但是大家肯定发现了,一般IC手册里不给这个参数啊,那咋办?大公司的硬件工程师这个时候可以找原厂去要,小公司的硬件工程师那就只能估算了,手册中一般会给出芯片工作的最大电流,这个最大电流里有多少是瞬态电流呢?我们不知道,那就常规做法按50%去估计。

2.评估被去耦IC能接受的电源电压波动容限,也就是电压纹波

也就是你选的这款IC如果是3.3V电压供电,它能接受多少的电压波动能够稳定工作呢?需要查阅对应的IC手册,需要注意的是如果某个IC允许10%的电压波动,导致电压波动的因素会有很多,比如稳压电源的精度3%,噪声2%。所以你得把这些都减掉,剩下5%的才是留给瞬态电流导致的电压纹波的。

3.基于芯片的最大瞬态电流和电源电压波动容限计算电源网络的阻抗的上限值

Z=ΔV/I,Z是我们的设计目标阻抗。

4.确定去耦的频率范围

板级电源分配网络设计的频率范围约从100kHz到100MHz,不同的产品需求不一样,需要根据自己的需求来定。或者你可以根据自己产品的MCU时钟频率来估算也可以,也就是5倍的时钟频率,为什么是5倍呢?这里不展开了,篇幅太多,以后讲到高速再细说,感兴趣的老铁可以自己先查查。

5.基于以下公式计算电容容值

C=1/2*π*f*Z

6.基于回路中的等效电感校核当前选型的电容是否符合

实例说明

IC是3.3V供电,设计可接受的瞬态电流导致的电压纹波5%,最大瞬态电流100mA,去耦的频率范围100kHz~100MHz。

1. 首先计算一下目标阻抗:

Z=3.3*5%/0.1=1.65Ω

2. 100kHz时,目标阻抗计算对应的电容容值如下:

C=1/2*3.14*100*1.65≈1uF

3. 1uF的电容够了吗?够不够得通过计算来说明

因为电容在充当去耦的角色时,电容到IC之间会有走线,过孔,再叠加电容自身的ESL,从而影响电容的等效谐振频率点,电容自身的ESL可以通过手册查,板上走线的等效电感,过孔的等效电感都应对应的计算公式,这里也不展开了,通过以上分析我们可以计算得到电感到IC之间的环路电感L,假定是1nH,那么我们就能计算得到这个电容能起作用的最大有效频率点:

f=1.65Ω/2*3.14*1nH≈262MHz

这就说明了目前的设计是可以满足要求的,当然了如果计算出来的f小于100MHz,那么我们就需要采用并联电容的方法,通过减小ESL来提高f。

重

要

通

知