今天给大侠带来基于FPGA的数字电压表设计,附源码,获取源码,请在“FPGA技术江湖”公众号内回复“数字电压表设计源码”,可获取源码文件。话不多说,上货。

模数转换器,又称A/D转换器,简称ADC,通常是指一个将模拟信号转换为抗干扰性更强的数字信号的电子器件。一般的ADC是将一个输入电压信号转换为一个输出的数字信号。由于数字信号本身不具有实际意义,仅仅表示一个相对大小,故任何一个ADC都需要一个参考模拟量作为转换标准。比较常见的参考标准为最大的可转换信号大小,而输出的数字量则表示输入信号相对于参考信号的大小。本设计则通过对模数转换芯片(TLC549)的采样控制,实现一个简易的数字电压表。

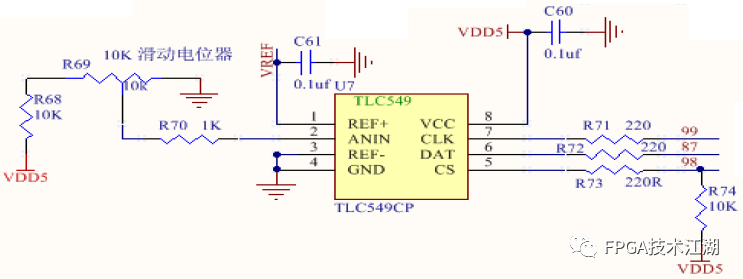

TLC549典型的配置电路如下图所示:

TLC549的端口描述如下:

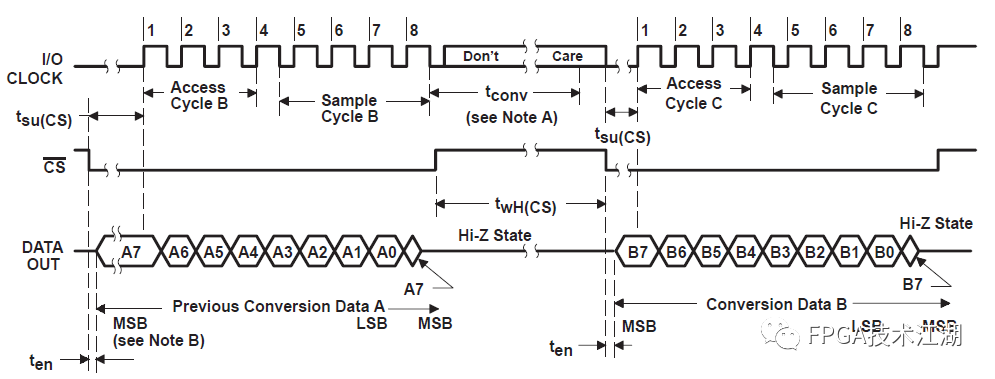

TLC549是一个8位的串行模数转换器,A/D转换时间最大为17us,最大转换速率为4MHz。下图为TLC549的访问时序,从图中可以看出,TLC549的使用只需对外接输入输出时钟(I/O CLK)和芯片选择(/CS)、输入的模拟信号(ANALOG IN)的控制。

分析时序图可知:当片选信号(/CS)拉低时,ADC前一次的转换数据(A)的最高位A7立即出现在数据线DATA OUT上,之后的数据在时钟I/O CLOCK的下降沿改变,可在I/O CLOCK的上升沿读取数据。转换时,/CS要置为高电平。在设计操作时,要注意Tsu(CS)、Tconv、Twh(CS)和I/O CLOCK的频率这几个参数。Tsu(CS)为CS拉低到I/O CLOCK第一个时钟到来的时间,至少要1.4us;Twh(CS)为ADC的转换时钟,不超过17us,Tconv的值也不超过17us;I/O CLOCK为 1.1MHz。其他参数可参考数据手册。

由于ADC是8位的,所以采样的电压值为:

V =(D*Vref)/256

其中V为采样的电压值;D为ADC转换后读取的8位二进制数;Vref为参考电压值,此处为2.5V。

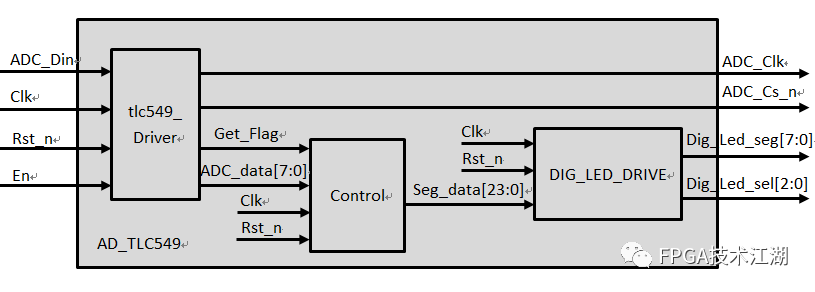

本设计通过调节电位器RW1改变ADC的模拟输入值,数据采样读取后由数码管显示,最后用万用表测量输入电压,并与读取在数码管上的数据(单位为mV)作比较。设计的架构图如下:

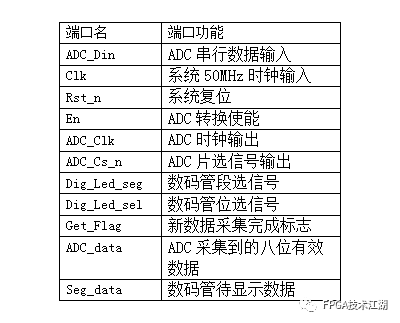

设计架构图对应端口的功能描述表:

tlc549_Driver模块采用序列机实现接口访问时序,并且产生1MHz的ADC_Clk和采集到ADC_data;Control模块,将采集到的ADC数据(ADC_data)换算成对应的电压值,并经过二进制到BCD转换以后传送到数码管;DIG_LED_DRIVE模块负责数码管的驱动,将传递过来的数据显示出来。

AD_TLC549顶层模块代码:

module AD_TLC549(Clk,Rst_n,ADC_Din,ADC_Clk,ADC_Cs_n,Dig_Led_sel,Dig_Led_seg);input Clk;input Rst_n;input ADC_Din;output ADC_Clk;output ADC_Cs_n;output [2:0]Dig_Led_sel;output [7:0]Dig_Led_seg;wire Get_Flag;wire [7:0]ADC_data;wire [23:0]seg_data;tlc549_Driver tlc549_Driver(.Clk(Clk),.Rst_n(Rst_n),.En(1'b1),.ADC_Din(ADC_Din),.ADC_Clk(ADC_Clk),.ADC_Cs_n(ADC_Cs_n),.Data(ADC_data),.Get_Flag(Get_Flag));Control Control(.Clk(Clk),.Rst_n(Rst_n),.Get_Flag(Get_Flag),.ADC_data(ADC_data),.seg_data(seg_data));DIG_LED_DRIVE DIG_LED_DRIVE(.Clk(Clk),.Rst_n(Rst_n),.Data(seg_data),.Dig_Led_seg(Dig_Led_seg),.Dig_Led_sel(Dig_Led_sel));endmodule

tlc549_Driver模块代码:

module tlc549_Driver (Clk,Rst_n,En,ADC_Din,ADC_Clk,ADC_Cs_n,Data,Get_Flag);input Clk; //系统50MHz时钟输入input Rst_n;//全局复位input En; //ADC转换使能,高电平有效input ADC_Din;//ADC串行数据输入output reg ADC_Clk; //ADC时钟信号输出output reg ADC_Cs_n;//ADC片选信号输出output reg Get_Flag;//数据转换完成标志output reg [7:0] Data;//ADC转换以后的电压值reg [10:0] Cnt1; //系统时钟计数器reg [7:0] data_tmp;//数据寄存器//系统时钟上升沿计数always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)Cnt1 <= 11'd0;else if(!En)Cnt1 <= 11'd0;else if(Cnt1 == 11'd1310)Cnt1 <= 11'd0;elseCnt1 <= Cnt1 + 1'b1;endalways@(posedge Clk or negedge Rst_n)beginif(!Rst_n)beginADC_Clk <= 1'b0;ADC_Cs_n <= 1'b1;data_tmp <= 8'd0;Data <= 8'd0;endelse if(En)begincase(Cnt1)1 : ADC_Cs_n <= 1'b0; //1~71(Tsu)71 : begin ADC_Clk <= 1; data_tmp[7] <= ADC_Din;end96 : ADC_Clk <= 0;121 : begin ADC_Clk <= 1; data_tmp[6] <= ADC_Din;end146 : ADC_Clk <= 0;171 : begin ADC_Clk <= 1; data_tmp[5] <= ADC_Din;end196 : ADC_Clk <= 0;221 : begin ADC_Clk <= 1; data_tmp[4] <= ADC_Din;end246 : ADC_Clk <= 0;271 : begin ADC_Clk <= 1; data_tmp[3] <= ADC_Din;end296 : ADC_Clk <= 0;321 : begin ADC_Clk <= 1; data_tmp[2] <= ADC_Din;end346 : ADC_Clk <= 0;371 : begin ADC_Clk <= 1; data_tmp[1] <= ADC_Din;end396 : ADC_Clk <= 0;421 : begin ADC_Clk <= 1; data_tmp[0] <= ADC_Din;end446 : begin ADC_Clk <= 0; ADC_Cs_n <= 1'b1; Get_Flag<=1;end447 : begin Data <= data_tmp; Get_Flag<=0; end //447~1310(Twh)1310: ;default:;endcaseendelsebeginADC_Cs_n <= 1'b1;ADC_Clk <= 1'b0;endendendmodule

module Control(Clk,Rst_n,Get_Flag,ADC_data,seg_data);input Clk;//系统时钟输入input Rst_n;//系统复位input Get_Flag;//ADC采集数据完成标志input [7:0]ADC_data;//ADC采集数据输入output reg [23:0]seg_data;//数码管待显示数据reg [3:0]qianwei; //千位reg [3:0]baiwei; //百位reg [3:0]shiwei; //十位reg [3:0]gewei; //个位reg [15:0]tenvalue;//采样的电压值//采集电压值计算always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)tenvalue<=0;else if(Get_Flag)//新的数据采集完成,可以进行计算tenvalue<=(ADC_data*100*25)/256;end//二进制转BCD值always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)beginqianwei<=0;baiwei<=0;shiwei<=0;gewei<=0;endelsebeginqianwei<=tenvalue/1000; //2baiwei<=(tenvalue/100)%10; //5shiwei<=(tenvalue/10)%10; //0gewei<=tenvalue%10; //0endend//数码管显示数值always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)seg_data<=0;elseseg_data<={qianwei, //千位baiwei, //百位shiwei, //十位gewei, //个位8'hFF //空闲};endendmodule

/*数码管扫描模块,位选为外部74hc138译码器进行控制*//*仿真时请将本文件设置为顶层,并在代码中根据相应注释中的内容选择cnt1_MAX = 24*/module DIG_LED_DRIVE(Clk,Rst_n,Data,Dig_Led_seg,Dig_Led_sel);input Clk; //系统时钟输入input Rst_n; //系统复位input [23:0]Data;//待显示数据output [7:0]Dig_Led_seg;//数码管段选output [2:0]Dig_Led_sel;//数码管位选parameter system_clk = 50_000_000;localparam cnt1_MAX = 24;/*仿真的时候使用,板级验证时请注释掉*///localparam cnt1_MAX = system_clk/1000/2-1;/*板级验证的时候使用,仿真时请注释掉*/reg [14 :0] cnt1; //分频计数器reg clk_1K; //扫描时钟,1KHzreg [2:0]sel_r; //数码管位选reg [7:0]seg_r; //数码管段选reg [3:0]disp_data; //单位显示数据缓存//1KHz时钟分频计数器always@(posedge Clk)beginif(!Rst_n)cnt1<=0;else if(cnt1==cnt1_MAX)cnt1<=0;else cnt1<=cnt1+1'b1;end//得到1KHz时钟always@(posedge Clk or negedge Rst_n)beginif(!Rst_n)clk_1K<=0;else if(cnt1==cnt1_MAX)clk_1K<=~clk_1K;end//位选信号控制always@(posedge clk_1K or negedge Rst_n)beginif(!Rst_n)sel_r<=3'd0;else if(sel_r == 3'd3)sel_r<=3'd0;elsesel_r<=sel_r+1'b1;end//根据不同的数码管位选择不同的待显示数据always@(*)beginif(!Rst_n)disp_data=4'd0;elsebegincase(sel_r)3'd0:disp_data=Data[23:20];3'd1:disp_data=Data[19:16];3'd2:disp_data=Data[15:12];3'd3:disp_data=Data[11:8];3'd4:disp_data=Data[7:4];3'd5:disp_data=Data[3:0];default :disp_data=4'd0;endcaseendend//数据译码,将待显示数据翻译为符合数码管显示的编码always@(*)beginif(!Rst_n)seg_r=8'hff;elsebegincase(disp_data)4'd0: seg_r=8'hc0;4'd1: seg_r=8'hf9;4'd2: seg_r=8'ha4;4'd3: seg_r=8'hb0;4'd4: seg_r=8'h99;4'd5: seg_r=8'h92;4'd6: seg_r=8'h82;4'd7: seg_r=8'hf8;4'd8: seg_r=8'h80;4'd9: seg_r=8'h90;4'd10: seg_r=8'h88;4'd11: seg_r=8'h83;4'd12: seg_r=8'hc6;4'd13: seg_r=8'ha1;4'd14: seg_r=8'h86;4'd15: seg_r=8'h8e;default : seg_r=8'hff;endcaseendendassign Dig_Led_seg = seg_r;assign Dig_Led_sel = sel_r;endmodule

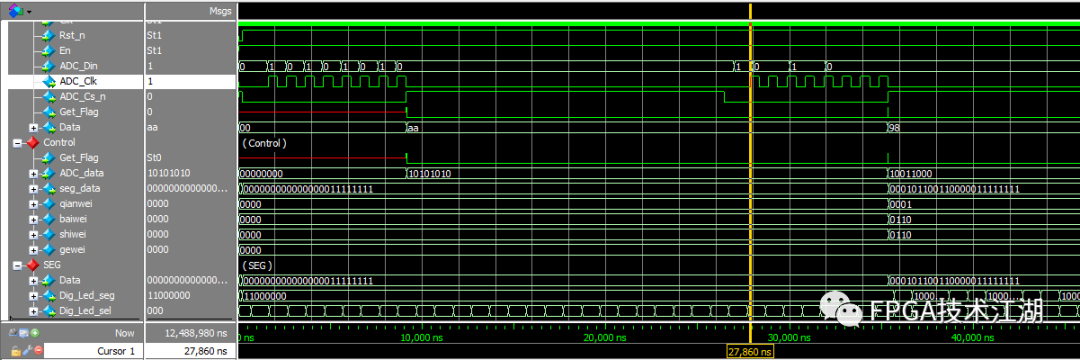

`timescale 1ns/1psmodule AD_TLC549_tb;reg Clk;reg Rst_n;reg ADC_Din;wire ADC_Clk;wire ADC_Cs_n;wire [2:0] Dig_Led_sel;wire [7:0] Dig_Led_seg;initial beginClk = 1;Rst_n = 0;ADC_Din = 0;#200.1Rst_n = 1;#1400 ADC_Din=1; //aa#1000 ADC_Din=0;#1000 ADC_Din=1;#1000 ADC_Din=0;#1000 ADC_Din=1;#1000 ADC_Din=0;#1000 ADC_Din=1;#1000 ADC_Din=0;#17000#1400 ADC_Din=1; //98#1000 ADC_Din=0;#1000 ADC_Din=0;#1000 ADC_Din=1;#1000 ADC_Din=1;#1000 ADC_Din=0;#1000 ADC_Din=0;#1000 ADC_Din=0;//#20000 $stop;endAD_TLC549 AD_TLC549_dut(.Clk(Clk),.Rst_n(Rst_n),.ADC_Din(ADC_Din),.ADC_Clk(ADC_Clk),.ADC_Cs_n(ADC_Cs_n),.Dig_Led_sel(Dig_Led_sel),.Dig_Led_seg(Dig_Led_seg));always #10 Clk = ~Clk;endmodule

- THE END -

往期精选

FPGA技术江湖广发江湖帖

无广告纯净模式,给技术交流一片净土,从初学小白到行业精英业界大佬等,从军工领域到民用企业等,从通信、图像处理到人工智能等各个方向应有尽有,QQ微信双选,FPGA技术江湖打造最纯净最专业的技术交流学习平台。

FPGA技术江湖微信交流群

加群主微信,备注姓名+学校/公司+专业/岗位进群

FPGA技术江湖QQ交流群

备注姓名+学校/公司+专业/岗位进群