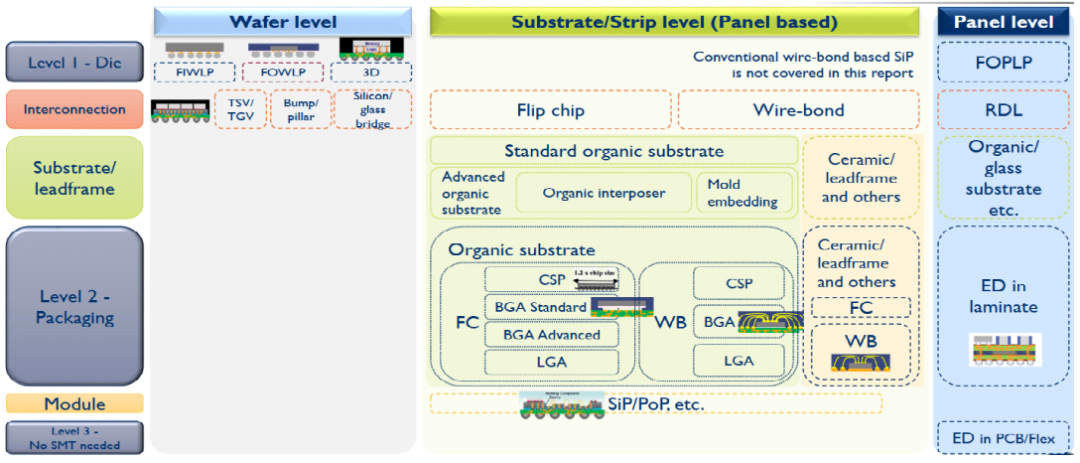

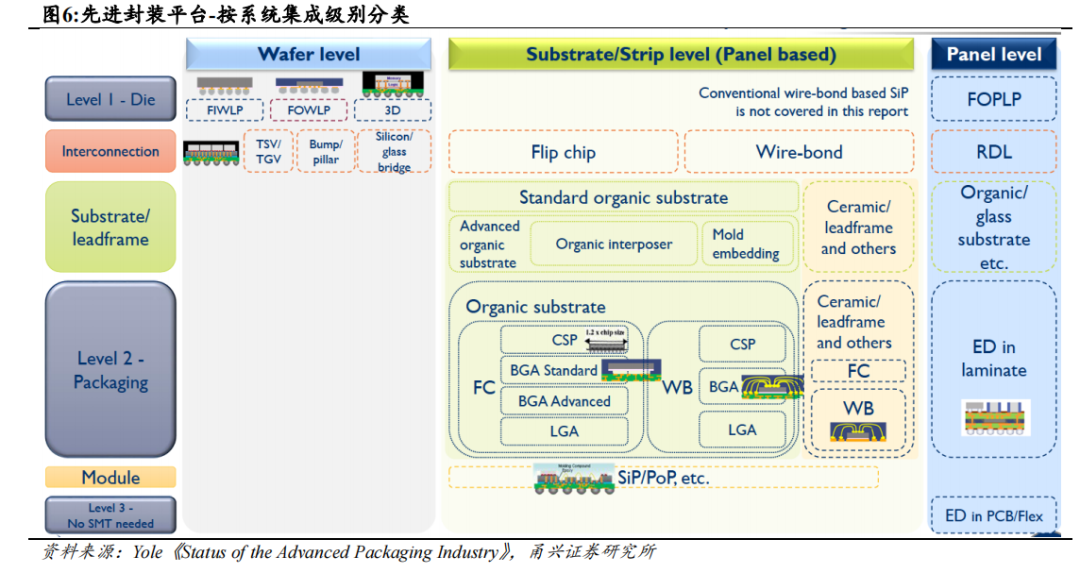

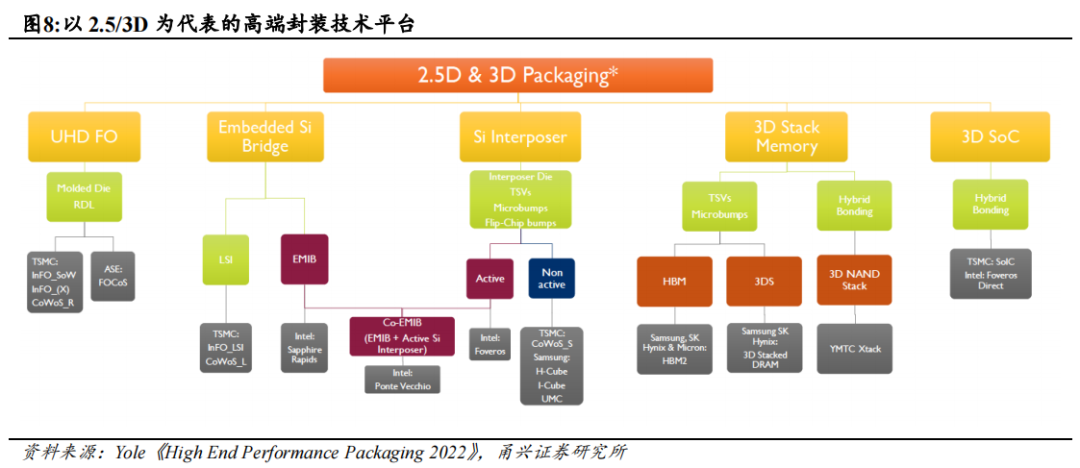

本文来自“人工智能系列专题报告:CoWoS技术引领先进封装,国内OSAT有望受益”。芯片封装由 2D 向 3D 发展,衍生出多种不同的封装技术。在封装技术不断升级迭代的过程中,出现了系统级封装(SiP)等新的封装方式。技术实现的方法包括 2.5D 封装(Interposer、RDL)、3D 封装(TSV)、倒装 FC(Flip Chip)、凸块(Bumping)、晶圆级封装 WLP(Wafer Level Package)、CoWoS (Chip onWafer on Substrate)、InFO (Integrated Fan-Out)、EMIB等先进封装技术。

香山:开源高性能RISC-V处理器

AI算力研究:英伟达B200再创算力奇迹,液冷、光模块持续革新

GPU深度报告:英伟达GB200 NVL72全互联技术,铜缆方案或将成为未来趋势?

人工智能系列专题报告:CoWoS技术引领先进封装,国内OSAT有望受益

软硬件融合:从DPU到超异构计算

《大模型技术能力测评合集》

1、大模型时代,智算网络性能评测挑战

2、AIGC通用大模型产品测评篇(2023)

3、人工智能大模型工业应用准确性测评

4、甲子星空坐标系:AIGC通用大模型产品测评篇

5、AIGC通用大模型产品测评篇(2023)

6、2023年中国大模型行研能力评测

1、新型智算中心算力池化技术白皮书 2、智算中心网络架构白皮书 3、面向AI大模型的智算中心网络演进白皮书 4、智算赋能算网新应用白皮书

14份半导体“AI的iPhone时刻”深度系列报告合集

12份走进“芯”时代系列深度报告合集

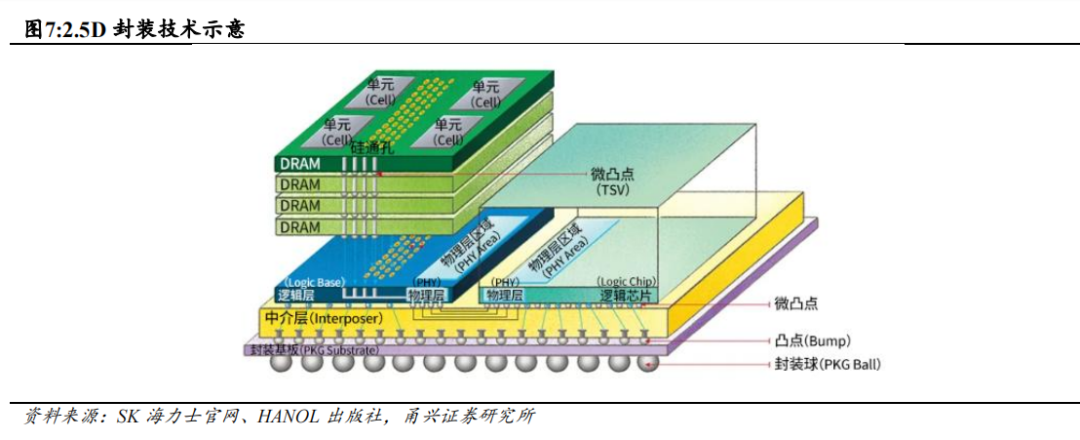

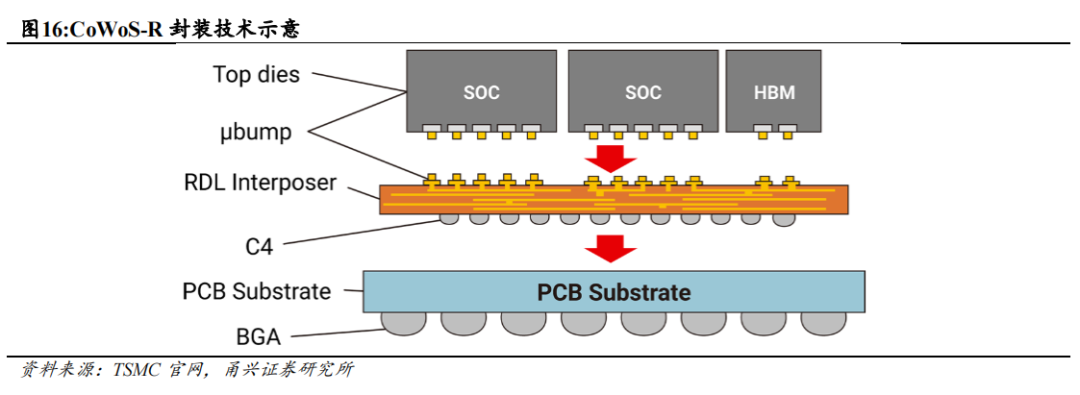

2.5D 封装是一种先进的异构芯片封装,具备低成本、高性能和可靠性等优势。根据电子工程专辑,在 2.5D 封装中,芯片被并排放置在中介层(interposer)的顶部,通过芯片上微小凸块(uBump)和中介层内的布线来实现彼此之间的互连。中介层通过硅通孔(TSV)来实现不同层之间的互连,然后通过锡球(C4)焊接到传统 2D 封装基板上。这种设计架构提供了更高的集成度和性能,允许多个芯片之间的高速数据传输和资源共享,从而实现了更强大的计算能力和更高效的能源利用。

2.5D 封装发展迅速,CoWoS 有望引领先进封装

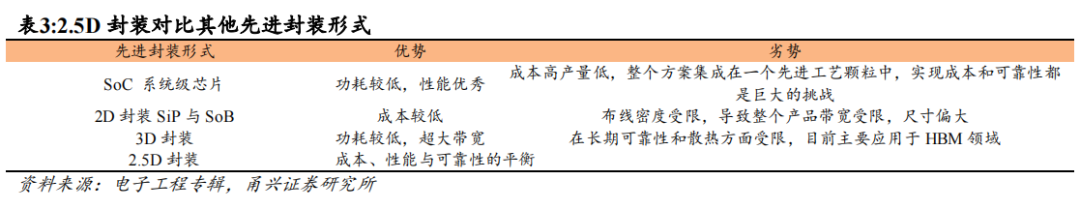

芯片封装由 2D 向 3D 发展的过程中,衍生出多种不同的封装技术。其中,2.5D 封装是一种先进的异构芯片封装,可以实现从成本、性能到可靠性的完美平衡。目前英伟达的算力芯片采用的是台积电的 CoWoS 方案,这是一项 2.5D 多芯片封装技术,该方案具备提供更高的存储容量和带宽的优势,适用于处理存储密集型任务,如深度学习、5G 网络、节能的数据中心等。目前 CoWoS 封装技术已经成为了众多国际算力芯片厂商的首选,是高端性能芯片封装的主流方案之一。我们认为,英伟达算力芯片的需求增长大幅提升了 CoWos 的封装需求,CoWos 有望进一步带动先进封装加速发展。

CoWos 技术是高端性能封装的主流方案

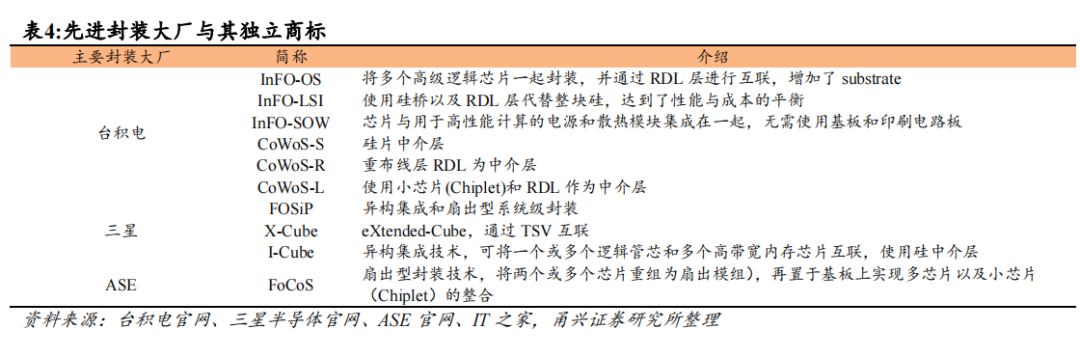

全球各大厂对纷纷对先进封装技术注册独立商标。近年来,在先进封装飞速发展的背景下,开发相关技术的公司都将自己的技术独立命名注册商标,如台积电的 lnFO、CoWoS,日月光的 FoCoS,Amkor 的 SLIM、SWIFT,三星的 I-Cube、H-Cube 以及 Intel 的 Foveros、EMIB 等。

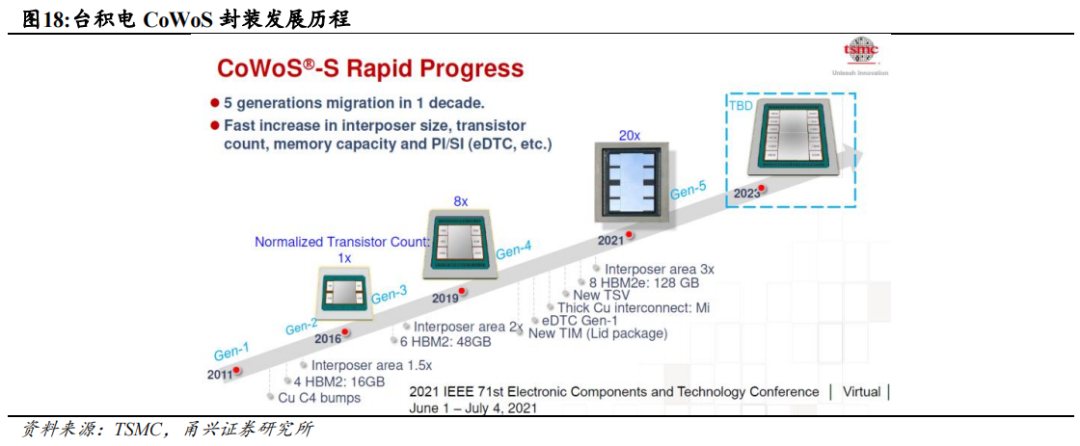

CoWoS 的主要优势是节约空间、增强芯片之间的互联性和降低功耗。台积电(TSMC)的 CoWoS(Chip on Wafer on Substrate)是一项 2.5D 多芯片封装技术,最早发布于 2011 年的《Advanced Reliability Study of TSVInterposers and Interconnects for the 28nm Technology FPGA》论文中。在过去十年,CoWoS 封装已经经过了五代的发展。目前采用 CoWoS 封装的产品主要分布于消费领域和服务器领域,包括英伟达、AMD 等推出的算力加速卡。

CoWoS 被应用于制造英伟达 GPU 所需要的工艺流程中,具备高技术壁垒特点,目前需求较大。我们认为,CoWoS 封装技术具备高集成度、高性能、芯片组合灵活性以及优秀稳定性与可靠性等特点,随着技术的不断进步和市场需求的增长,CoWoS 封装技术有望在未来继续取得突破,并在多重领域中得到应用。

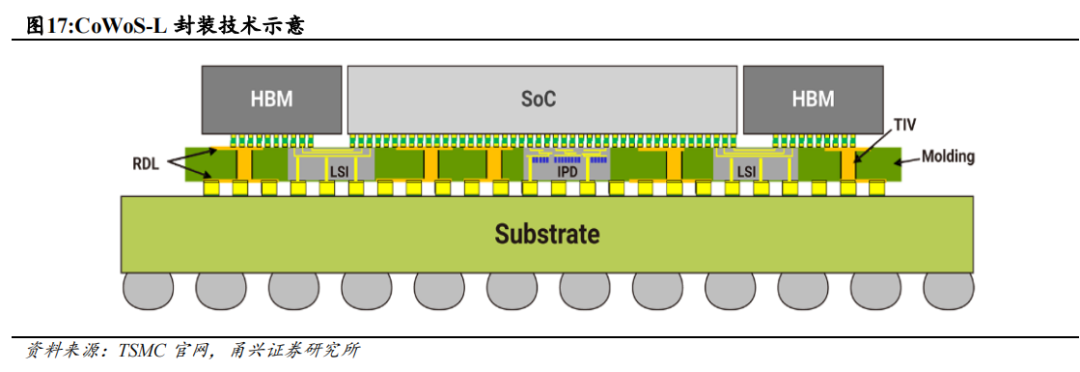

CoWoS 布局三类条线,满足复杂需求。CoWoS 可细分为 S、R、LSI 三类条线,分别为硅中介层(Si Interposer)、重布线层(RDL)与局部硅互联技术(LSI)。

根据台积电官网,CoWoS-R 采用 InFO 技术并应用 RDL 中介层,以提供芯片间的互连服务,重点应用于 HBM(高带宽内存)和 SoC 异构集成中。RDL 中介层由聚合物和铜引线构成,具备一定的灵活性,并能够拓展封装尺寸以满足更为复杂的功能需求。

CoWoS-R 技术的主要特点包括以下三方面。首先,RDL 互连器由多达6L 层铜线组成,最小间距为 4um (线宽/间距为 2um)。第二,互连具有良好的信号和电源完整性性能,路由线的 RC 值较低,可实现较高的传输数据速率。共面 GSGSG 和层间接地屏蔽以及六个 RDL 互连提供了卓越的电气性能。第三,RDL 层和 C4/UF 层因 SoC 与相应基板之间的 CTE不匹配而提供了良好的缓冲效果。C4 凸块的应变能量密度大大降低。

CoWoS 的技术历程与未来展望

目前 CoWoS 封装技术已经成为了众多国际厂商的优选,前景广阔。根据台积电,其于 2011 年推出了 2.5D Interposer 技术 CoWoS。2021 年台积电发布第 5 代 CoWoS 技术,其晶体管数量是第 3 代的 20 倍。CoWoS 本身的进化还体现在持续扩大硅中介层的面积,我们认为中介层越大,则能够容纳的裸片数量也越多;根据电子工程专辑,台积电 CoWoS 封装可解决光刻机可处理的极限尺寸(Reticle Limit)的问题。

根据台积电,2011 年首个 CoWoS 诞生,我们认为其为 FPGA、GPU 等高性能产品的集成提供了新的解决方案。2016 年发布第二代 CoWoS 方案,硅中介层尺寸大约是 1.5x reticle limit,并包含 4 个 HBM2,总容量为 16GB。2019 年开发的第 4 代 CoWoS,装有一个逻辑芯片和 6 个 HBM2,总容量为48GB(384Gbit),是第三代容量的 3 倍。

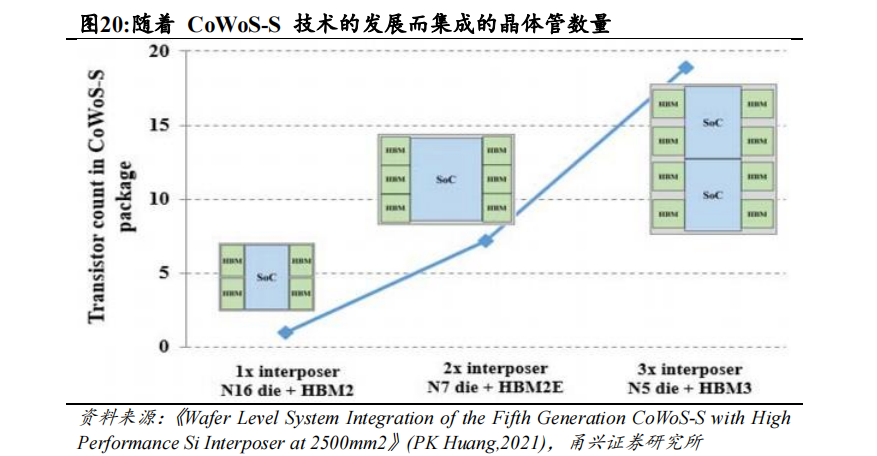

台积电发布第 5 代 CoWoS 技术,效能大幅提升。CoWoS-S5 通过将插层尺寸扩大到3 倍 rectile limit(2500 mm²),可在单个插层上集成 3 个或更多逻辑芯片组和 8 个 HBM。与上一代 CoWoS 相比,更大的尺寸与先进的节点顶层芯片相结合,可多集成近 20 倍的晶体管和 2 倍的内存堆栈(从 4 个增加到 8个)、CoWoS-S5 除了增加了硅中介层的尺寸外,还增加了部分新功能,以进一步提高其电气和热性能。

CoWoS-S5 引入新的金属堆栈、新的亚微米层(双镶嵌线路),以解决信号完整性问题。根据上述论文,HBM2E 存储堆栈应用于本代 interposer已得到验证,其传输速率为 3.2GT/s。未来将采用 HBM3,速率将提升至 4GT/。

CoWoS-S5 开发出了 5 层超低电阻互连的新金属方案,以支持 HBM3。新方案将金属迹线片电阻和通孔接触电阻都降低了 50%以上,但最小线宽/空间仍保持在亚微米以下,满足高密度布线的先决条件。在 CoWoS-S5,对良品率模式进行了监测,没有发现电阻损失或漂移。此外,这种新的互连方案还通过了电迁移(EM)、应力迁移(SM)和时间相关介质击穿(TDDB)测试,没有出现任何故障。

CoWoS-S5 有两种热解决方案,分别是环型封装与带散热器的盖型封装。根据上述论文,环型封装,裸片背面暴露在外,可与散热器直接接触;带散热器的盖型封装,在盖和裸片之间插入热界面材料(TIM),以提供连续的热界面。对于盖型封装方案,凝胶型 TIM 已使用了很长时间,工艺也比较成熟。

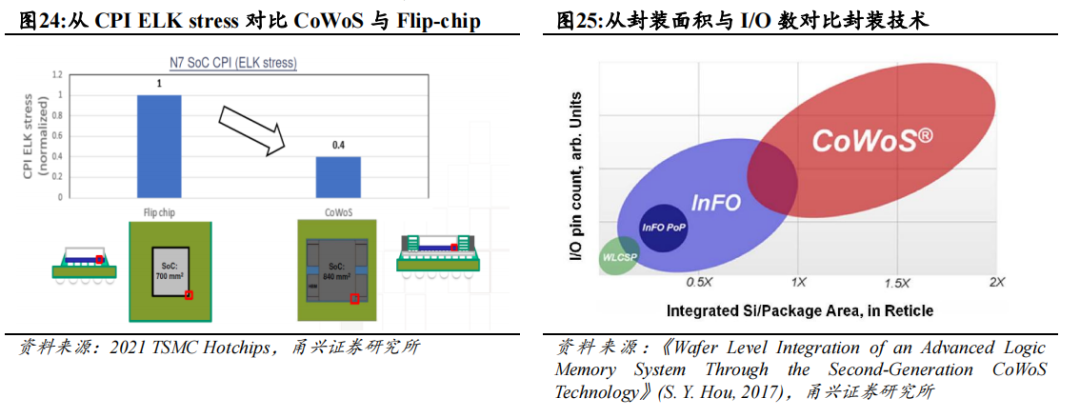

CoWoS 解决方案具备提供更高的存储容量和带宽的优势,适用于处理存储密集型任务,如深度学习、5G 网络、节能的数据中心等。除了扩展计算能力、输入/输出和 HBM 集成,CoWoS 技术还具备设计灵活性和更高的良率等优势,以支持先进工艺下的复杂特殊应用芯片设计。根据台积电资料显示,在关键尺寸工艺指数(Critical Dimension Process Index)方面与 ELK(Edge Liftoff Kirk)应力方面,CoWoS-S5 明显低于 FC 倒装封装技术,较低的 CPI 值表示制造过程更接近设计要求,具有更高的精度和一致性。

本号资料全部上传至知识星球,更多内容请登录智能计算芯知识(知识星球)星球下载全部资料。

免责申明:本号聚焦相关技术分享,内容观点不代表本号立场,可追溯内容均注明来源,发布文章若存在版权等问题,请留言联系删除,谢谢。

温馨提示:

请搜索“AI_Architect”或“扫码”关注公众号实时掌握深度技术分享,点击“阅读原文”获取更多原创技术干货。