对于零中频接收机,主要有IQ失配,直流偏移等问题[1]。

(1)当知道IQ增益失配和相位失配后,镜像抑制比是多少呢?

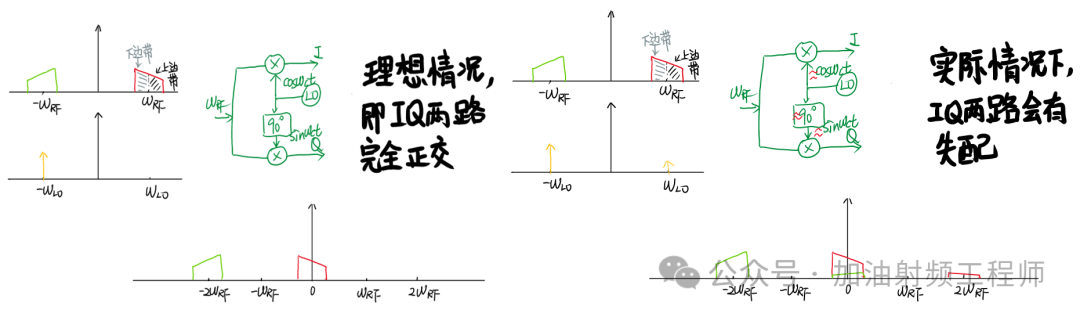

理论上,如果IQ两路完全匹配,那么基带处理后的信号,能够完全抑制镜像信号。

但是,实际上,IQ两路总是会失配,所以镜像信号总是存在。

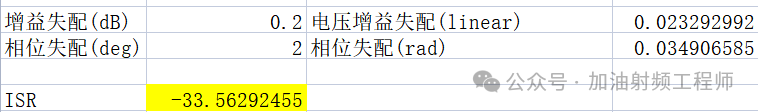

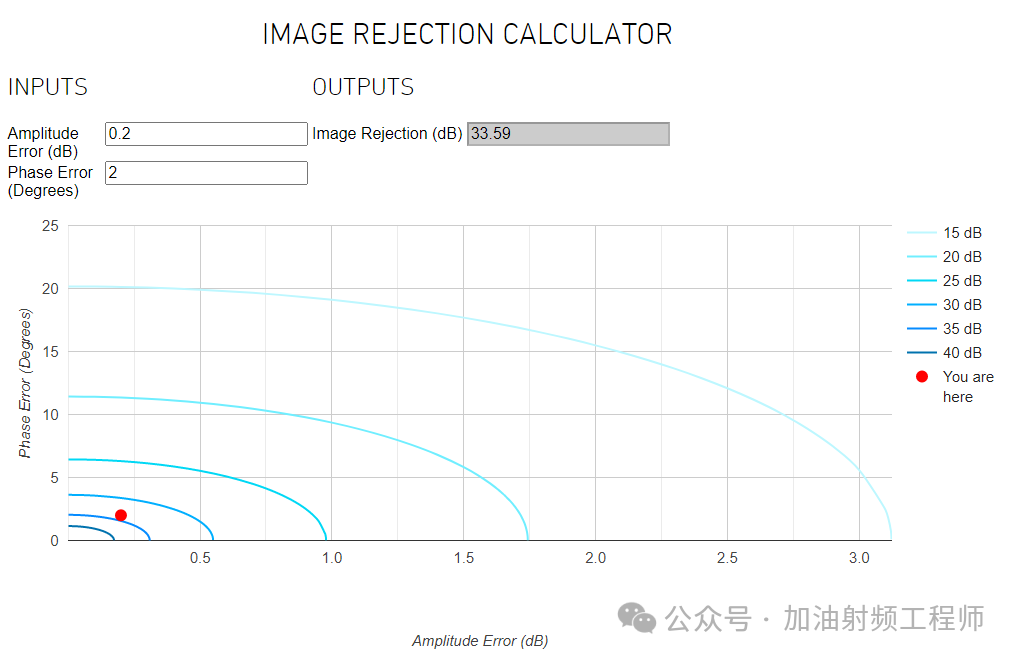

比如说,假设增益失配为0.2dB,相位失配位2度,那么就会产生33.56dBc的镜像抑制,在文献[2]中,写是39dBc,我觉得应该是不太对。

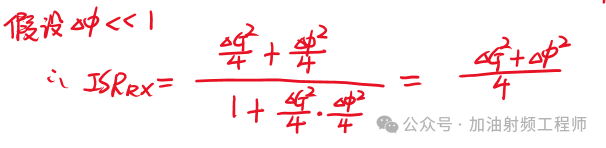

在零中频接收机中,为什么IQ失配会带来镜像干扰,可以得到ISR与增益失配和相位失配之间的关系为:

如果用excel表格来计算一下的话,则是:

或者在[3]中,也提供了类似的计算,计算结果与用上述公式计算出来的一致。

(2) IQ失配从哪里来?

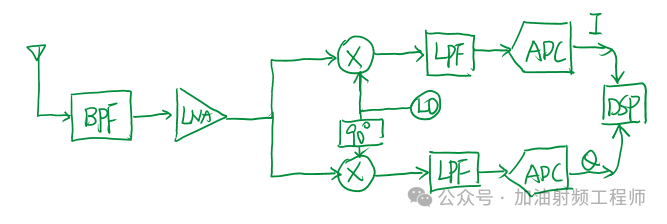

零中频接收机的大概框图,如下图所示。

所以,在IQ两路中的所有器件,都有可能带来IQ失配,从而产生镜像干扰,包括:

① I路ADC和Q路ADC

② I路LPF和Q路LPF

③ I路MIXER和Q路MIXER

④ LO的90度相移器

⑤ IQ两路中的放大器和数控衰减器等。

(3) 芯片中是怎么处理IQ失配的?

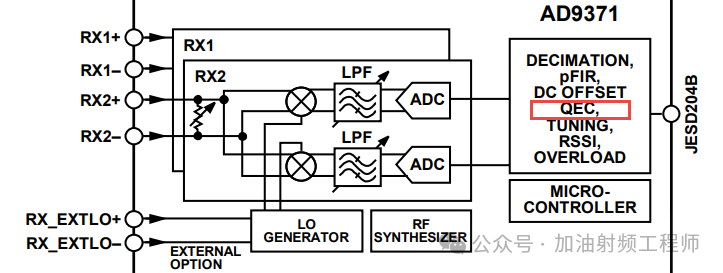

下图,是AD9371中接收机的框图示意图。

可以看到,在ADC之后的处理中,有一项叫QEC。是的,零中频接收机中,就是使用QEC模块(quadrature error correction)来对接收机的IQ失配进行校准。

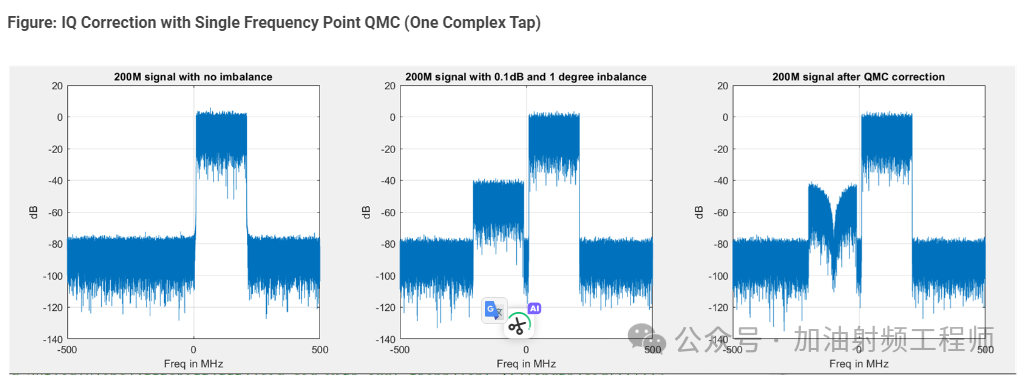

文献[2]中,展示了采用one complex tap的QEC,对400MHz带宽信号校准后的结果(这个不是AD9371的结果,是另外一篇文献上的,只是想说明,对于宽带信号而言,QEC的设计也是个挑战)。

为了便于观看,信号只给了一半,即200MHz。

左图是IQ完全匹配时候的图形,可以看到-200MHz的带宽内,没有东西,很平坦。

中间是IQ失配后产生的图形,此时IQ增益失配为0.1dB,相位失配为1deg,可以看到,在-200MHz的带宽内,镜像抑制约为-40dBc。

右图是进行了QEC校准后的图形,发现,其在-100MHz处的校准效果很好,但是在信号边缘处,校准效果变差。

所以,想在整个工作温度下,整个信号动态范围内,获得宽带宽内的高镜像抑制比,还是一个比较大的挑战[2]。

(4)

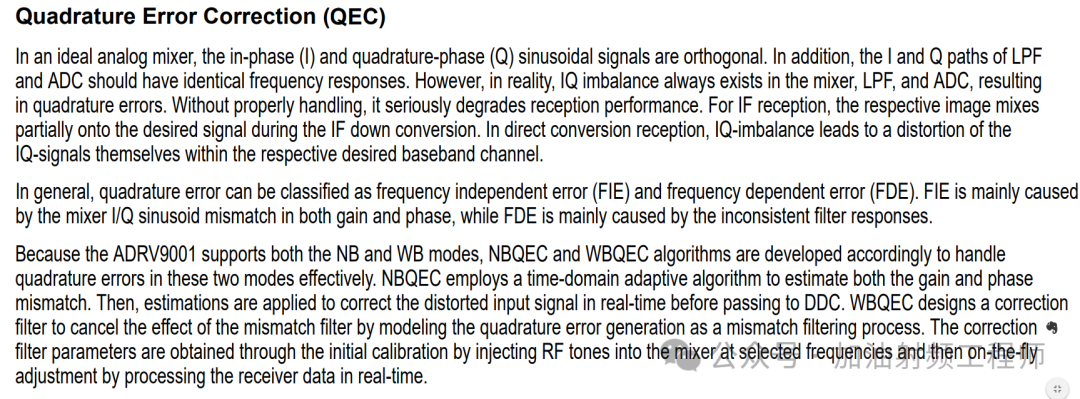

在ADRV9001的user guide[4]中,有对QEC的一段介绍,如下图所示。也就是说在ADRV9001中,QEC有两种模式,分别为NB和WB mode,两者的设计方法会有所不同。

参考文献:

[1] 池保勇 余志平 石秉学,CMOS 射频集成电路分析与设计

[2] https://docs.amd.com/r/en-US/wp541-coloc-direct-rf/Local-Oscillator-Leakage

[3]https://www.qorvo.com/design-hub/design-tools/interactive/image-rejection-calculator

[4]https://www.analog.com/media/en/technical-documentation/user-guides/adrv9001-system-development-user-guide-ug-1828.pdf

今年打算做2件事。

① 板级低噪放课程(149元):

打算做板级低噪放设计课程,课程内容,打算是从原理图+版图仿真开始,然后画板,然后投产+调测。

价格的话是149元,如果前期报过系统课程的话,则优惠50元,为99元。

②芯片LNA共学营(3999元,可流片封装):

这个项目主打自己学习为主,外援老师教授为辅助。 报名的号友,都会在一个群里,学习主要是靠自学。我每天会花四个小时左右在芯片学习上。因此我会列出每周自己的学习计划,以及给出自己的学习心得。号友可以参考我的计划,也可以遵照自己的计划进行。中间,会请老师进行辅导和答疑,大概会进行三次左右。

共学营开营后,会设置一个流片的deadline(目前打算设置在一年左右),需要在这个deadline之前把版图准备好,大家一起流片。

价格是3999元。

你有意愿报名的话,可以加我微信,说明一下意向,并注明是对板级有趣,还是芯片级的有兴趣。说明意向的时候,不用付费,等我差不多规划完,确认开班了,我再统一拉群。

完结接收机课程吆喝处哈(已在平台上购买的同学,加我微信,领课件资料哈!)

想了解接收机的底层理论知识,可以选择这门课;

想了解ADS的系统仿真,可以选择这门课;

想了解SystemVue的系统仿真,可以选择这门课。

想报名的同学,可以海报底部扫码哈!

☜左右滑动查看更多

Slide for more photos