前几天,使用 千分之一精度的电阻,搭建了 R2R 梯形电阻 DAC电路,通过实测,电路达到了 12bit 的线性精度。下面,我思考一个问题,那就是,如果降低 R2R 的阶次,比如降低到 12bit,那么它的线性精度是多少呢? 下面通过实验,或者相应的数据,来尝试给出这个问题的解答。

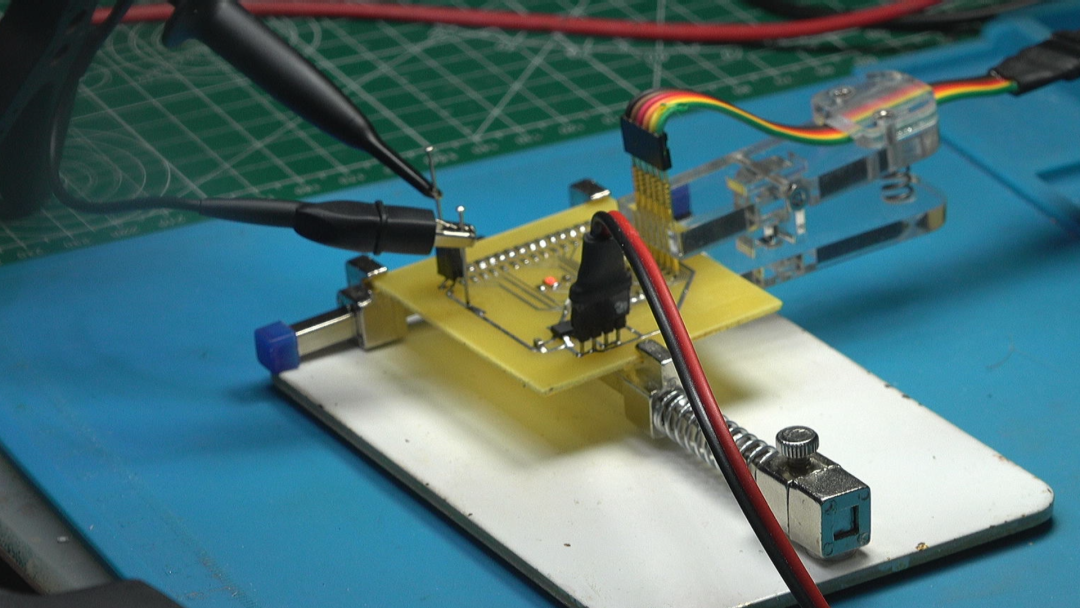

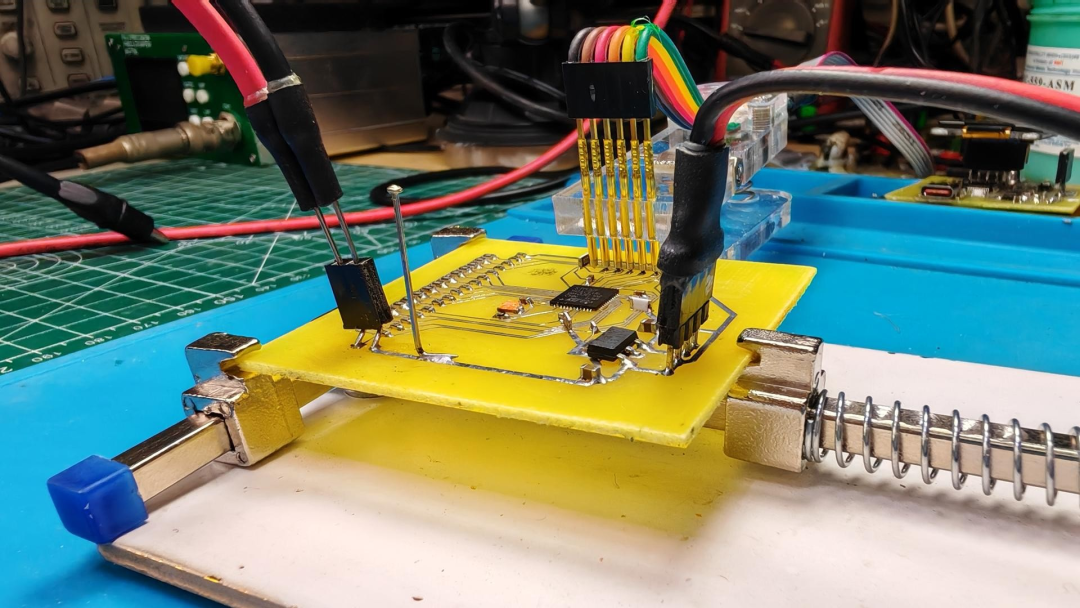

▲ 图1.1.1 测试电路原理图

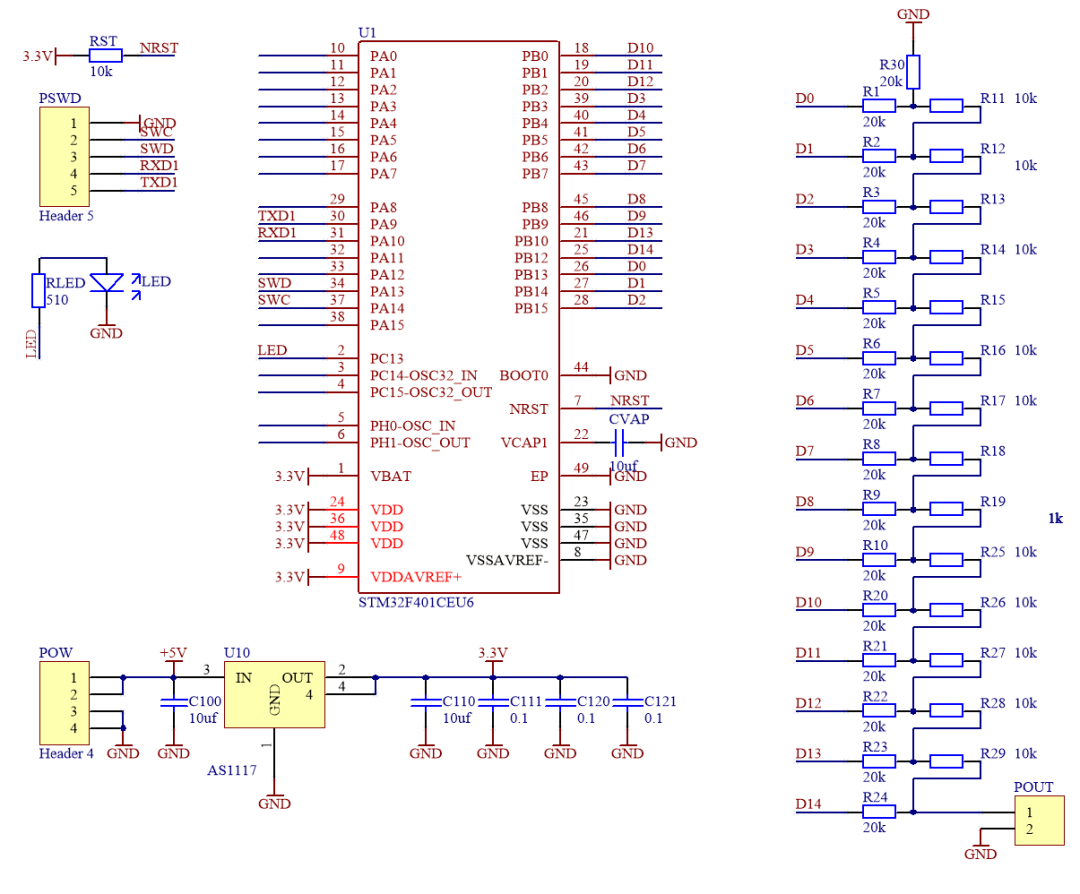

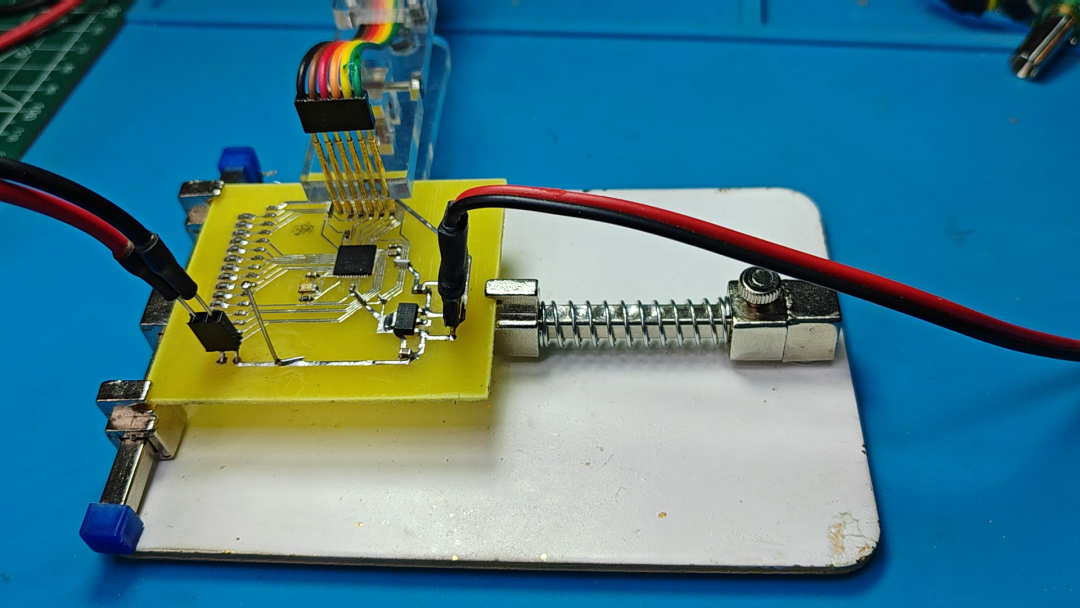

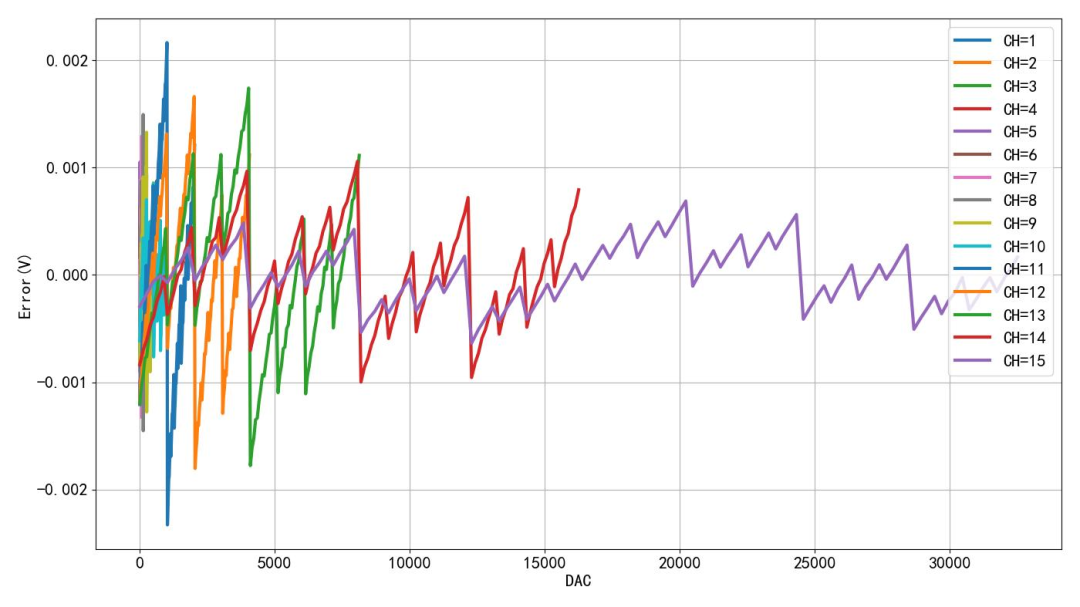

▲ 图1.1.2 测试电路PCB通过编程,测量DAC通道从 1 变化到15,对应每个DAC输出对应的输出电压。通过 DM3068记录每种通道个数 最多128 个测量数据。这个过程虽然是程序自动完成,但是还是耗费了我 今天上午将近 半个小时的测量时间。对于每组数据计算 线性误差曲线,这是计算结果,可以看到,随着输出通道的数量的提高,线性误差曲线也逐步减小。当输出通道达到 15 时,也就是图表中最长的那组数据,可以看到它对应的误差最小。

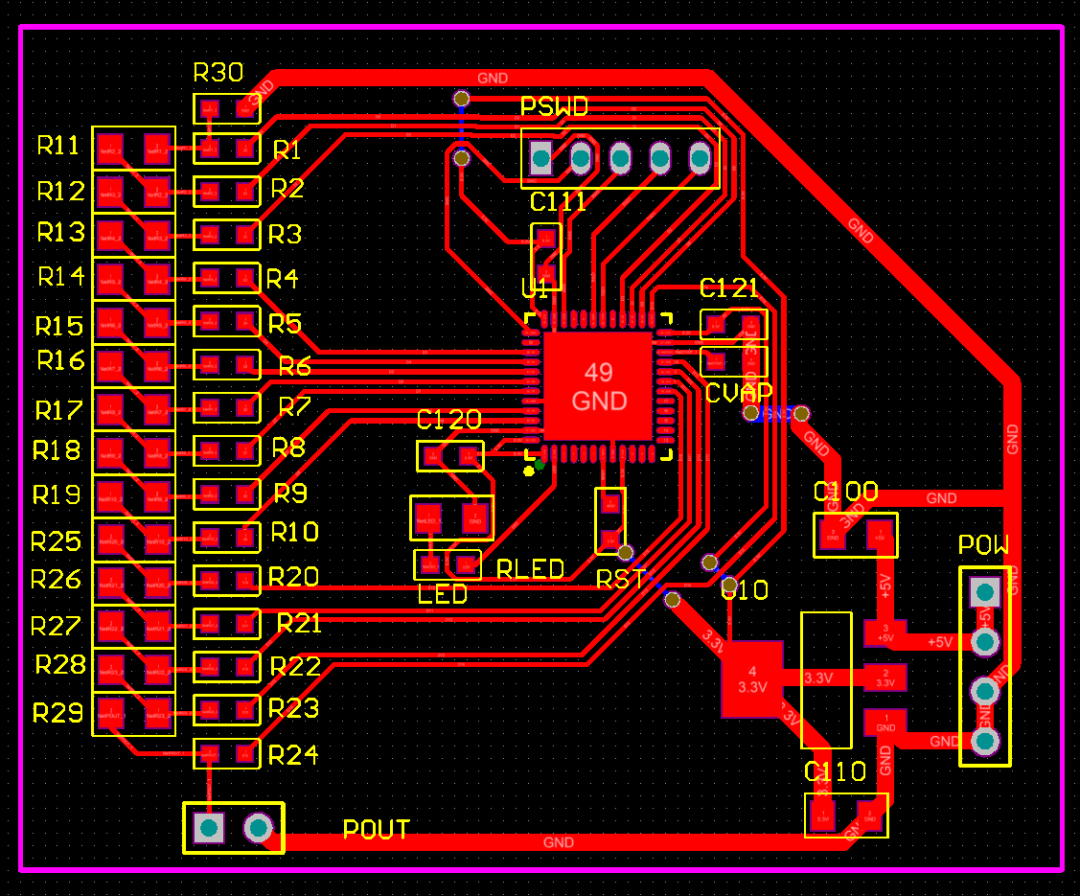

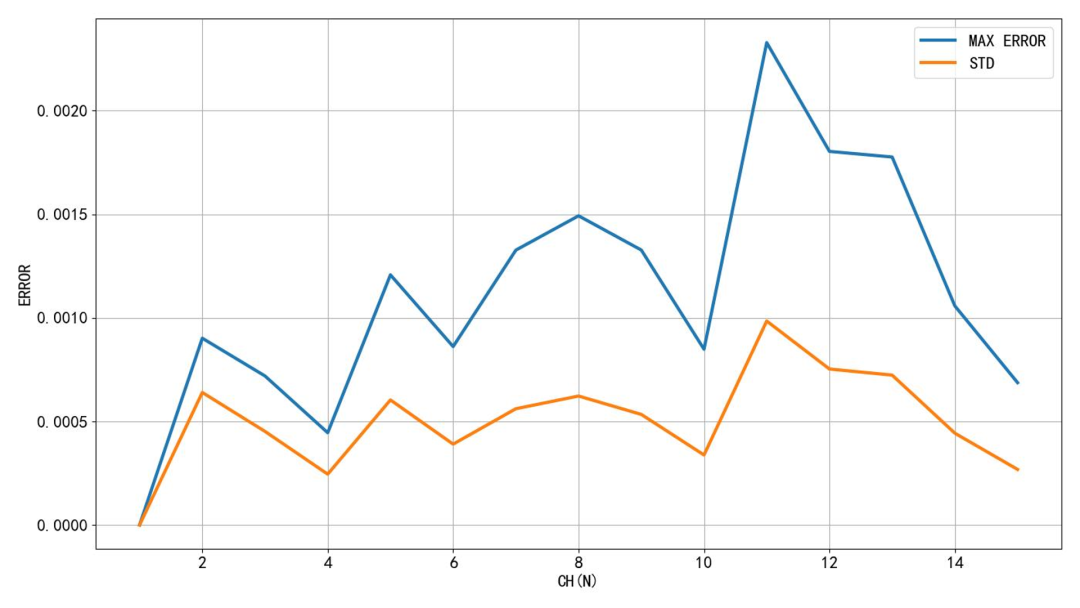

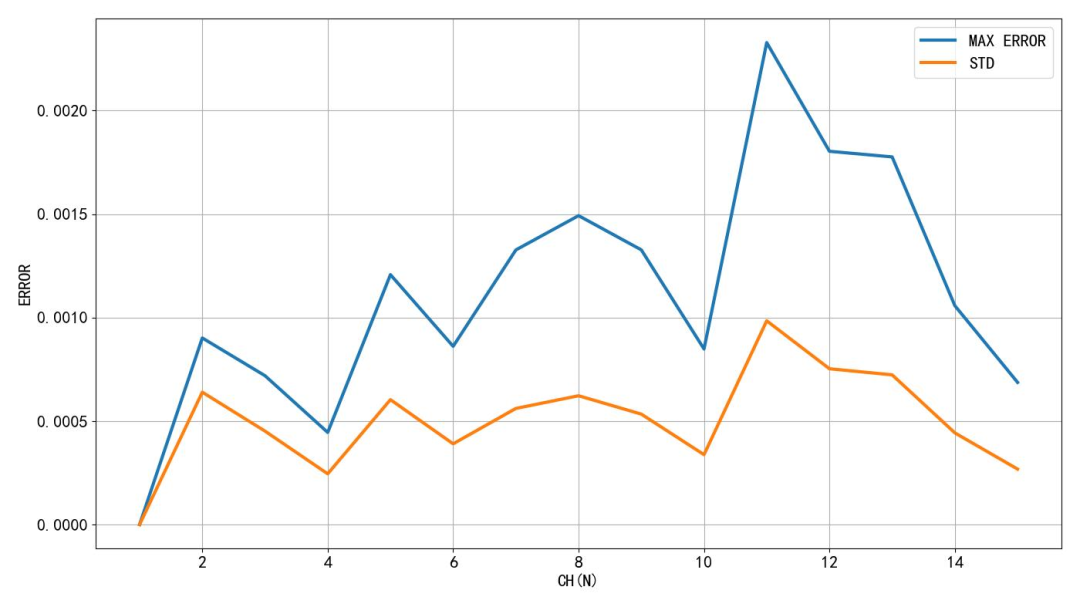

▲ 图1.2.1 不同的通道与误差曲线但是,将上面测量不同DAC 通道下,误差的最大值 和 标准方差绘制出来,情况有了变化。线性误差的最大值是青色曲线,下面是线性误差的均方根。可以看到,线性误差在 DAC 通道数为 11 的时候,达到峰值,然后又随着通道数增加而下降。对于误差的均方根,则是呈现一种平稳的态势,也就是无论输出通道数是多少,DAC 线性误差的均方根都基本上维持在 0.5mV左右。这个结果的确出乎我的意外。

▲ 图1.2.2 不同的通道数对应的线性误差的最大值和标准方差今天一大早对前几天制作的 15bit 电阻 R2R DAC的线性误差进行了测量,虽然都是 千分之一精度的电阻,但是选择了不同的输出通道数,对应的线性误差的均方根却是大体相同的。这是实验测量的结果,后面有时间再进行理论分析吧。今天是清明节前一天,上午 还有课程,待会儿去上课。

15bit R2R 电阻梯 DAC 性能测试: https://zhuoqing.blog.csdn.net/article/details/137032684