概述:

CP是把坏的Die挑出来,可以减少封装和测试的成本。可以更直接的知道Wafer 的良率。

FT是把坏的chip挑出来,检验封装的良率。

现在对于一般的wafer工艺,很多公司多把CP给省了,目的是减少成本。

CP对整片Wafer的每个Die来测试,FT则对封装好的Chip来测试。

CP Pass 才会去封装。然后FT,确保封装后也Pass。

WAT是Wafer Acceptance Test,对专门的测试图形(test key)的测试,通过电参数来监控各步工艺是否正常和稳定。芯片

CP是wafer level的chip probing,是整个wafer工艺,包括backgrinding和backmetal(if need),对一些基本器件参数的测试,如vt(阈值电压),Rdson(导通电阻),BVdss(源漏击穿电压),Igss(栅源漏电流),Idss(漏源漏电流)等,一般测试机台的电压和功率不会很高;

FT是packaged chip level的Final Test,主要是对于这个(CP passed)IC或Device芯片应用方面的测试,有些甚至是待机测试。

Pass FP还不够,还需要做process qual 和product qual。

CP 测试对Memory来说还有一个非常重要的作用,那就是通过MRA计算出chip level 的Repair address,通过Laser Repair将CP测试中的Repairable die 修补回来,这样保证了yield和reliability两方面的提升。

CP是对wafer进行测试,检查fab厂制造的工艺水平。

FT是对package进行测试,检查封装厂制造的工艺水平。

对于测试项来说,有些测试项在CP时会进行测试,在FT时就不用再次进行测试了,节省了FT测试时间;

但是有些测试项必须在FT时才进行测试(不同的设计公司会有不同的要求)。

一般来说,CP测试的项目比较多,比较全;FT测的项目比较少,但都是关键项目,条件严格。但也有很多公司只做FT不做CP(如果FT和封装yield高的话,CP就失去意义了)。

在测试方面,CP比较难的是探针卡的制作,并行测试的干扰问题。FT相对来说简单一点。memory测试的CP会更难,因为要做redundancy analysis,写程序很麻烦。

CP在整个制程中算是半成品测试,目的有2个,1个是监控前道工艺良率,另一个是降低后道成本(避免封装过多的坏芯片),其能够测试的项比FT要少些。最简单的一个例子,碰到大电流测试项CP肯定是不测的(探针容许的电流有限),这项只能在封装后的FT测。不过许多项CP测试后FT的时候就可以免掉不测了(可以提高效率),所以有时会觉得FT的测试项比CP少很多。

应该说WAT的测试项和CP/FT是不同的。CP不是制造(FAB)测的!

CP的项目是从属于FT的(也就是说CP测的只会比FT少),项目完全一样的;不同的是卡的SPEC而已;因为封装都会导致参数漂移,所以CP测试SPEC收的要比FT更紧以确保最终成品FT良率。还有相当多的DH把wafer做成几个系列通用的die,在CP是通过trimming来定向确定做成其系列中的某一款,这是解决相似电路节省光刻版的最佳方案;所以除非你公司的wafer封装成device是唯一的,且WAT良率在99%左右,才会盲封的。

据我所知盲封的DH很少很少,风险实在太大,不容易受控。

WAT:wafer level 的管芯或结构测试。

CP:wafer level 的电路测试含功能。

FT:device level 的电路测试含功能。

CP=chip probing。

FT=Final Test。

CP 一般是在测试晶圆,封装之前看,封装后都要FT的。不过bump wafer是在装上锡球,probing后就没有FT。

FT是在封装之后,也叫“终测”。意思是说测试完这道就直接卖去做application。

CP用prober,probe card。FT是handler,socket。

CP比较常见的是room temperature=25度,FT可能一般就是75或90度。

CP没有QA buy-off(质量认证、验收),FT有。

CP两方面:

1. 监控工艺,所以呢,觉得probe实际属于FAB范畴。

2. 控制成本。Financial fate。我们知道FT封装和测试成本是芯片成本中比较大的一部分,所以把次品在probe中reject掉或者修复,最有利于控制成本。

FT:

终测通常是测试项最多的测试了,有些客户还要求3温测试,成本也最大。

至于测试项呢,

1. 如果测试时间很长,CP和FT又都可以测,像trim项,加在probe能显著降低时间成本,当然也要看客户要求。

2. 关于大电流测试呢,FT多些,但是我在probe也测过十几安培的功率mosfet,一个PAD上十多个needle。

3. 有些PAD会封装到device内部,在FT是看不到的,所以有些测试项只能在CP直接测,像功率管的GATE端漏电流测试Igss

CP测试主要是挑坏die,修补die,然后保证die在基本的spec内,function well。

FT测试主要是package完成后,保证die在严格的spec内能够function。

CP的难点在于,如何在最短的时间内挑出坏die,修补die。

FT的难点在于,如何在最短的时间内,保证出厂的Unit能够完成全部的Function。

一

芯片测试

芯片测试分两个阶段,一个是CP(Chip Probing)测试,也就是晶圆(Wafer)测试。另外一个是FT(Final Test)测试,也就是把芯片封装好再进行的测试。

CP测试的目的就是在封装前就把坏的芯片筛选出来,以节省封装的成本。同时可以更直接的知道Wafer 的良率。CP测试可检查fab厂制造的工艺水平。现在对于一般的wafer成熟工艺,很多公司多把CP给省了,以减少CP测试成本。具体做不做CP测试,就是封装成本和CP测试成本综合考量的结果。

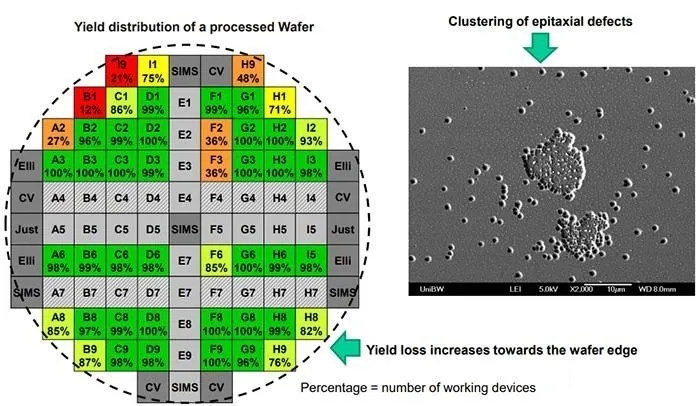

一片晶圆越靠近边缘,die(一个小方格,也就是一个未封装的芯片)出问题的概率越大。

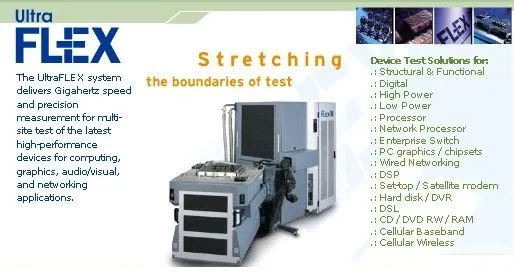

随着芯片规模的越来越大,测试也更为复杂。ATE(Automatic Test Equipment)也就应运而生。目前ATE公司最大的是Teradyne和爱德万,NI目前也在做这一块,并且很多小公司都在用NI的仪器。国内的公司知名的有长川科技。

ATE作为集成了众多高精密的Instruments的设备,价格自然不菲。一台泰瑞达的高端Ultra Flex可以买上海的几套房!

二

芯片测试流程

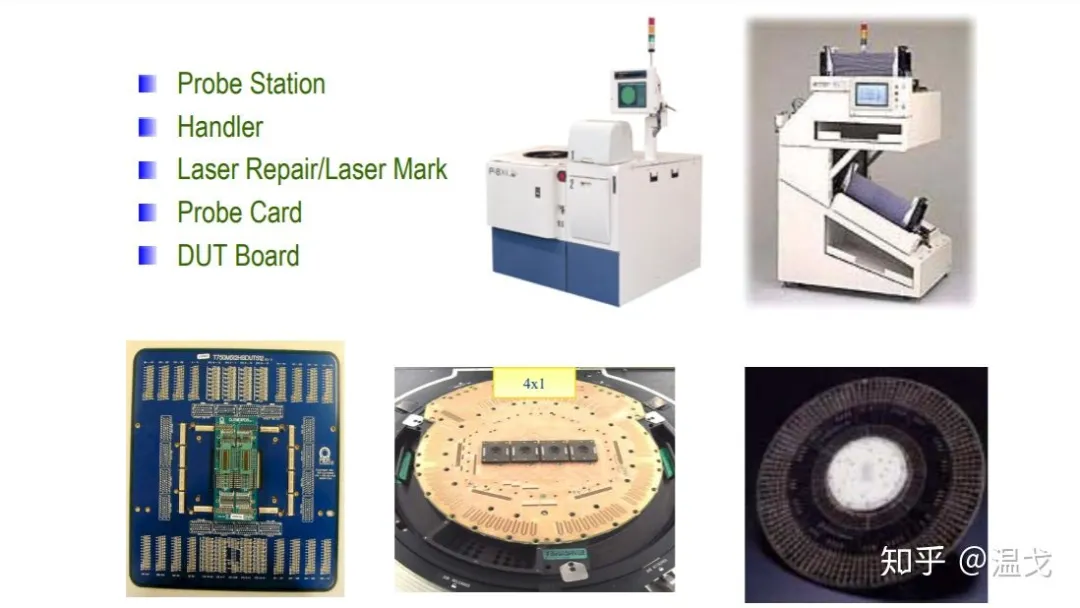

在测试之前,当然要有ATE设备,CP测试需要Probe Card, FT测试需要Load board, Socckt等。来一张全家福吧。最下边左一是Load Board(又叫DUT Board), 左二是Probe Card.

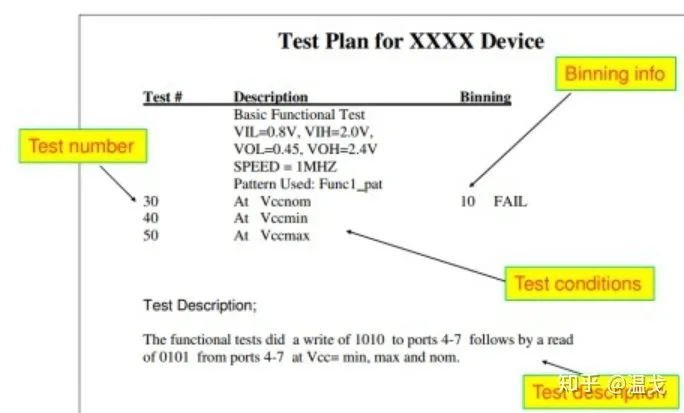

然后由芯片设计公司来提供Design Spec和Test Spec(datasheet)来制定Test Plan,开发测试程序,建立测试项。

Test Plan示意图:

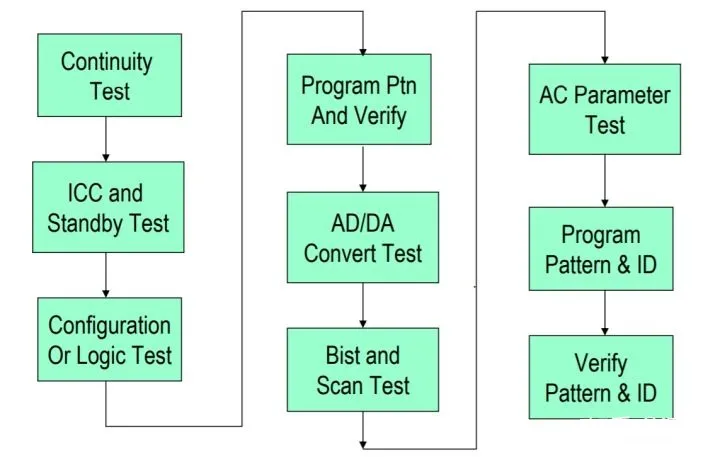

一般测试通常包含以下测试项:

DC parameters Test

主要包含以下测试,Continuity测试(又称open/short test)主要是检查芯片的引脚以及和机台的连接是否完好。其余的测试都是检查DC电气参数是否在一定的范围内。

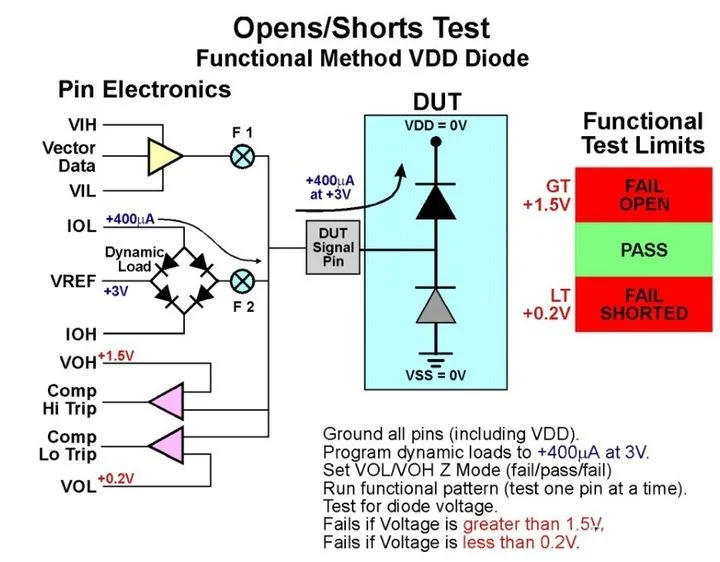

Continuity Test

Leakage Test (IIL/IIH)

Power Supply Current Test (IDDQ)

Other Current/Voltage Test (IOZL/IOZH, IOS, VOL/IOL, VOH/IOH)

LDO,DCDC 电源测试。

以下这张图就是open/short test原理示意图,DUT(Device Under Test)的引脚都挂有上下两个保护二极管,根据二极管单向导通以及截至电压的特性,对其拉/灌电流,然后测试电压,看起是否在设定的limit范围内。

整个过程是由ATE里的instruments PE(Pin Electronics)完成的。

这部分的测试主要是跑测试向量(pattern),pattern则是设计公司的DFT工程师用ATPG(auto test pattern generation)工具生成的。

pattern测试基本就是加激励,然后捕捉输出,再和期望值进行比较。

与Functional Test相对应的的是Structure Test,包括Scan,Boundary Scan等,Pattern是根据芯片制造过程中产生的的defects和fault 模型来产生的。

应用Structure Test能更好的提高覆盖率。

当然还有Build-in-Self-Test (BIST)主要是针对memory进行的测试。

AC Parameters Test

主要是AC Timing Tests,包含Setup Time, Hold Time, Propagation Delay等时序的检查。

ADC and DAC Test

主要是数模/模数混合测试,检查信号经过ADC/DAC后的信号是否符合期望,这个地方涉及到的信号知识比较多。总体来说包含静态测试和动态测试。

Static Test – Histogram method (INL, DNL)

Dynamic Test – SNR, THD, SINAD

除了以上常规测试项,根据芯片的类型不同可能会进行不同的测试,比如RF测试,SerDes高速测试,Efuse测试等。

一个基本的测试流程图如下:

测试流程图

所有的测试项都是在ATE上执行的,一般会执行几秒到几十秒,因为ATE是根据机时来付费的(很少有海思,苹果这种土豪公司一次买数十台),所以缩短测试时间变得尤其重要!另外一般芯片在量产测试的时候,都是百万颗或者千万颗,每个芯片节省一秒,总体来说缩短的时间还是很可观的。

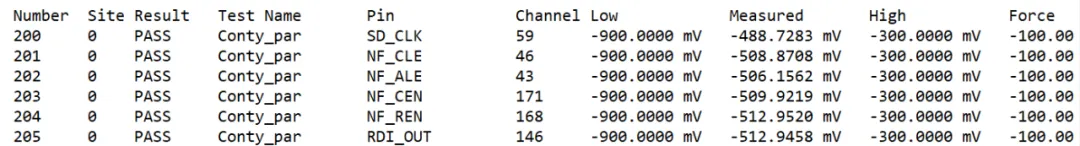

在测试执行完成后,ATE会输出一个Datalog,以显示测试结果。对于测试pass或fail测试项的不同,也会对其进行分类(Bin),最后由Handler分拣。

datalog 示意图:

以上就是芯片的测试完整流程。再放两张芯片测试的封测厂/实验室的环境图:

封测厂需要穿静电服

图为Advantest测试机台

三

两个问题

1、BGA 这样的封装,应该不能多次焊接吧,那又如何上电测试呢?

对于封装好的芯片,通常测试是不需要进行焊接的,它和ATE机台的连接方式是通过socket和Load board。

socckt也就是放芯片的底座,长这样:

不同大小,不同封装类型的芯片,socket也不同,有专门的做这个的厂商。

先把芯片放到socckt里,再把socket放到load board上,load board再放在机台上。有的load board很重,对很多女同志来说搬起来是有些辛苦啊!

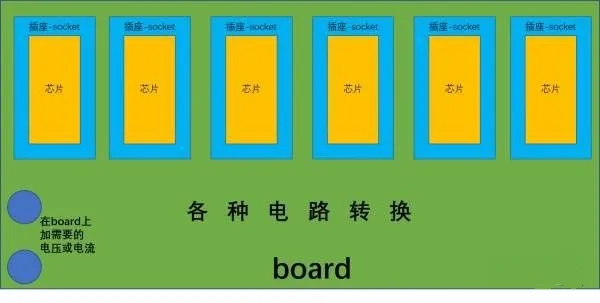

一个load board上面支持放多个socket,我们称其为site。示意图如下,共6个site,可以对6个芯片同时进行测试:

2、那么多的功能,真的要写软件一样一样测吗?

在这里先说明一下,芯片的逻辑功能是有IC验证工程师来完成的,是在流片之前,并不依赖于测试。

而芯片测试里的function test/structure test是跑pattern, 测试的是在制造过程中芯片是否有缺陷,从而影响功能/性能。

所以测试工程师所需要的关心的就是把pattern都跑通,如果跑不通可能会和DFT工程师一起进行diagnosis。

测试工程在写测试项的时候,也不是要一行一行代码去写,通常ATE机台的嵌入式软件都有提供测试项的Template, 只需要填写参数就好。另外针对一些大客户的成熟测试项,也会开发一些测试模板,留好必要的参数接口,这样就很方便应用到其他的芯片测试上。

四

写在最后

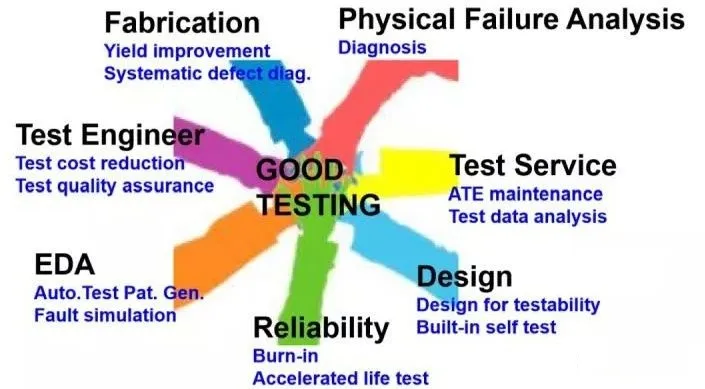

一个完备的的芯片测试不是靠芯片测试工程师一个人完成的,而是需要设计工程师,DFT工程师的支持,以及由可靠的EDA工具,优秀的硬件支撑等多方因素共同决定的。

芯片测试是极其重要的一环,有缺陷的芯片能发现的越早越好。在芯片领域有个十倍定律,从设计-->制造-->封装测试-->系统级应用,每晚发现一个环节,芯片公司付出的成本将增加十倍。

所以测试是设计公司尤其注重的,如果把有功能缺陷的芯片卖给客户,损失是极其惨重的,不仅是经济上的赔偿,还有损信誉。因此芯片测试的成本也越来越高!

在 IC 行业,每一个环节都要十分小心,一次流片的费用在数十万美金,一天的ATE机台使用几百美金。而一个芯片的利润可能只有几美分。这也是IC行业投资周期长,收益少的原因,基本前几年都在亏钱。幸运的是国家越来越重视芯片了,期待国内IC发展能越来越好。