低功耗设计一直是芯片设计追求的目标,常规的低功耗设计技术有:

1、clk gating----- 在模块不工作的时候,将时钟信号关掉;2、Power gating------ 在模块不工作的时候,直接断掉模块供电;power gating相比较于clk gating更加的省电,但是有一个问题,power gating确实更省电,但是在断电之后,模块如果想要重新启动,需要重新进行上电,等到电源稳定之后,然后再恢复时钟信号,这个过程就需要一个延时。典型的场景,比如手机SIM卡的I/O,如果在休眠进入低功耗之后,SIM I/O直接power gating,在退出低功耗状态时,重新上电初始化的延时会严重影响用户体验,可能在系统唤醒后,发现半天无法识网,从而影响用户体验。

所以在芯片的I/O设计中采用了retention的技术,既采用了power gating节省了功耗,而且又不丢失信息,从而可以实现快速启动,那么retention技术是如何实现的呢?该方案的关键点就在于,支持retention的I/O包含了两种类型的寄存器:

主寄存器面积大,工作电压高,采用的晶体管阈值电压低,因为工作电流大,这样可以保证该寄存器在正常工作时驱动能力更强,速度更快。

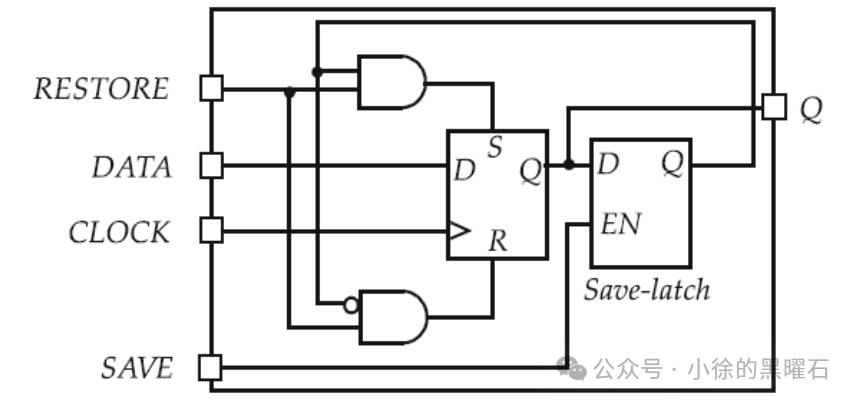

而从寄存器,即所谓的retention寄存器,面积相对小一点,采用阈值电压高的晶体管,驱动电压也会更低,因此消耗的电量就更少。需要注意的一点是,在芯片中,包含retention逻辑的寄存器,因为有两个电压域,为了放置电压倒灌漏电等问题,需要插入isolation cell做电压隔离。retention cell的电路结构如上图所示,对比普通的I/O就是多了一个save-latch:

1. Save-latch一般是一个HVt cell, 以节省静态功耗;

2. Save-latch是由备用电源供电;

正常情况下,Retention flip-flop和普通的flip-flop功能一样,但是会把输出锁存在Save-latch中,当电源关掉时,由于Save-latch是由备用电源供电,Save-latch还是保持原有状态;当RESTORE信号拉成1时,Save-latch会把输出送给前面的flip-flop,就能立刻恢复下电时的状态了。