今天给大侠带来基于 FPGA 的图像边缘检测设计,话不多说,上货。

设计流程如下:mif文件的制作→ 调用 ip 核生成rom以及仿真注意问题→ 灰度处理→ 均值滤波:重点是3*3 像素阵列的生成→ sobel边缘检测→ 图片的显示→ 结果展示 。

WIDTH=16 ; //数据位宽DEPTH=19200 ; // rom 深度即图片像素点的个数ADDRESS_RADIX=UNS ; //地址数据格式DATA_RADIX=BIN ; //数据格式CONTENTBEGIN0:1010110011010000 ; // 地址 :数据 ;注意格式要和上面定义的保持统一1:1010110011010000 ;2:1010010010110000 ;......19198:1110011011111001 ;19199:1110011011011000 ;END;

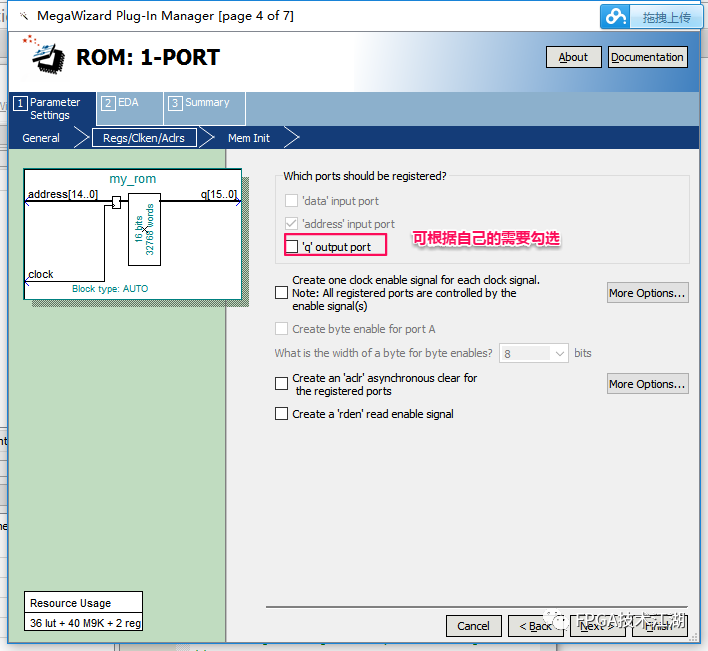

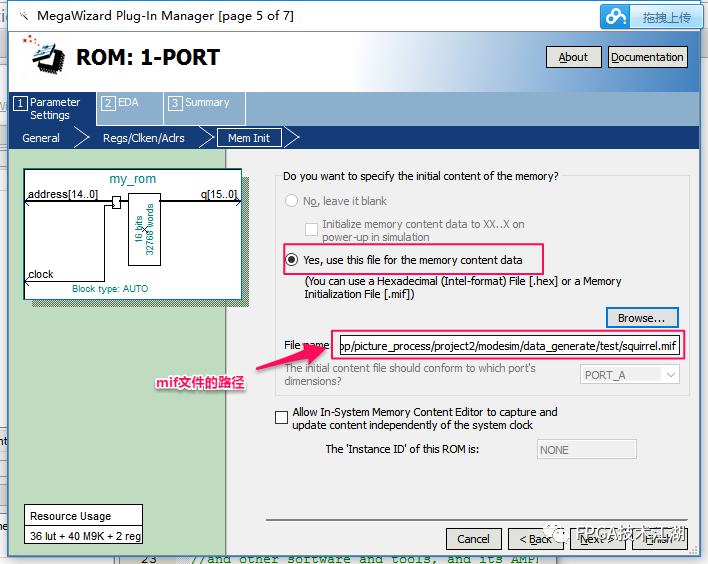

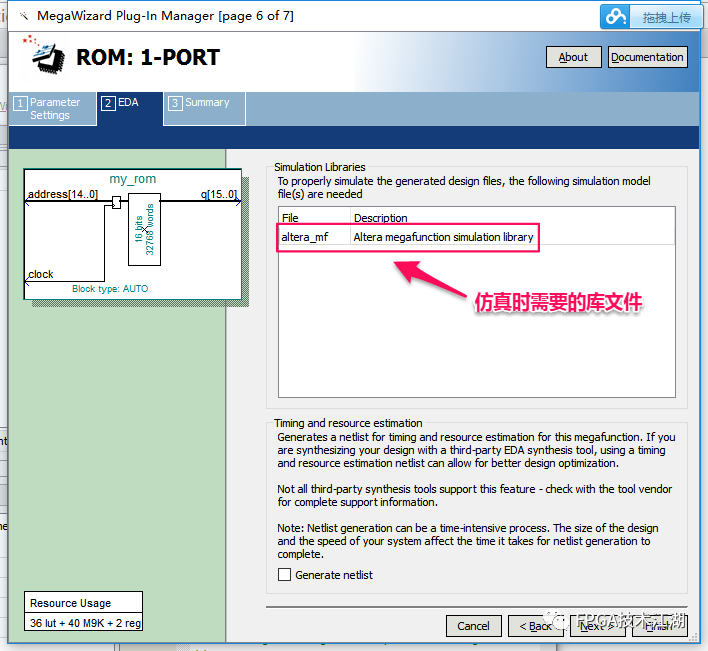

二、ip 核生成 rom 及仿真时需要注意的问题

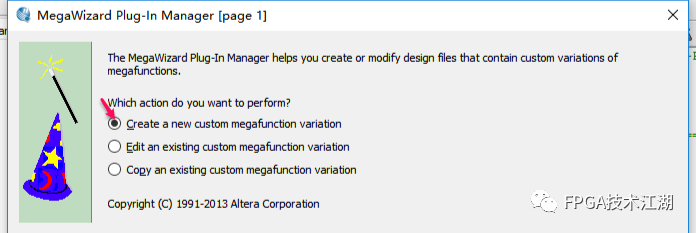

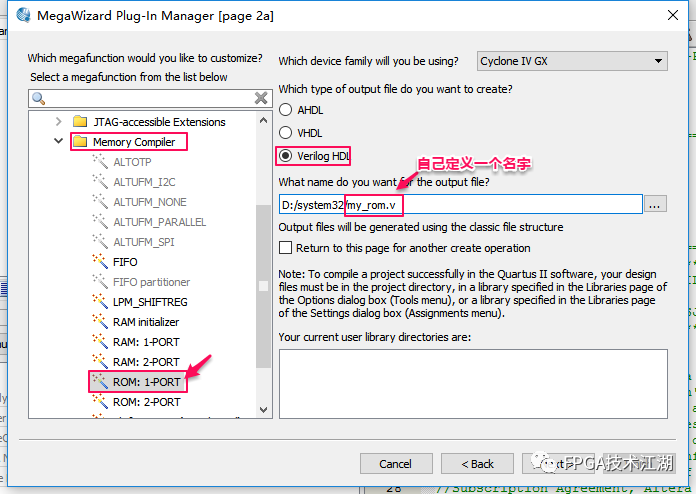

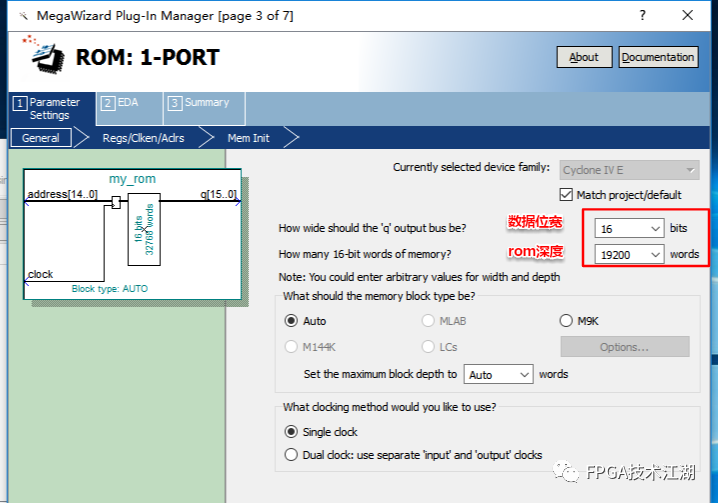

ip 核生成 rom

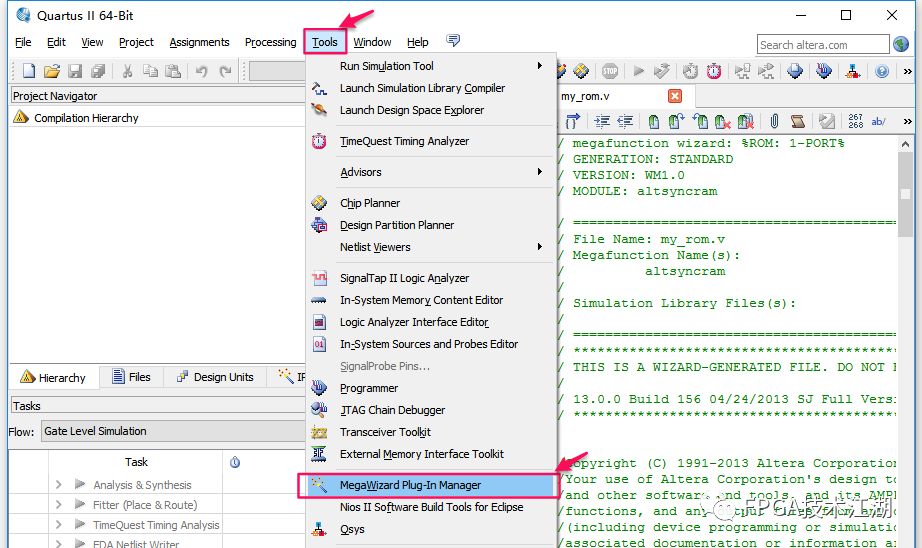

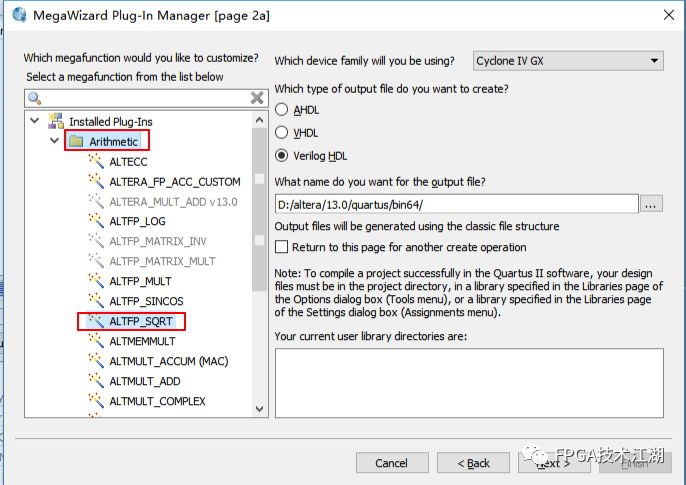

1、Tools -> MegaWizard Plug-In Manager

浮点算法:Gray=0.299R+0.587G+0.114B

平均值法:Gray=(R+G+B)/3;

仅取单色(如绿色):Gray=G;

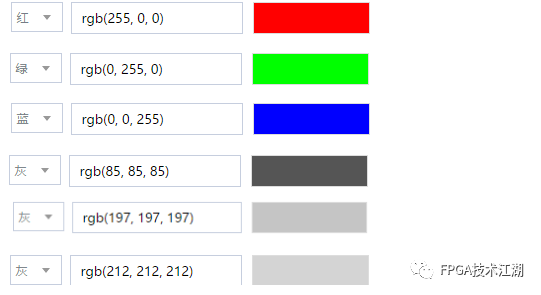

站长工具颜色代码查询、RGB颜色值:

http://tool.chinaz.com/tools/selectcolor.aspx

always @(posedge clk or negedge rst_n)beginif(rst_n==1'b0)beginred_r1 <= 0 ;green_r1 <= 0 ;blue_r1 <= 0 ;endelse beginred_r1 <= red * 77 ; //放大后的值green_r1 <= green * 150;blue_r1 <= blue * 29 ;endendalways @(posedge clk or negedge rst_n)beginif(rst_n==1'b0)beginGray <= 0; // 三个数之和endelse beginGray <= red_r1 + green_r1 + blue_r1;endendalways @(posedge clk or negedge rst_n)beginif(rst_n==1'b0)beginpost_data_in <= 0; //输出的灰度数据endelse beginpost_data_in <= { Gray[13:9], Gray[13:8], Gray[13:9] };//将Gray值赋值给RGB三个通道endend

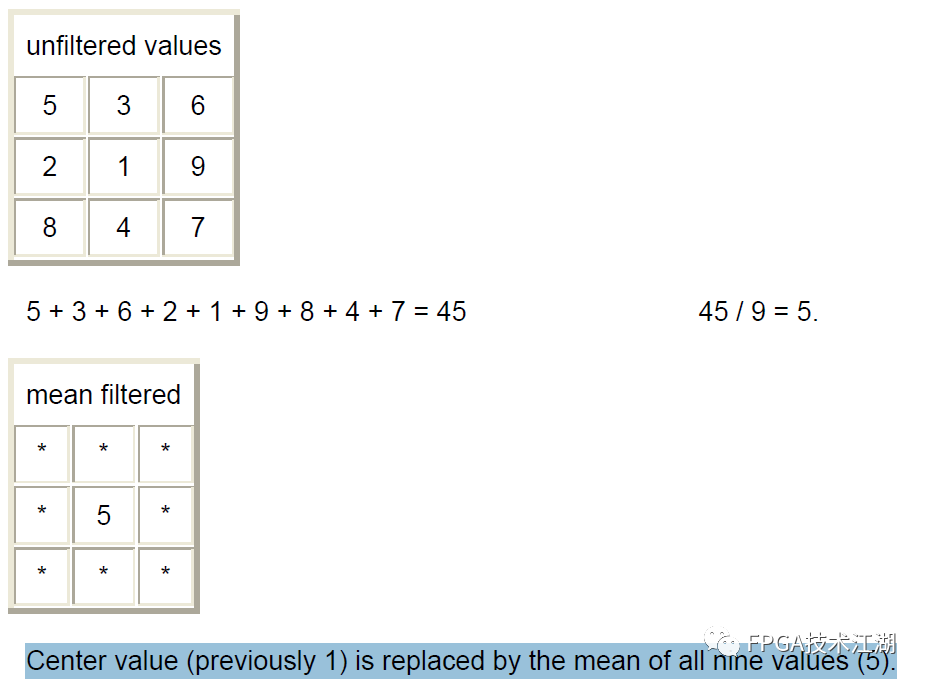

这里还是可以明显的感觉到不同的, 没有好坏之分,就是第二幅图片看上去更为平滑。继续我们的问题, 那这里均值平滑是否具有去除噪声的功能呢?我们搞来了椒盐噪声(就是随机的白点,黑点)来试试手:

平滑处理之后:

void meanFilter (unsigned char* corrupted, unsigned char* smooth, int width, int height){memcpy ( smooth, corrupted, width*height*sizeof(unsigned char) );for (int j=1;j{for (int i=1;i{smooth [ j*width+i ] = ( corrupted [ (j-1)*width+(i-1) ] + corrupted [ (j-1)*width+i] + corrupted [ (j-1)*width+(i+1) ] +corrupted [ j*width+(i-1) ] + corrupted [ j*width+i] + corrupted [ j*width+(i+1) ] +corrupted [ (j+1)*width+(i-1) ] + corrupted [ (j+1)*width+i] + corrupted [ (j+1)*width+(i+1) ] ) / 9;}}}

简单的从1...width-1来处理, 所以第一个和最后一个像素就简单的抛掉了, 如果只是简单的看看效果还是没有问题的。

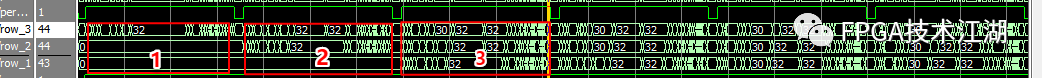

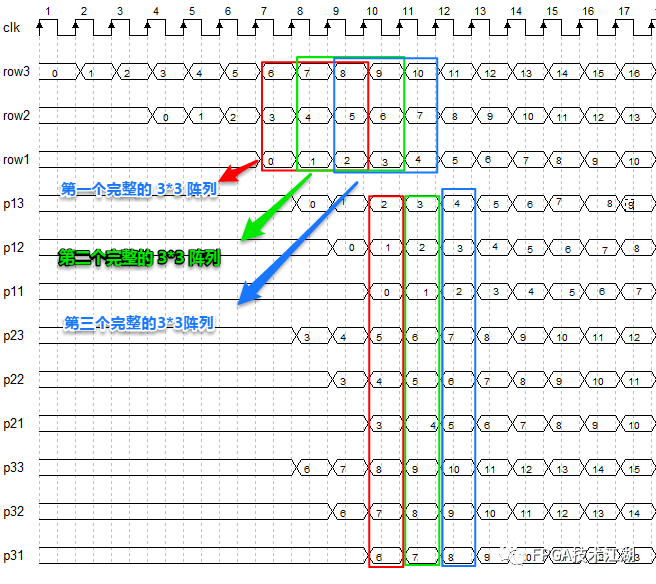

仿真波形如下 row_1 , row_2 , row_3 是指图像的第一、二、三行的数据,Per_href 是行有效信号(受VGA时序的启发,从 rom 中读取数据时设计了行有效和场有效的控制信号,事半功倍,有了利于仿真查错和数据的控制)。从 3 开始就出现了3*3 的像素阵列,这时候就可以求取周围 8 个像素点的平均值,进行均值滤波。

核心代码如下:

reg [5:0]p_11,p_12,p_13; // 3 * 3 卷积核中的像素点reg [5:0]p_21,p_22,p_23;reg [5:0]p_31,p_32,p_33;reg [8:0]mean_value_add1,mean_value_add2,mean_value_add3;//每一行之和always @(posedge clk or negedge rst_n)beginif(rst_n==1'b0)begin{p_11,p_12,p_13} <= {5'b0,5'b0,5'b0} ;{p_21,p_22,p_23} <= {15'b0,15'b0,15'b0};{p_31,p_32,p_33} <= {15'b0,15'b0,15'b0};endelse beginif(per_href_ff0==1&&flag_do==1)begin{p_11,p_12,p_13}<={p_12,p_13,row_1};{p_21,p_22,p_23}<={p_22,p_23,row_2};{p_31,p_32,p_33}<={p_32,p_33,row_3};endelse begin{p_11,p_12,p_13}<={5'b0,5'b0,5'b0};{p_21,p_22,p_23}<={5'b0,5'b0,5'b0}{p_31,p_32,p_33}<={5'b0,5'b0,5'b0}endendendalways @(posedge clk or negedge rst_n)beginif(rst_n==1'b0)beginmean_value_add1<=0;mean_value_add2<=0;mean_value_add3<=0;endelse if(per_href_ff1)beginmean_value_add1<=p_11+p_12+p_13;mean_value_add2<=p_21+ 0 +p_23;mean_value_add3<=p_31+p_32+p_33;endendwire [8:0]mean_value;//8位数之和wire [5:0]fin_y_data; //平均数,除以8,相当于左移三位。assign mean_value=mean_value_add1+mean_value_add2+mean_value_add3;assign fin_y_data=mean_value[8:3];

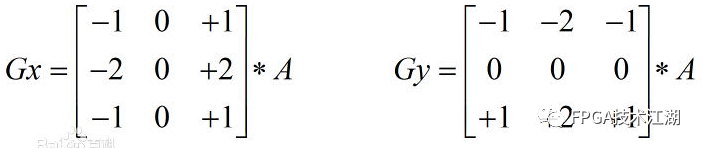

代码如下:

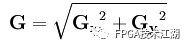

reg [8:0] p_x_data ,p_y_data ; // x 和 y 的正值之和reg [8:0] n_x_data ,n_y_data ; // x 和 y 的负值之和reg [8:0] gx_data ,gy_data ; //最终结果always @(posedge clk or negedge rst_n)beginif(rst_n==1'b0)beginp_x_data <=0;n_x_data <=0;gx_data <=0;endelse if(per_href_ff1==1) beginp_x_data <= p_13 + (p_23<<1) + p_33 ;n_x_data <= p_11 + (p_12<<1 )+ p_13 ;gx_data <= (p_x_data >=n_x_data)? p_x_data - n_x_data : n_x_data - p_x_data ;endelse beginp_x_data<=0;n_x_data<=0;gx_data <=0;endendalways @(posedge clk or negedge rst_n)beginif(rst_n==1'b0)beginp_y_data <=0;n_y_data <=0;gy_data <=0;endelse if(per_href_ff1==1) beginp_y_data <= p_11 + (p_12<<1) + p_13 ;n_y_data <= p_31 + (p_32<<1) + p_33 ;gy_data <= (p_y_data >=n_y_data)? p_y_data - n_y_data : n_y_data - p_y_data ;endelse beginp_y_data <=0;n_y_data <=0;gy_data <=0;endend//求平方和,调用ip核开平方reg [16:0] gxy; // Gx 与 Gy 的平方和always @(posedge clk or negedge rst_n)beginif(rst_n==1'b0)begingxy<=0;endelse begingxy<= gy_data* gy_data + gx_data* gx_data ;endendwire [8:0] squart_out ;altsquart u1_altsquart ( //例化开平方的ip核.radical (gxy),.q (squart_out), //输出的结果.remainder());//与阈值进行比较reg [15:0] post_y_data_r;always @(posedge clk or negedge rst_n)beginif(rst_n==1'b0)beginpost_y_data_r<=16'h00;endelse if(squart_out>=threshold)post_y_data_r<=16'h00 ;elsepost_y_data_r<=16'hffff ;end

代码如下:

integer w_file;initialw_file = $fopen("data_out_3.txt"); //保存数据的文件名always @(posedge clk or negedge rst_n)beginif(flag_write==1&&post_href==1)//根据自己的需求定义$fdisplay(w_file,"%b",post_y_data);end

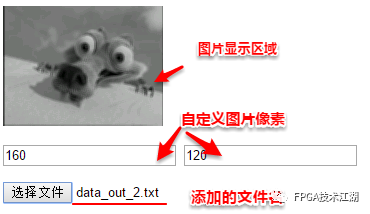

网页的界面如下,将参数设置好以后就可以显示图片。

下载链接:

链接:https://pan.baidu.com/s/1pwkJHtAxVHWWijSLczH0Ng

提取码:e87j

- THE END -

往期精选

FPGA技术江湖广发江湖帖

无广告纯净模式,给技术交流一片净土,从初学小白到行业精英业界大佬等,从军工领域到民用企业等,从通信、图像处理到人工智能等各个方向应有尽有,QQ微信双选,FPGA技术江湖打造最纯净最专业的技术交流学习平台。

FPGA技术江湖微信交流群

加群主微信,备注姓名+学校/公司+专业/岗位进群

FPGA技术江湖QQ交流群

备注姓名+学校/公司+专业/岗位进群