serdes相关基础知识

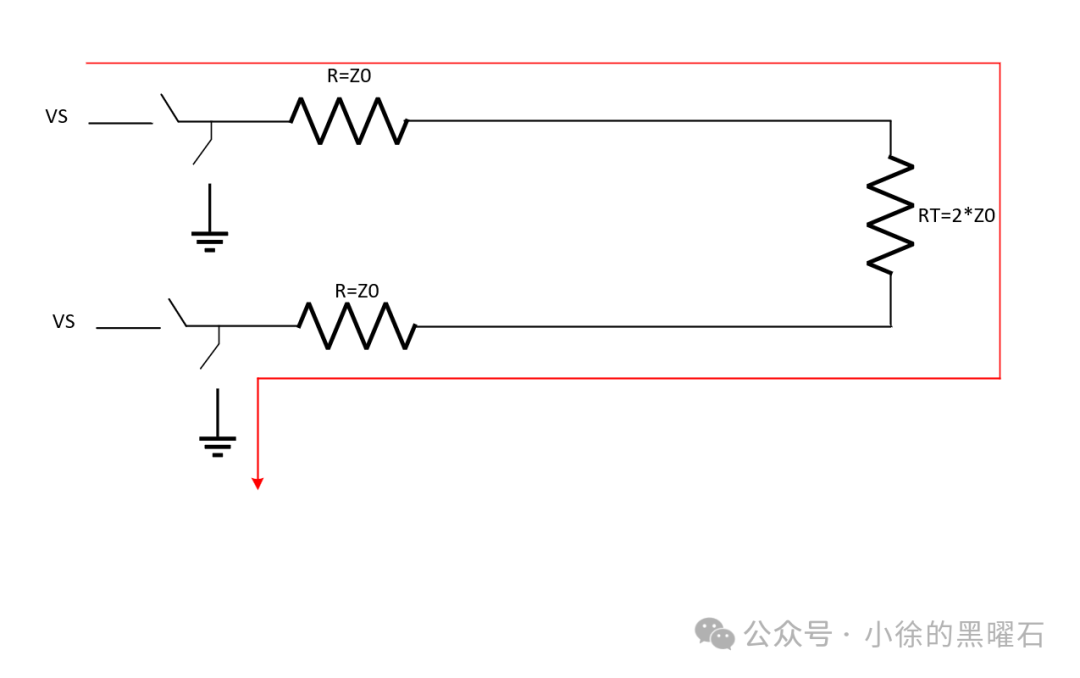

而电压模的差分接口如下图所示,驱动源为固定的Vs电压,RT为RX端的端接电阻,Z0为驱动器的输出阻抗,可以计算出流经电路的电流为:

I=Vs/(2*Z0+RT)

RX端的差分摆幅Vdpp为:

Vdpp=I*RT

通过上面的公式很容易推算出,只有当RT=2*Z0时,才可以得到最大的电压摆幅VS。

FFE均衡的基本概念

均衡是在高速串行互连中改善信号质量,减少误码率的重要措施,在TX端的均衡主要是FFE(前向反馈均衡),FFE的基本原理是基于发送端的信号本身出发。

我们知道信道对信号的影响主要有两点:

1、对信号的不同频率成分有不同的衰减,频率越高,衰减也越大

2、信号中不同频率的传输速度不同,频率越高,传播速度越快,会产生“色散”现象。

既然serdes本身传输的就是数字信号,所以FFE的目标就是在发送端就优化数字信号的频谱特征,通常是利用FIR数字滤波器来实现信号的高通滤波,通过调整FIR滤波器各个抽头的系数来改变滤波器的频响特性。

3.1、SST驱动器的基本原理

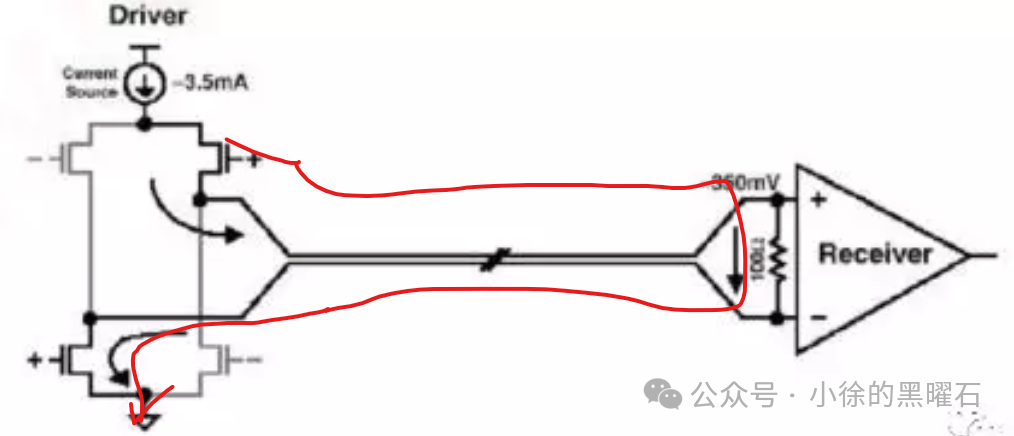

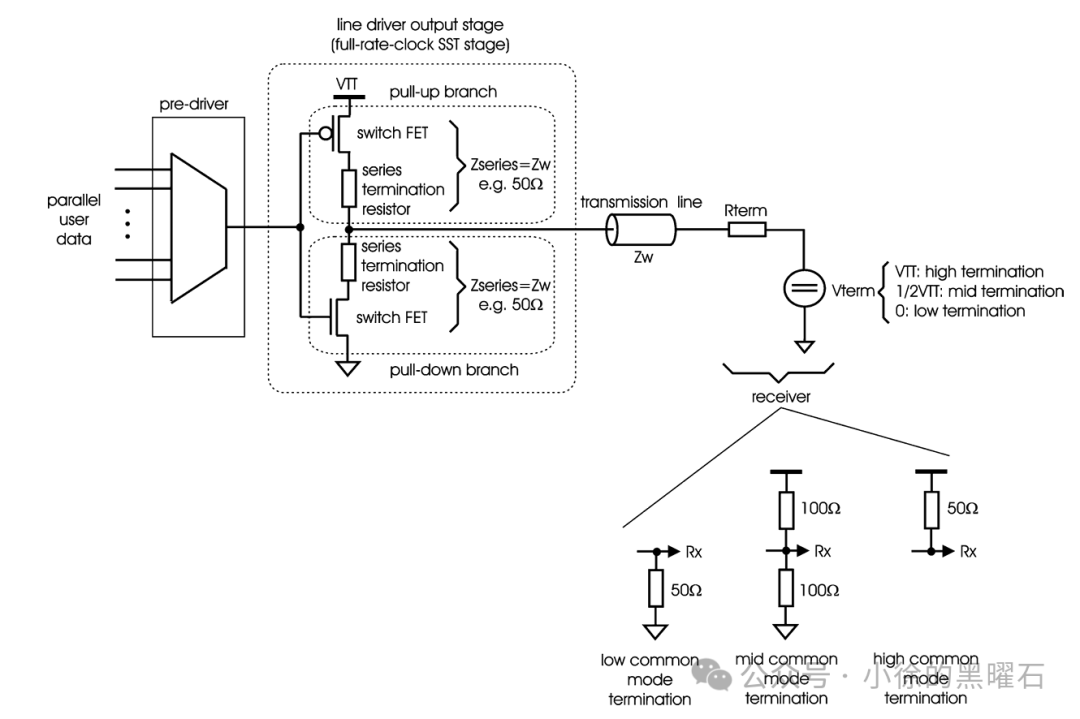

在高速serdes数据传输中,应用最广泛的接口之一就是CML接口,主要原因是因为其可以支持比较高的速率,而且对电源噪声的敏感性也相对比较低,但是也伴随着一些缺点,比如功耗比较高,而且也无法支持不同的DC端接电压,因此发展出了SST,可以很好的克服CML接口的缺点,在支持比较高的信号摆幅的同时,还可以支持不同的端接电压,而且功耗对比CML接口也更低。

SST发射器的基本架构如上图所示,输出级被细分为pull-up和pull-down两条支路,pull-up支路由PMOS开关管实现,pull-down由NMOS开关管实现,每条支路都串接有串联的端接电阻来保持和传输线的阻抗相匹配。

如前面所说,SST的优势之一就是可以支持不同的DC端接电压,上面的架构图中也展示出low VCM、Mid VCM、high VCM三种场景下的RX 端接。

上面的架构显示的是单端SST,在RX端阻抗匹配的情况下,因为源端串联阻抗和RX端接的分压,信号摆幅将是供电电压VTT的一半(实际中会有一点差异,因为FETs会占用一部分的voltage headroom)。

3.2、SST发射器的阻抗匹配

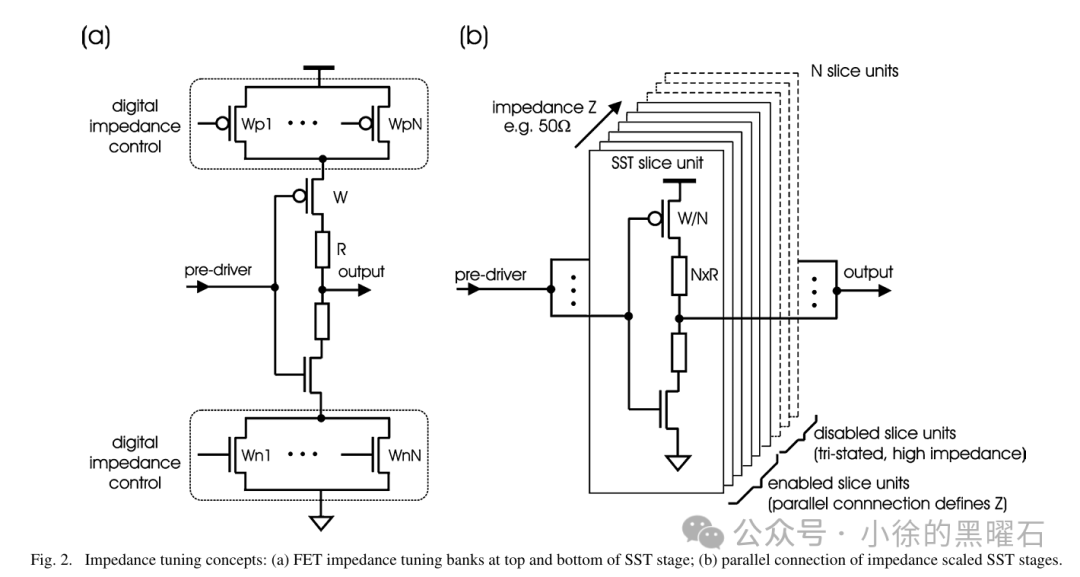

为了解决因为工艺偏差导致的阻抗不匹配问题,SST发射器的阻抗被设计为可调的,阻抗调谐方案主要有两种(如上图所示)。

在上图(a)中,一组二进制加权控制的FETs串联在pull-up和pull-down分支的顶部和底部,利用这些FETs的等效阻抗来进行阻抗调谐,其缺点就是额外增加的FETs会限制可用的voltage headroom(即降低部分摆幅),如果优化此问题的话,则需要在开关管的宽度上进行补偿。

另外一种方案如图(b)所示,其方案是将原来的驱动器的阻抗进行缩放后(即单个slice unit串接的阻抗为N*R,N个并联的阻抗即为R),将N个同样的驱动器进行并联的方案,每单个驱动器我们称之为slice unit。

在上述方案(b)中,如果驱动器输出阻抗偏小,则可以禁用掉一些slice unit来提高输出阻抗,该方案的优势就在于slice unit可以设计的更加的简单,阻抗的调谐也更容易,而且也没有voltage headroom问题。

将驱动器划分为不同的slices也允许发射器进行amplitude margin,因为在已经使能的输出slices中,单个slices可以被配置静态的pull-up或者pull-down,这一特性很有用,比如系统启动后,可以决定发射多大电平的信号;amplitude margin 并不会影响到输出阻抗,只是静态的slices取代了动态的slices,产生的改变只是信号摆幅,而不是阻抗。

3.2、SST发射器的均衡

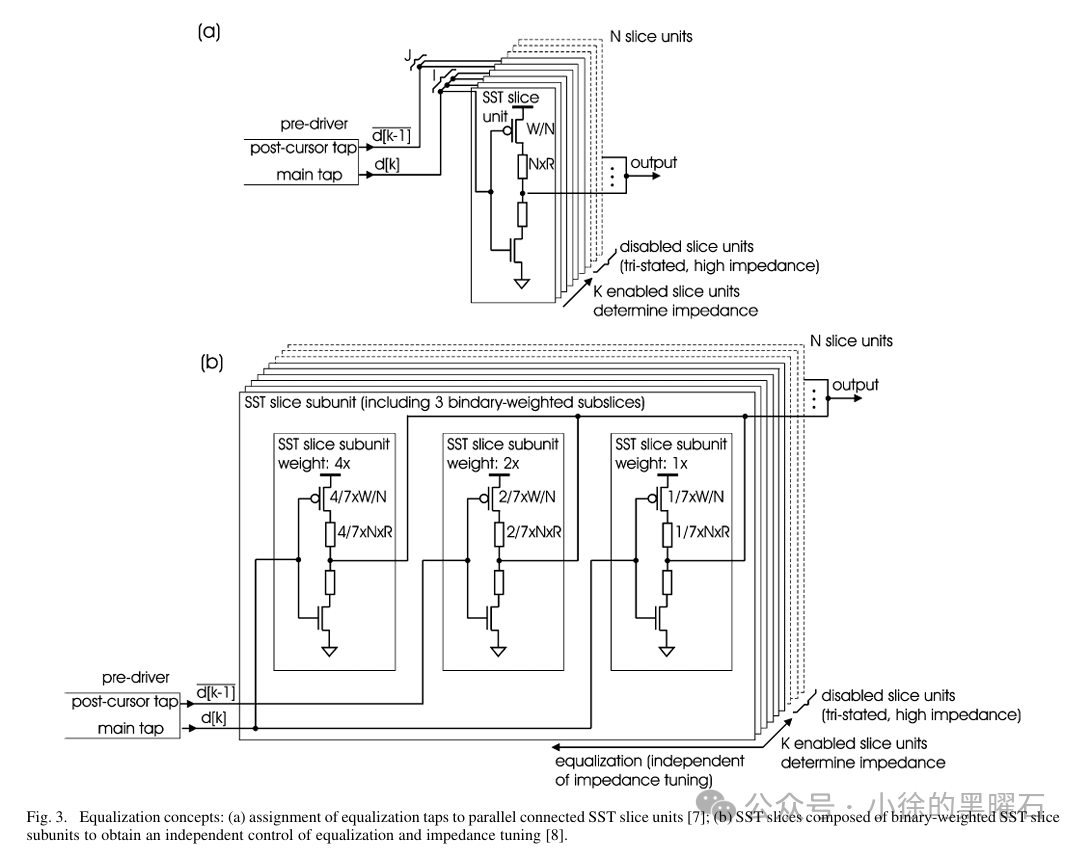

除了提供阻抗匹配之外,一般serdes发射器还需要提供合适的信道均衡能力,而在SST中主要有两种TX FFE方案,详细的架构图如下所示。

在上图方案(a)中,所有的slice uints都是相同的,该架构实现了一个2-tap的均衡器(main-cursor和post cursor),我们假设将N片slice uints中的K片slice uints并联来实现传输线的阻抗匹配,为了实现2-tap的均衡,将K片slice uints中I片给main cursor,J片slice uint给post cursor,需要注意此处:

I+J=K

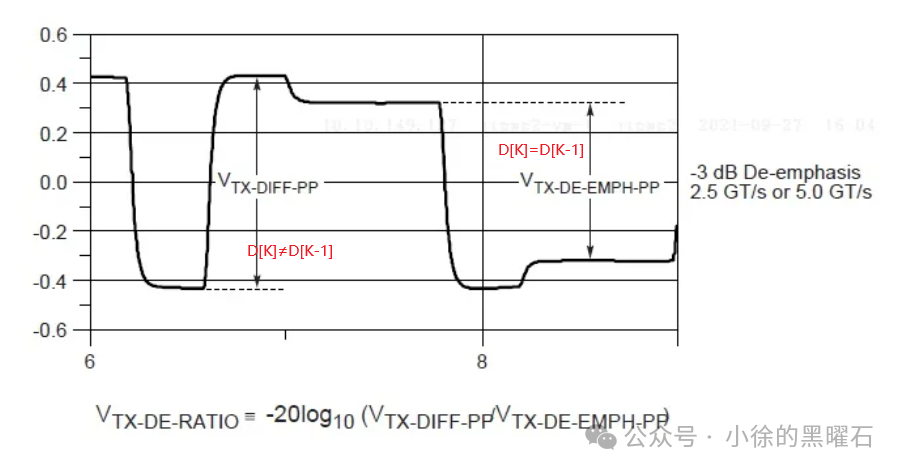

假设K=8,I=6,J=2,则可以计算出来当FFEVpp=VTT*1/2

则可以实现大约6dB的均衡(如何计算均衡可以参考下图)

备注:main cursor为d[K],post cursor为1-bit-delayed且取反之后的d[K-1]

该架构的缺点在于发射器的输出阻抗不能独立的进行调谐,因为改变了并联的slice units的数量也会影响到已经分配的main cursor和post cursor,比如在上面实现6dB均衡的例子中,假设为了阻抗匹配需要新增4个使能的slice uints,则K新增4达到12个,I必须新增3个,J必须新增1个来维持6dB的均衡(即I+J=K,I/J=3),但是当假设K需要新增5个时,则无法保证上述的比例关系。

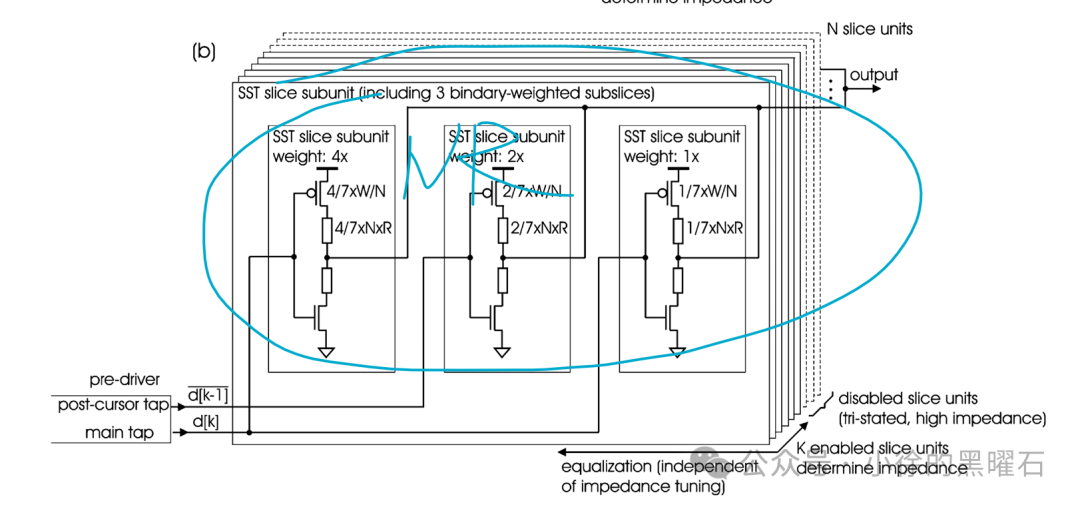

在方案(b)中则将阻抗匹配和均衡实现了解耦,克服上面的问题,如方案(b)中的架构所示,发射器中的架构包括了N个相同的slice units,K个slice uint并联在一起实现目标的阻抗匹配,和方案(a)相反的是,独立的slice uints有三个binary-scaled SST驱动器,可以实现的幅度调节steps为Vpp/(2^3-1)。

以方案(b)中抽头系数进行分配,将最大和最小的权重给main cursor,中间的权重给post cursor,按照前面介绍过的计算方法,可以计算出这样的分配可以实现7.4dB的均衡。