芝能智芯出品

芝能智芯出品JEDEC(标准组织)正式发布了GDDR7 DRAM的规范,这是专为显卡和其他GPU驱动设备设计的最新一代内存。

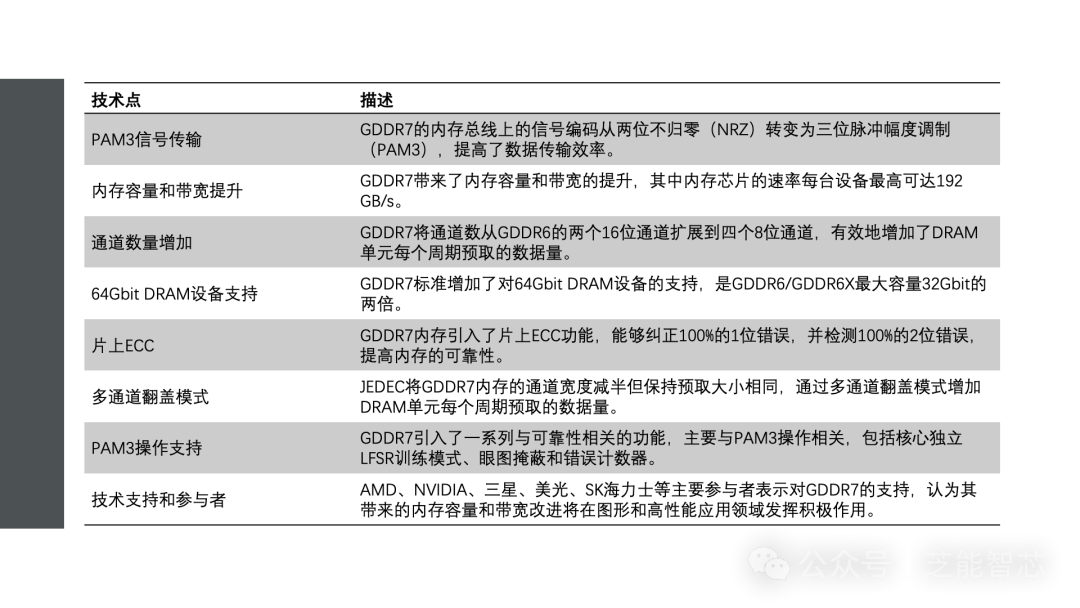

GDDR7通过从两级非归零(NRZ)编码转向三级脉冲幅度调制(PAM3)信号传输,引入了增加内存容量和带宽的组合。GDDR7标准的显著变化包括更高的数据传输速率,每个DRAM芯片通道数量的增加,新接口训练模式的添加,以及引入片上纠错码(ECC)以确保内存可靠性。转向PAM3编码使GDDR7能够在两个周期内传输三位数据。

JEDEC电子设备工程师协会在三月初发布了GDDR7 DRAM的官方规范,为显卡和其他GPU驱动设备提供了最新的内存标准。这一新一代的GDDR(图形双数据率)内存带来了内存容量和内存带宽的增益,主要通过内存总线上的PAM3信号驱动实现。

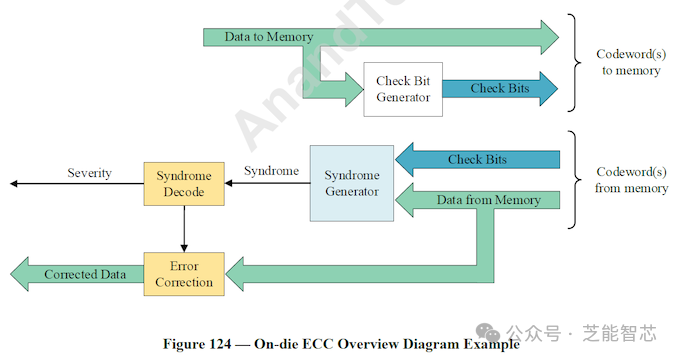

此外,新的图形RAM标准还增加了每个DRAM芯片的通道数量,引入了片上ECC(错误纠正码),以提高内存的可靠性。

GDDR7已经在过去几年中进行了开发,约一年前,JEDEC成员首次披露了这项内存技术。根据发布的规范,GDDR7的最大技术变化在于内存总线上的信号编码从两位不归零(NRZ)转变为三位脉冲幅度调制(PAM3)编码。

这种变化使得GDDR7能够在两个周期内传输3位数据,相比之下,以相同时钟速度运行的GDDR6在相同时间内只能传输两位数据,提高了50%的数据传输效率。

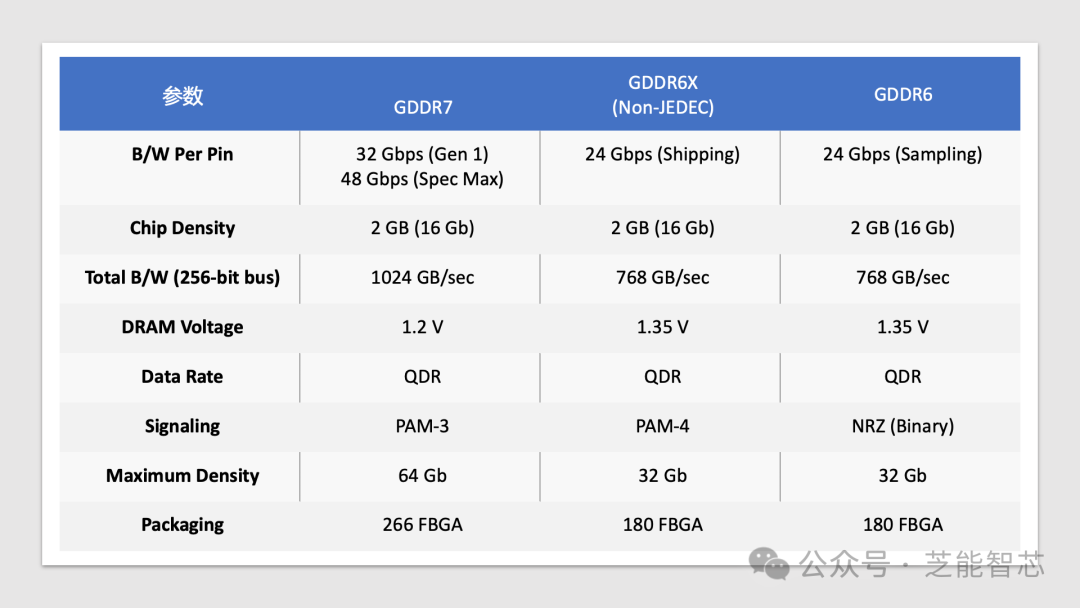

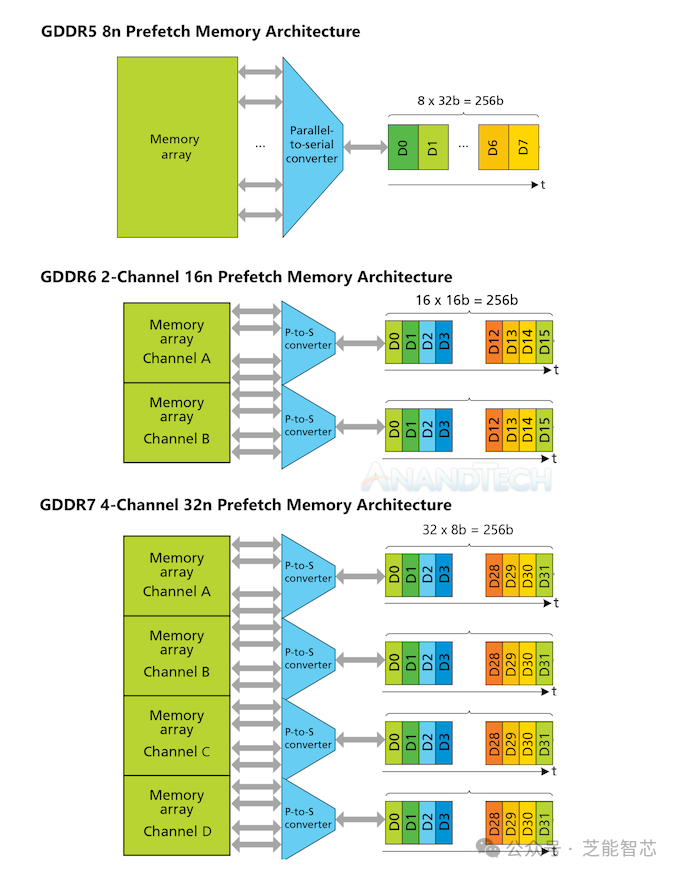

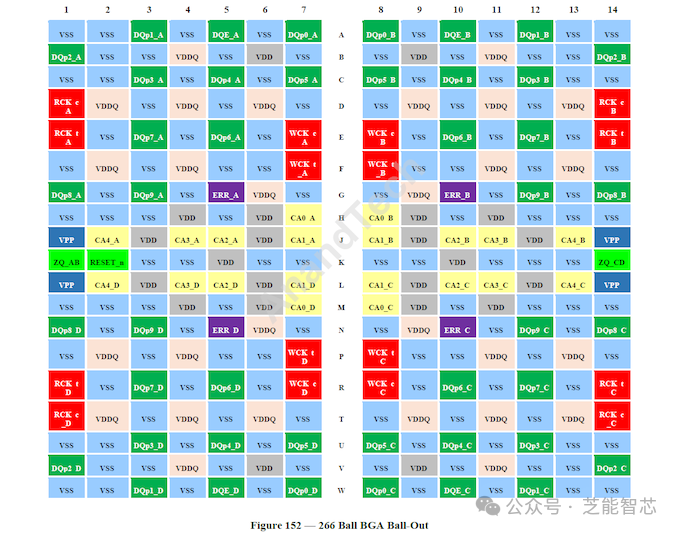

GDDR7的第一代预计将以每个引脚32 Gbps左右的数据速率运行,但标准本身为更高的数据速率(最高48 Gbps/pin)留有余地。JEDEC表示,GDDR7内存芯片的速率每台设备最高可达192 GB/s。此外,规范还将单个32位GDDR内存芯片细分为更多数量的通道,从而有效地增加了DRAM单元每个周期预取的数据量。

一个显著的变化是在内存芯片的通道数量上,GDDR7将通道数从GDDR6的两个16位通道扩展到四个8位通道。这一变化对于最终用户来说影响较小,但对芯片内部的工作方式产生了重大影响。JEDEC将每通道的预取保持在256位,使GDDR7成为32n预取设计。

GDDR7标准增加了对64Gbit DRAM设备的支持,是GDDR6/GDDR6X最大容量32Gbit的两倍。规范还引入了片上ECC功能,用于提高内存的可靠性,可以纠正100%的1位错误,并检测100%的2位错误。此外,规范还包括对内存错误的信息提供以及对PAM3操作的支持。

三星电子和SK海力士计划在今年上半年量产下一代显卡用内存GDDR7 DRAM,这是用于图形处理单元(GPU)的最新一代高性能内存。

GDDR7 DRAM将在美国加利福尼亚州的IEEE国际固态电路会议上亮相,其中三星的16Gb、37Gbps GDDR7 DRAM被宣称是世界上最快的,采用PAM3信号技术,相较于以往的NRZ方法,能够在相同信号周期内传输更多数据。

SK海力士也计划在同一次会议上展示其16Gb、35.4Gb/s GDDR7内存。这种高速内存预计将在Nvidia和AMD的下一代GPU中投入使用,并在今年年底前量产。GDDR7 DRAM的推出有望继续巩固韩国在半导体行业的领先地位。

小结:内存领域的竞争,在持续延续。