本文简介

主要内容

什么是LDO的压降?

LDO的压降如何产生?

如何降低LDO的压降?

领取资料:关注并后台回复:粉丝群

正文

什么是压降?

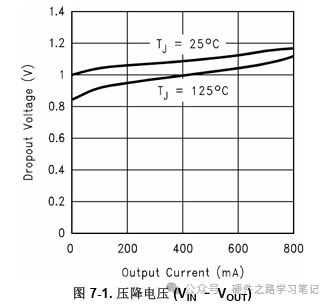

压降电压 Vdrop 是指为实现正常稳压,输入电压 VIN 必须高出所需输出电压 VOUT的最小压差。

压降在数据手册中如何体现?

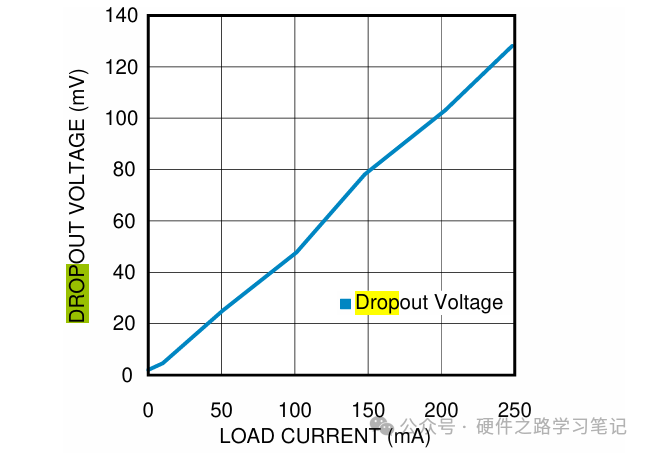

而TI的LP5907作为超低压降LDO,其Vdop曲线如下图,在其满负载250mA时其压降也仅仅为130mA,适合在低压场合使用。

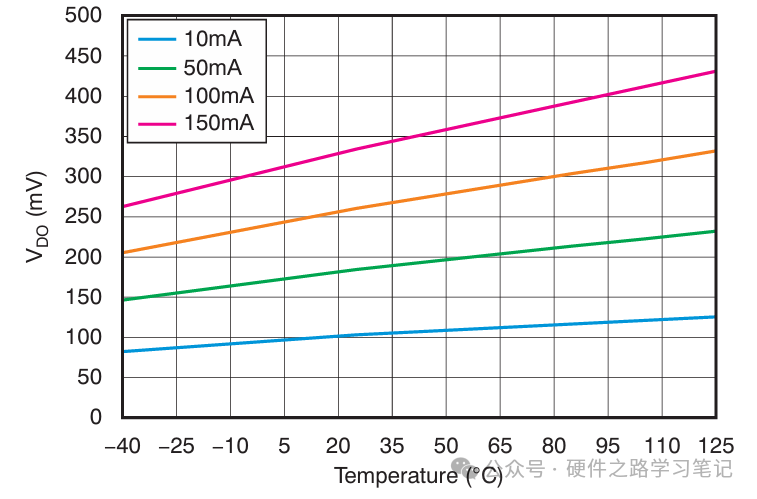

此外,还有其他因素影响压降,如下图,相同负载下,温度越高,压降Vdrop越大。

决定压降的因素是什么?

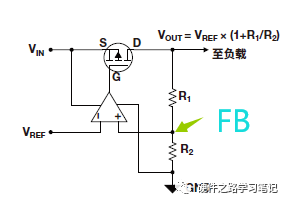

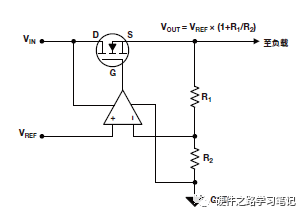

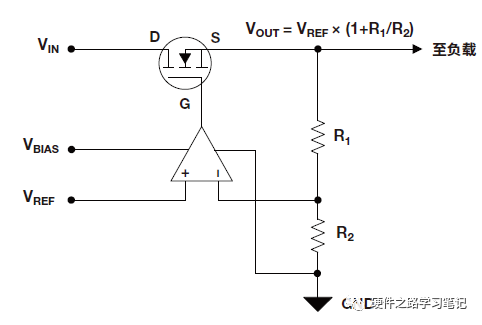

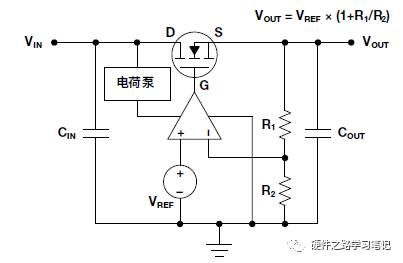

LDO是如何尽量降低压降的

了解了NMOS和PMOS型LDO的控制逻辑后我们可以轻易得出降低Vdrop的方法-增大|Vgs|,以NMOS型LDO为例,除了选取低Vgs的MOS以外,同种MOS的情况下,由于Vs=VIN,这个设计时无法控制,因此LDO设计者可以通过增大Vg来增大Vgs,一般有以下两种方法。

关注个人公众号:硬件之路 学习笔记 阅读更多文章

文章推荐

公众号主页菜单栏中有分类整理的文章,欢迎查看。

微信号:yjzlxxbj

CSDN:硬件之路学习笔记

扫码加群领取资料

多一个点 在看

多一条小鱼干