运算放大器电路魅力无穷。采用运算放大器构建优雅的反馈应用,是吸引我投身电子设计行业的初衷。仿真作为一种直观展示电路性能的方式,是研究反馈思路和培养运算放大器电路直觉的理想工具。

然而,运算放大器电路的仿真却也带来令人痛心的讽刺:尽管IC设计工程师在运算放大器的设计中几乎不可避免地要用到SPICE,但在一些更大的应用电路中,使用SPICE来仿真最终的运算放大器却十分困难;或者至少比我想象的困难得多。本文旨在解决这一问题,希望能够为运算放大器建模提供一个一劳永逸的解决方案。问题的关键在于:SPICE在晶体管级别的仿真方面表现出色;然而,IC设计工程师要尽一切可能,让人难以分辨运算放大器中是否存在晶体管。他们希望您能够使用运算放大器手册为设计提供参考,并且不会因为晶体管的限制而偏离理想的运算放大器性能。而当您意识到SPICE中没有任何原生电路元件的性能与运算放大器相似时,这种讽刺意味就更加明显。搭建一个模拟运算放大器的模型困难重重,要么可能比原始的晶体管级别模型实现更难求解,要么会因过于简化而失去实用价值;这是一个技术难题。并且,IC制造商并没有理由了解如何在应用层面对运算放大器建模——因为这根本不是运算放大器设计过程的一部分。这就使制造商陷入了尴尬的境地。他们的客户要求获得适用于电路设计的模型,但制造商通常不具备必要的建模专业知识。此外,各方利益的冲突也使得情况进一步复杂。制造商希望突出展示其运算放大器产品的差异化优势,如更低的偏移和更高的电源抑制比(PSRR)。然而,他们在进行这种展示时,并未考虑到设计流程是否能实现最佳设计。由于运算放大器制造商缺乏建模方面的专业知识,他们通常选择与具有专门侧重点的建模咨询承包商合作。承包商倾向于重复利用他们的专有模板电路,并仅根据主极点、相位裕度、输出电压范围等关键要素进行调整。该模板采用称为“contraptous”的方法,只使用最简单和最常见的SPICE基本组件来实现。这种方法对咨询师而言颇为有利,因为其不必为不同的IC制造客户定制不同的模型;同时这些模型也经得起委员会的审查,因为它们只使用所有SPICE程序共有的功能。然而,此类模型的模板通常是在对SPICE求解器工作原理缺乏详细了解的情况下编写的,这导致模型在从一个仿真环境迁移到另一个仿真环境时,无论如何都需要进行再次调整。显然,这种基于现有技术最低共同点的解决方案并非最佳实践。这些相互竞争的方法导致了复杂的运算放大器模型;此类模型既不正确,又难以在大型电路中求解。首先,让我们来探讨其不正确的原因。以偏移电压为例;制造商期待模型能够展示其运算放大器在偏移电压和偏置电流方面优于其它公司的产品,并希望模型能够展示一个典型的偏移值。但实际上,IC设计人员作为有责任心的专业人士,会尽可能地消除偏移。在整个生产过程中,有些器件会有正偏移,有些具有负偏移。除非产品设计本身存在错误,否则不会出现系统性偏移。但是,制造商为了强调产品差异化,会要求模型显示系统偏移电压。对于这种仅仅为了突出差异化而建立的模型,问题在于,如果优化设计时需要运算放大器来调节,那么得到的优化点并不正确;并且以模型的偏移电压为中心还会导致最坏情况下的误差加倍。您完全可以跳过仿真,直接参考运算放大器手册中的设计方法,选择成本更低的运算放大器,并获得更佳的电路性能。这个问题还延伸到运算放大器建模的其它方面。例如PSRR。IC设计人员在设计过程中也尽可能地将其消除。有时,其幅度可能是已知的(至少从对数尺度可以看出),但相位信息却未知。我从未见过将PSRR表示为复数的数据表。偏移和PSRR不以真实平均值为中心的错误,对于使用多个运算放大器的电路来说尤为严重。我无法想象拥有多个具备相同偏移和PSRR的运算放大器是多么奢侈。从更深层次上讲,这些方法之所以会导致运算放大器建模出现如此严重的问题,是因为这些模型通常得不到熟悉仿真设计流程人员的支持。IC制造商的应用工程师抱怨,客户不会观察输入共模范围之类的参数,却要求对其“建模”。然而,就设计流程而言,如果在没有模拟输入共模范围的情况下进行仿真,然后在电路运行过程中检查是否超出输入共模范围,通常更为合理。这与击穿电压的处理方式类似;除非设备属于雪崩级(即在部署时会安全击穿),否则最好不要在仿真中包含击穿电压,而是让电压自由变化,并让仿真设备承受一切可能的问题。待仿真完成后再审核结果,以查看是否有超过额定电压的情况。否则,就很难知道是否发生了击穿;设计流程甚至可能会产生一个在某些器件烧毁冒烟后才起作用的设计。上述段落包含了一个争议点:IC制造商的应用工程师可能会轻视客户的设计能力。这也是人之常情,因为一个只负责支持自己IC项目的人,自然很容易对那些不太熟悉这些IC的用户评头论足。但在某种程度上,我们必须认识到,这些IC制造商的应用工程师并不会像他们的客户那样购买大量在公开市场流通且必须在竞争中生存下来的元器件。出于这个原因,从最终分析来看,我并不认为客户比自己更笨,甚至于我可能最终都找不到比我更笨的人了。我所编写的每一个仿真器都是为了让人们感觉自己很聪明,让他们能够使用工具来培养对所设计电路的理解。

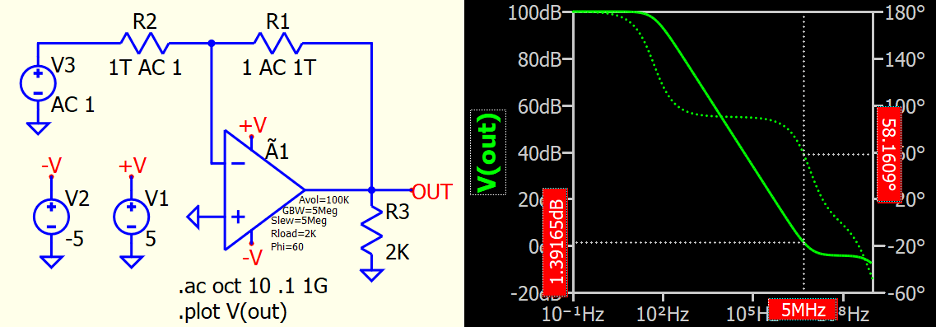

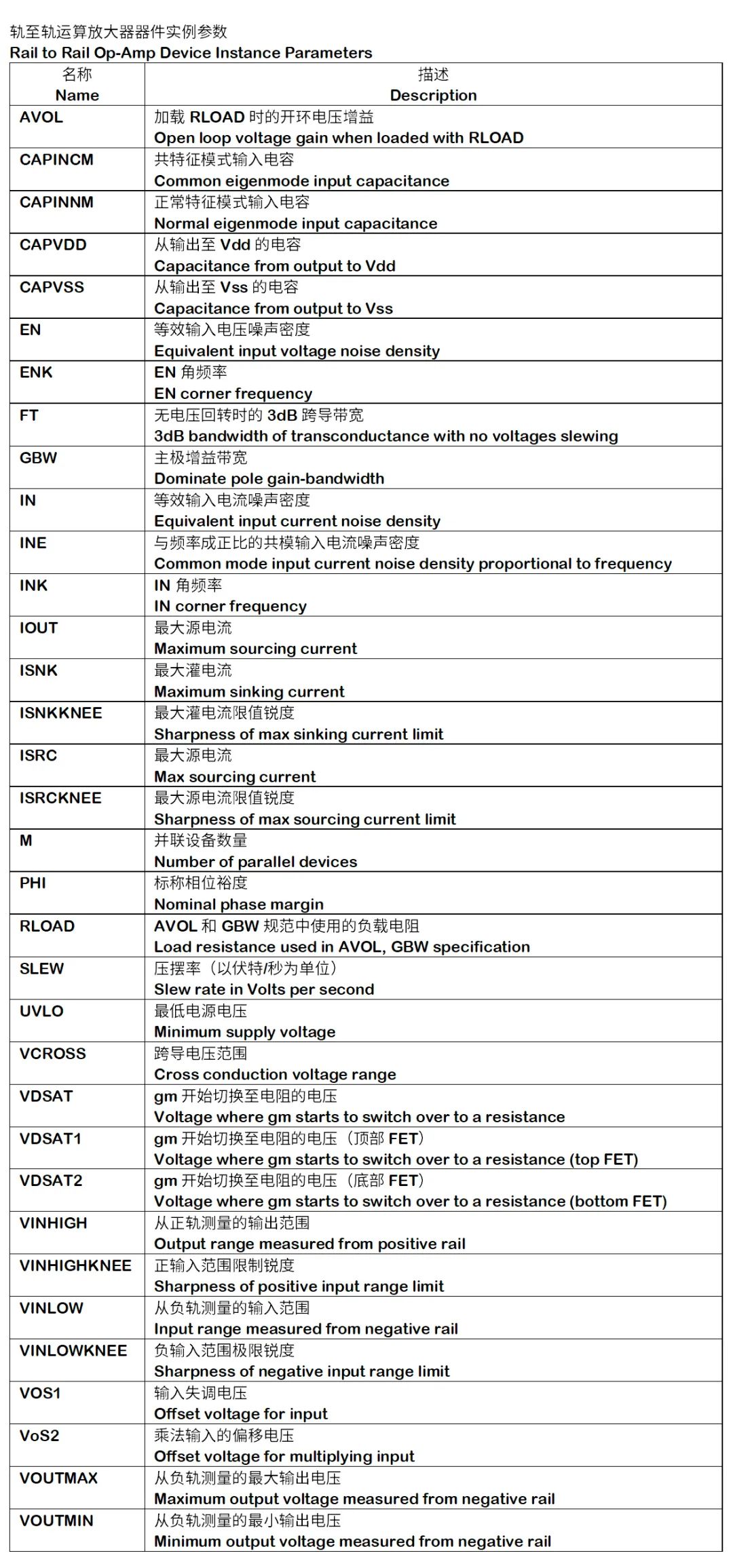

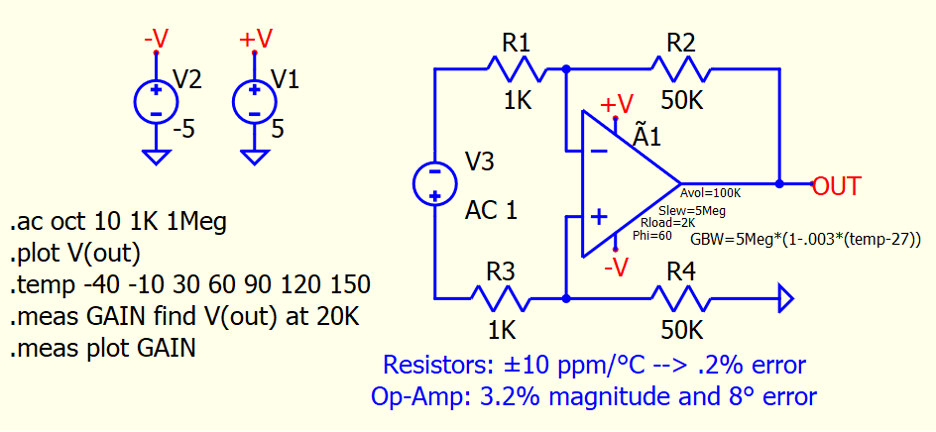

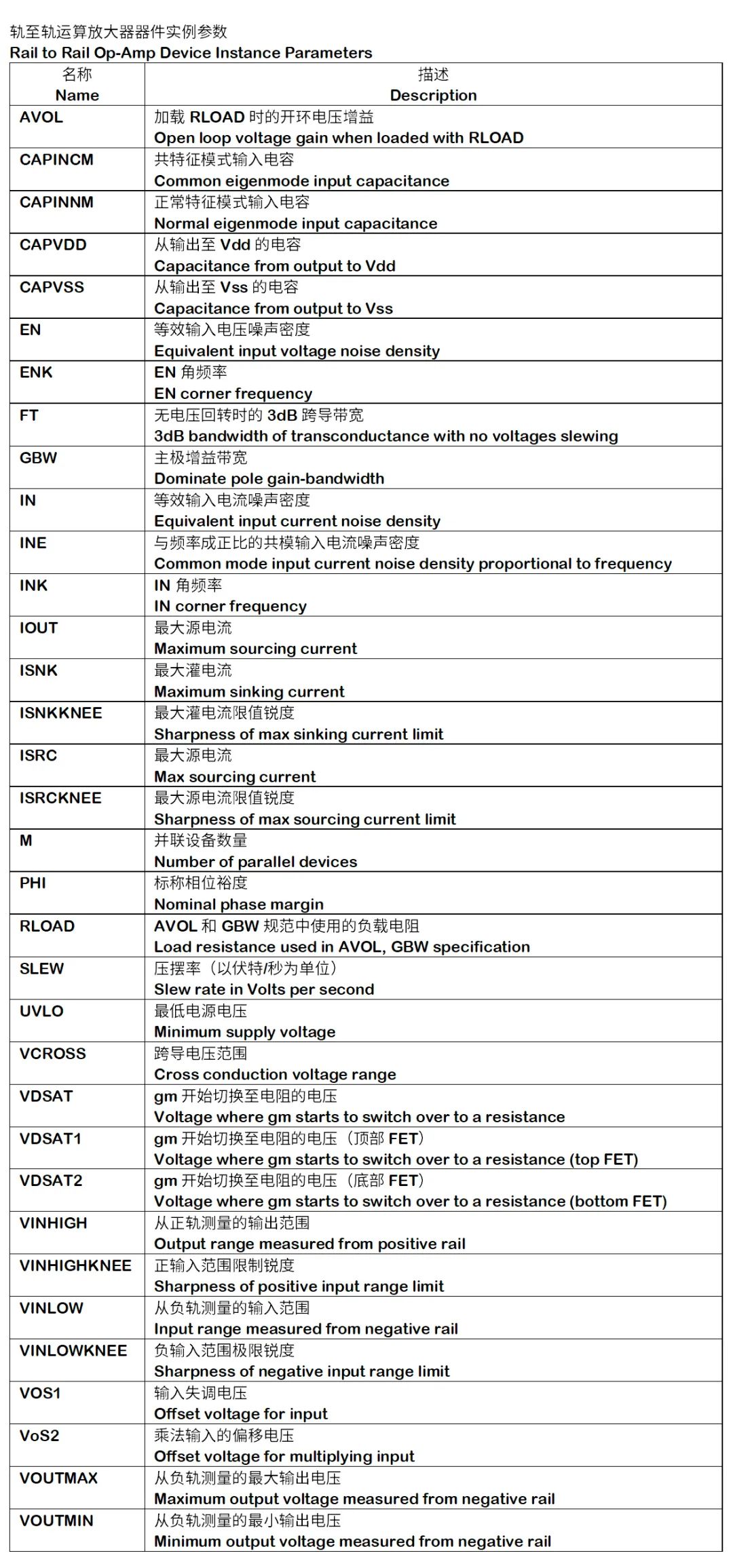

说了这么多,让我们回归主题。为了简化运算放大器建模,QSPICE包含了一个全新的原生电路元件。它作为一个跨导,从电源轨获取电流(而不是神奇地作为自己的电源运行);当输出接近电源轨时,它会像满足平方律关系的FET一样转换为电阻。其功能与轨至轨输出(RRO)运算放大器精心设计的互补接地源输出级类似。内部补偿RRO运算放大器的常见拓扑结构包括一个从该输出到内部节点的米勒倍增电容。这种拓扑结构也是QSPICE中一个原生电路元件。本仿真演示了如何提取QSPICE RRO运算放大器原生电路元件的开环响应:R1的值是“1 AC 1T”。这意味着对于直流解决方案,它表现为1Ω的电阻;但从交流角度分析,它呈现为1e12Ω的电阻。相反,R2在直流解决方案中为1e12Ω的电阻,而从交流角度分析则成为1Ω的电阻。针对交流和直流使用不同阻值的功能源自HSPICE,并且常作为电压跟随器来用于求解偏置点,之后直接在开环中进行交流分析。实例参数Avol、GBW、Slew和Phi分别表示开环电压增益、增益带宽、压摆率和相位裕度。由于RRO具有高阻抗输出,电压增益基本上可达到无限大。这就是为什么需要引入参数Rload来指定用于测量开环电压增益的负载阻抗。我们可使用简单推导的方程式来设置RRO运算放大器设备。在波形窗口中,光标设置为5MHz,但增益为1.4dB而非零,相移为58°而非60°。此时,我们可以调整实例参数GBW和Phi以匹配所需的运算放大器。RRO器件支持对完整运算放大器进行建模所需的所有参数:主极点、相位裕度、随机噪声、输入电容(包括正常和共模电容)、电压和电流输出能力等。以下是实例参数的完整列表:

另外,没错;您也可以直接为其设置一个偏移电压作为实例参数,以确定器件精度和散射的影响。

接下来让我来解释一下输入电容,即CAPINCM和CAPINNM。CAPINCM表示当两个输入同时驱动时的电容,而CAPINNM是差分驱动时的电容。这并不是输入端之间的电容,而是在正常模式稳定性分析中需要关注的电容。值得注意的是,一些IC制造商会错误地将数据表中引脚对引脚的电容列为正常模式电容。QSPICE RRO运算放大器器件解决了几个问题。其不仅让每个人都能通过简单的数值填写成为运算放大器建模专家,还确保了建模和未建模的部分完全透明,让您深入了解模型的运作。当然,除了强大的原生电路元件,QSPICE也支持快速、便捷地从第三方导入历经验证的各种模型,以帮助开发者减少重复工作量、实现更丰富的仿真功能。欢迎小伙伴们点击下方视频了解~

对于一些人来说,QSPICE RRO运算放大器设备的高速运算性能至关重要。求解电路所需的时间更多地取决于求解方程的数量,而非器件的数量。您可以通过在SPICE仿真中添加“.options acct”来确定求解电路所需的方程数量。因此,为计算运算放大器模型中的内部节点数,可以在一个空白原理图中放置一个模型实例,并将所有引脚接地。随后,运行任意仿真并检查控制台输出;输出应显示为“Circuit Equations: 2(电路方程:2)”,这意味着QSPICE的RRO运算放大器器件包含两个内部节点。相比之下,在通用工业运算放大器模型上进行的同样测试,通常需要40到150个方程。如果您只仿真几个运算放大器,这些并不重要,但当您将系统的其它部分用作运算放大器电路的测试矢量时,它便变得重要起来。

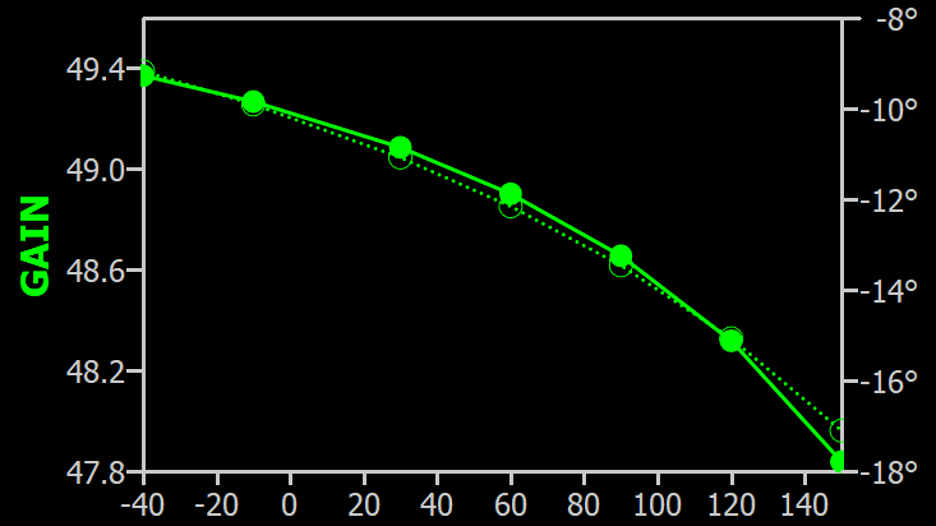

QSPICE的RRO运算放大器器件还让您能够研究电路在温度条件变化下的性能,而一般供应商提供的运算放大器模型则无法做到这一点。使用简单的电阻反馈网络时,相位偏移可能会先于幅度偏移发生,从而导致数据采集错误。我只是将GBW的值设定为一个包含其温度系数(tempco)的表达式。在信号调理过程中,运算放大器GBW的温度相关性可能引发的误差很容易超过无源元件因温度相关性而产生的误差。例如,指定25ppm/°C的电阻很简单;但假设我们选择10ppm/°C,则在-40°C到150°C的温度范围内会产生0.2%的误差。在这个仿真中我们可以看到,在假设20kHz的分析频率下(这种频率可能用于石油勘探等场景),幅值误差为3.2%,相位误差为8°。下图为增益随温度变化的曲线图,这里仅考虑了运算放大器GBW温度相关性的影响:

借助QSPICE的RRO运算放大器器件,您可以设计一个数据采集系统,并在石油勘探等应用中预测其在井下或地表的性能,无论地点位于北极还是非洲。