本文简介

主要内容

由于现在小体积设备如手表手环等越来越多,减小DC-DC模块体积也随之变得非常重要,因此本文将探讨如何才能尽量减小DC-DC芯片及其外围电路体积。

领取资料:关注并后台回复:粉丝群

正文

一、

影响DC-DC模块体积的因素

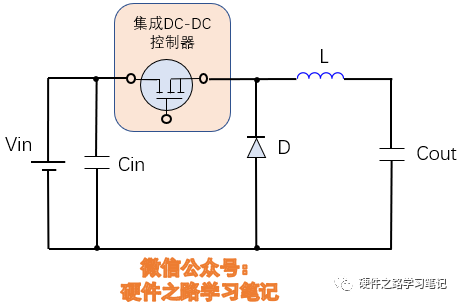

常见DC-DC(BUCK)拓扑结构

外围器件分析

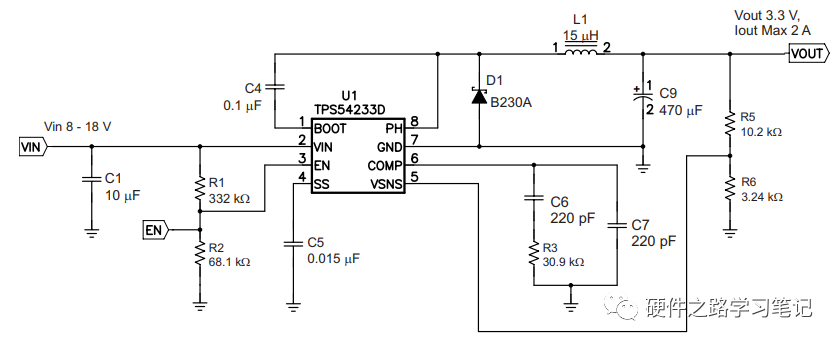

在如上图1所示的集成BUCK芯片的外围电路中,输入输出电容、二极管、电感均会影响整个DC-DC模块的体积。

二、

如何减小电感体积

电感体积与什么参数有关

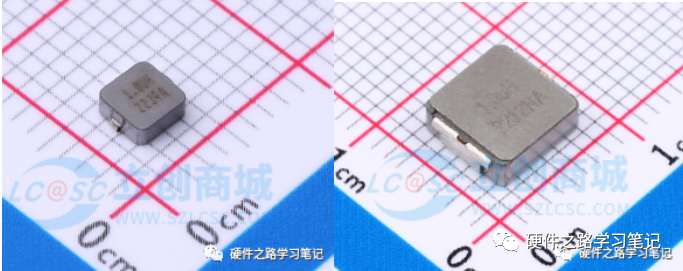

图2 1uH-2A(左)与10uH-2A体积对比(右)

图3 1uH-4A(左)与1uH-9A体积对比(右)

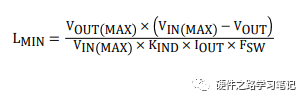

如何降低电感量

前述可知减小电感体积只有降低电感电流与减小电感量两种方法,而电感电流与输出负载电流有关,这个我们没办法减小,因此只能去减小电感量。

图4 电感计算公式

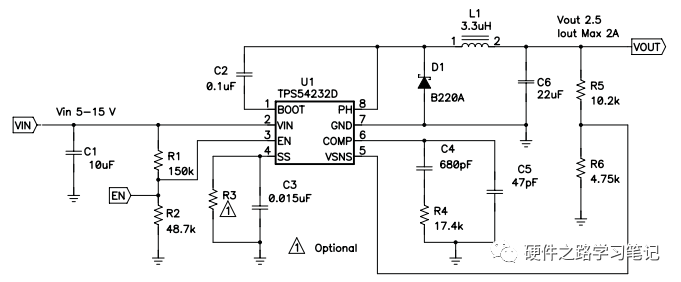

图5 TPS54332-1MHz 电感量3.3uH

图6 TPS54333-285kHz 电感量15uH

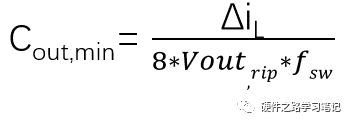

图7 输出电容计算公式

同时,如上图7的输出电容公式可以看出,输出电容容量也随开关频率的增大而减小,所以通过提高开关频率来减小体积是一举两得的方式。

但要知道的是,开关频率过高也不全是优点,过高的开关频率对EMC等可能有负面影响,同时高开关频率带来的损耗也更高,后续出文章介绍,欢迎关注。

三、

其他减小DC-DC模块体积的方法

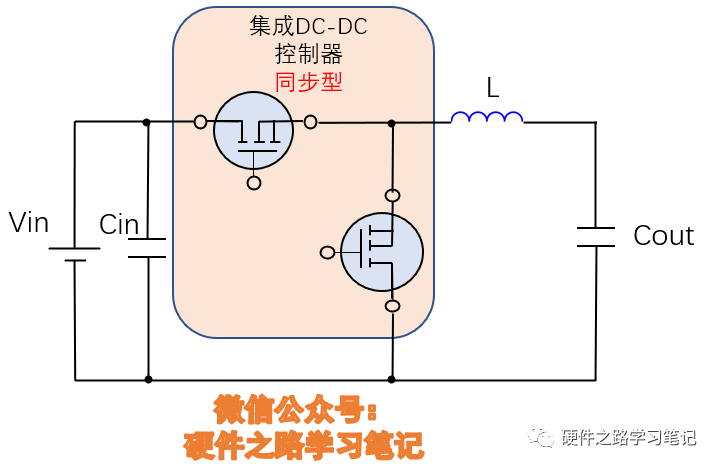

干掉二极管

图8 同步型DC-DC(BUCK)拓扑

从输入输出电容入手

为了滤除不同频段的杂波,通常输入输出电容都是并联多个,而在极端体积限制时,只要满足纹波等参数要求,可以减少输入输出电容数量;同理也可以通过减小其容值以缩小体积。

关注个人公众号:硬件之路 学习笔记 阅读更多文章

文章推荐

公众号主页菜单栏中有分类整理的文章,欢迎查看。

微信号:yjzlxxbj

CSDN:硬件之路学习笔记

扫码加群领取资料

多一个点 在看

多一条小鱼干