半导体的氧化有许多种方法,包括热氧化法、电化学阳极氧化法和等离子化学气相沉积法。

由于只有热氧化法可以提供最低界面陷阱密度的高质量氧化层,因此通常采用热氧化的方法生成栅氧化层和场氧化层。

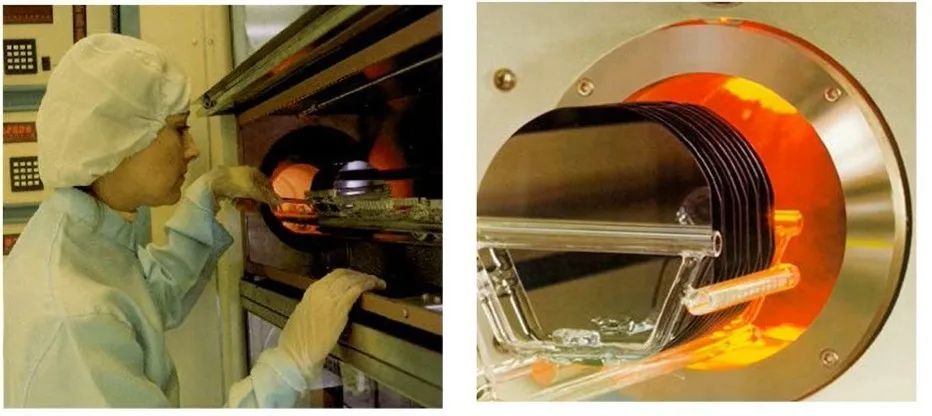

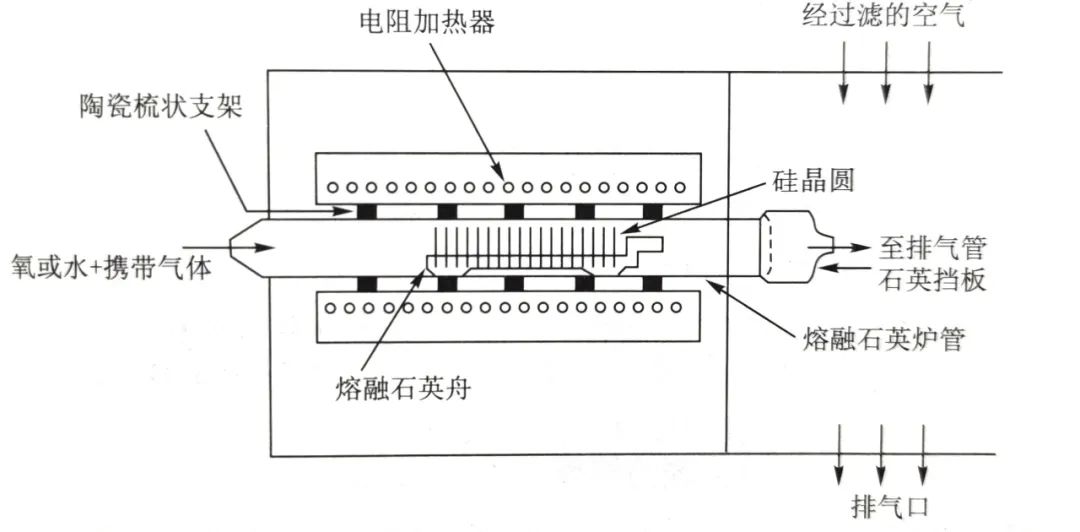

热氧化法装置:

图源:https://slideplayer.com/slide/2412042/

热氧化的基本装置如上图所示。反应器的组成包括:电阻加热氧化炉、圆筒形熔融石英管、开槽的石英舟(放在石英管中,用来垂直摆放晶圆)和注入口(用来注入高纯干燥氧气和高纯水蒸气)。炉管的装片端置于具有垂直流向的过滤空气的护罩中,持续注入过滤后的空气流。护罩用来减少周围空气中的灰尘和微粒数,使装片时可能受到的污染减至最小。

氧化温度一般保持在900~1200℃,典型的气体流速大约为1 L/min。

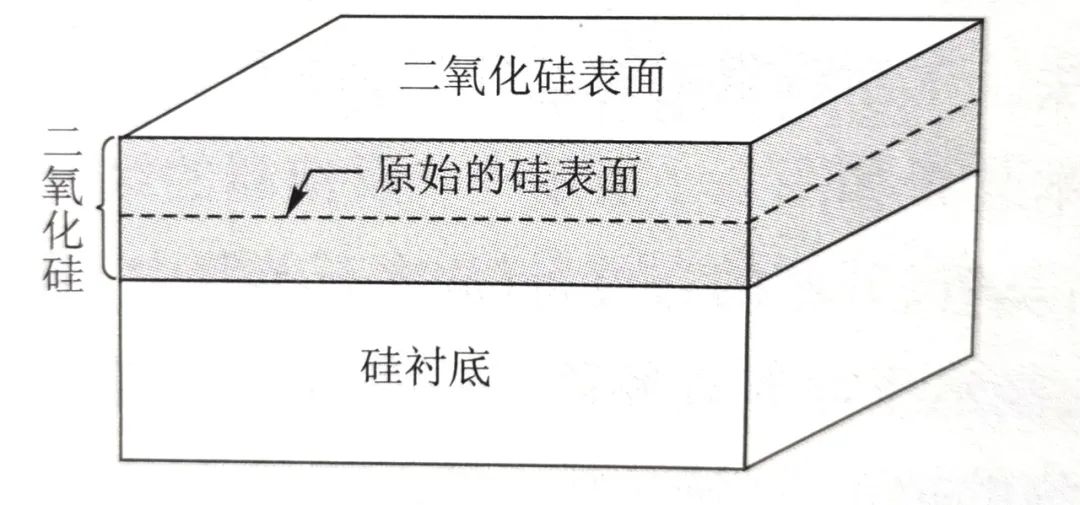

热氧化法生成的二氧化硅如下:

氧化物生长参数:

在氧化物生长的开始阶段,当表面反应是限制生长速率的主要因素时,氧化层厚度随时间呈线性变化。当氧化层变厚时,氧化剂必须通过氧化层扩散,在硅﹣二氧化硅界面与硅发生反应,反应受扩散过程限制。这时,氧化层厚度与氧化时间的平方根成正比,生长速率曲线为抛物线。

干氧氧化可以得到高质量的氧化膜,其致密性更好且具有更高的击穿电压,所以对于较薄的氧化层,例如 MOSFET栅氧化层(≤20nm),一般采用干氧氧化。

对于相对较厚的氧化层,例如MOS集成电路中的场氧化层(≥20nm)以及对于双极器件,则采用湿氧(或水蒸气)氧化,以获得适当的隔离和保护效果。在温度和时间相同的情况下,湿氧氧化的氧化层厚度是干氧氧化的5~10倍。

薄氧化层生长:

为了精确地控制薄氧化层厚度并使其具有可重复性,一般都采用较慢的生速率。获得慢生长速率的方法有很多,包括

常压低温下(800~900℃)进行干氧氧化

在低于标准大气压下氧化,利用惰性气体(如氮气、氦气和氩气)的注入降低氧气分压再进行氧化

采用复合氧化膜的方法,即栅氧化层由热氧化生成的二氧化硅层和化学气相淀积生成的二氧化硅层复合生成。

生长10~15 nm的栅氧化层的主要采用方法1。采用这种方法,利用现代立式氧化炉可以在晶圆上生成高质量、可重复的、厚度为10nm的氧化层,且整个晶圆氧化层厚度误差在0.1 nm以内。

对于ULSI(超大规模集成电路)来说,生长薄(5~20nm)而又均匀的高质量、可重复的栅氧化层显得越来越重要。薄氧化层的生长机理:在干氧氧化的初始阶段,氧化层中存在很大的压缩应力。这种应力降低了氧在氧化层中的扩散系数。当氧化层较厚时,由于受二氧化硅的黏滞流作用影响,压缩压力减小,扩散系数将接近无应力时的值。

氧化质量:

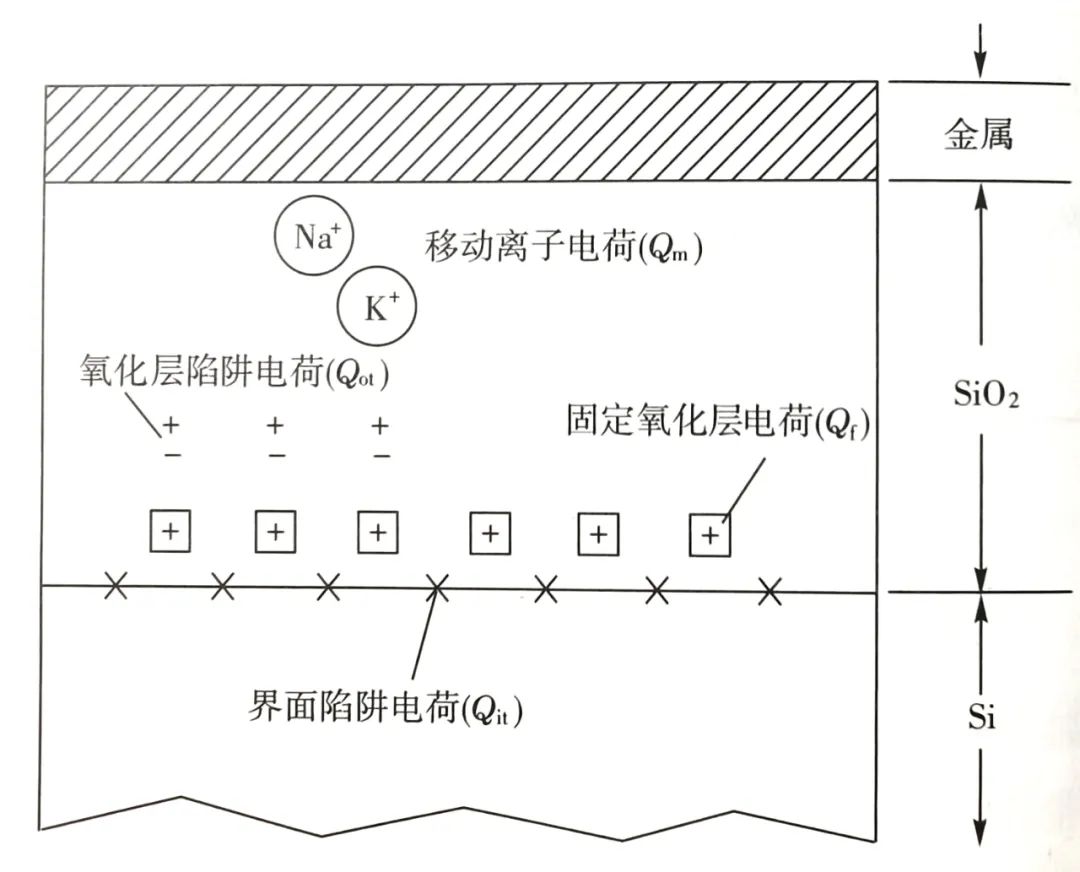

MOS器件也会受到氧化层中的电荷和位于二氧化硅-硅界面处的陷阱的影响,目前,大部分采用低温(450℃)氢退火进行钝化处理。

移动离子电荷是被钠或其他碱金属离子污染而产生的。碱金属离子污染会影响半导体器件在高偏置和高温条件下的工作的稳定性。钠污染可以通过在氧化过程中加入氯来降低。

其他:

1.判定氧化层厚度最简便的方法可能就是根据颜色表来比较晶圆的颜色。当用垂直方向的白光来照射表面被氧化的晶圆时,光会穿过氧化层,并被下层的硅反射。相长干涉会增加某一反射光的波长,从而使相应于这一波长的晶圆颜色发生变化。例如,氧化层厚度为500nm的晶圆会呈现蓝绿色。

2.判定氧化层厚度更精确的方法是表面光度法和椭圆偏光法。

3.斯坦福大学的SUPREM软件可以准确模拟多维氧化物的生长,还可以对沉积、扩散、外延层生长和离子注入工艺的结果进行预测。

© 滤波器 微信公众号