定义 2.5D 器件是缩小以适应封装的印刷电路板,还是超出单个芯片极限的芯片,看似是细枝末节的语义问题,但却会对设计的整体成功产生重大影响。

平面芯片一直受到光罩尺寸的限制,光罩尺寸约为 858 平方毫米。除此之外,产量问题也使得硅片并不经济。多年来,这限制了平面基板上可容纳的功能数量。任何额外的功能都需要设计成额外的芯片,并用印刷电路板(PCB)连接起来。

2.5D 封装技术的出现开辟了一个全新的扩展轴,允许多个芯片在先进的封装内相互连接。但是,这种封装设计的出发点会对各种元件的组装方式、参与人员、使用的工具和时间产生重大影响。

如今,2.5D 技术正在逐渐普及,这有几个原因。其一是成本。"西门子数字工业软件公司高级封装解决方案总监 Tony Mastroianni 说:"如果你能制造出更小的芯片或芯片组,而且这些芯片组经过设计和优化,可以集成到一个封装中,那么整个封装就会变得更小。"由于良品率更高,这对成本产生了巨大影响。芯片尺寸芯片的良品率不再是 50%或更低,而是可以达到 90%。

使用印刷电路板连接芯片也会限制性能。"Eliyan 公司首席执行官兼联合创始人 Ramin Farjadrad 说:"一直以来,我们都是将芯片单独封装,放在 PCB 上,然后通过一些布线进行连接。"人们开始面临两方面的问题。其一是这些芯片之间的带宽因穿过印刷电路板而受到限制,其二是封装上有限数量的球限制了这些芯片之间的连接。

与 PCB 相比,2.5D 的主要区别在于 2.5D 使用芯片尺寸。2.5D使用的是芯片尺寸,导线的纹理要细得多,而且与电路板相比,内插板或封装上的各种元件可以更紧密地排列在一起。由于这些原因,导线可以更短,数量可以更多,带宽也会增加。

这在多个层面上影响了性能。"西门子的 Mastroianni 说:"由于它们距离如此之近,因此不会有较长的传输 RC 或 LC 延迟,因此速度要快得多。西门子的 Mastroianni 说:"你不需要芯片上的大驱动器来驱动电路板上的长线路,因此功耗更低。你可以获得数量级更高的性能和更低的功耗。常见的衡量标准是每比特皮焦。移动比特所需的能量使得 2.5D 技术引人注目。

尽管如此,思维方式仍会影响最初的设计理念,并对整个流程产生影响。如果你与芯片设计师交谈,他们可能会说这只是一个大芯片,"Cadence 公司定制集成电路和 PCB 部门产品管理组总监 John Park 说,"但如果你与封装设计师或电路板设计师交谈,他们会说这基本上是一个大芯片。"但如果你与封装设计师或电路板设计师交谈,他们会说这基本上是一个很小的 PCB。

谁说得对?"Ansys 产品营销总监 Marc Swinnen 说:"公司内部的组织结构往往决定了如何处理这个问题。"从长远来看,你要确保公司的结构与物理学相匹配,而不是试图让物理学与你的公司相匹配"。

显而易见的是,没有什么是确定的。"Cadence 的 Park 说:"数字世界是非常有规律的,每两年我们就会有一个新的节点,它的尺寸只有原来的一半。"会有一些新的要求,但都是循序渐进的。今年我们可能会有 8 项新的封装技术,明年有 3 项,后年有 12 项。其中许多技术来自于代工厂,而过去只是来自于外包半导体组装和测试公司(OSAT)以及基板供应商。虽然代工厂是新进入者,但 OSAT 正在以较低的成本提供一些非常有趣的封装技术。

造成这种情况的部分原因是不同的群体有不同的需求。"安世公司的 Swinnen 说:"政府和军方认为异构集成能力是主要优势。"他们并不是在推动处理技术的发展。相反,他们设计的是单片微波集成电路(MMIC)等需要波导的高速信号。他们从封装组装的角度出发。相反,高性能计算(HPC)公司则从 5 纳米和 3 纳米芯片与高性能高带宽内存(HBM)的堆叠角度出发。他们认为这是一个硅组装问题。他们认为这样做的好处是架构灵活,他们可以加入内核和接口,为特定市场创造产品,而不必重新设计每个芯片。他们认为灵活性就是好处。军方认为异构集成是好处所在。

材料

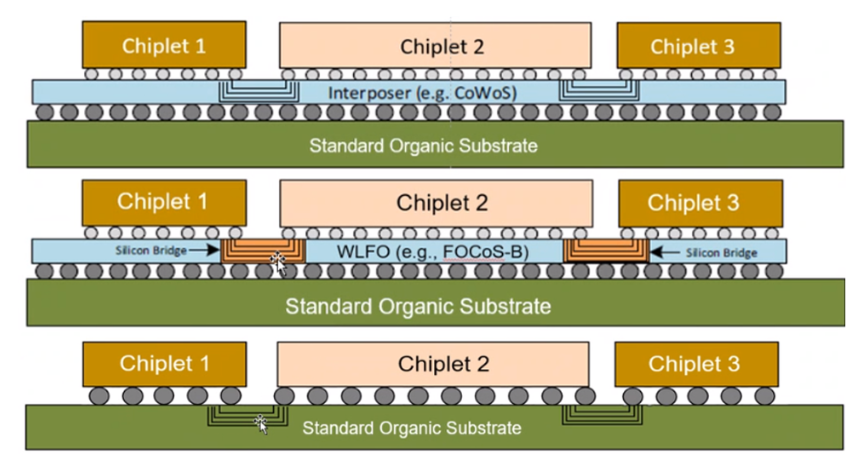

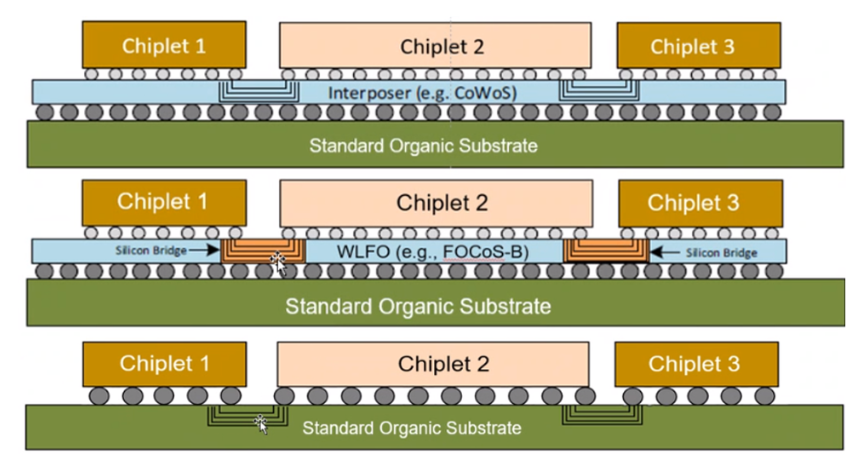

在 2.5D 封装技术中,有几种材料被用作基板,每种材料在成本、密度和带宽方面都有不同的权衡,同时每种材料都有一些必须克服的不同物理问题。如图 1 所示,凸点间距是主要的区别点之一。

图 1. 不同基底配置的芯片互连。资料来源:Eliyan

说到中间件,一般都认为是硅。"Eliyan公司的Farjadrad说:"中间件可以是一大块硅片(图1上部),或者只是芯片之间的硅桥(图1中部),以提供连接。"这两种解决方案都使用高密度的微凸块。插座和桥接器提供了大量高密度的凸块和迹线,从而带来了带宽。如果使用 1,000 根导线,每根导线以 5Gb 的速度运行,就能获得 5Tb 的带宽。如果有 10,000 条,则可获得 50Tb 带宽。但这些信号的传输距离不能超过两三毫米。另外,如果避免使用硅内插层,而采用有机封装(图 1 底部),如倒装芯片封装,则走线密度会降低 5 到 10 倍。然而,导线的厚度却可以增加 5 到 10 倍。这是一个很大的优势,因为导线的电阻会随着导线厚度的平方而降低。导线的横截面会随着导线的平方而增大,因此电阻会大大降低。如果密度降低 5 倍,就意味着可以将信号传输得更远 25 倍"。

对某些人来说,这就是每毫米的带宽。"Synopsys 解决方案部硬件工程高级经理 Kent Stahn 说:"如果你有一条并行总线或一个高速并行接口,而且你想要每毫米的带宽,那么你可能会选择硅插层。"有机基板损耗低、成本低,但密度不够高。在这两者之间,有许多解决方案可以实现其中的某些功能,但成本却不尽相同。

选择衬底材料还有其他原因。"Synopsys 解决方案部高级产品经理 Manuel Mota 说:"硅内插层来自代工厂,因此可用性是个问题。"一些公司在采购先进封装时面临挑战,因为产能已被占用。如果采用带宽密度稍低的其他技术,也许就能满足您的应用需求,您可以在其他地方找到这些技术。这正在成为一个关键方面。

然而,所有这些技术都在飞速发展。"Park说:"光罩的极限大约是858毫米见方。"人们谈论的内插板尺寸可能是这个尺寸的四倍,但我们的层压板尺寸要大得多。日本生产的一些层压基板的互连密度已接近硅材料的水平。我个人认为,有机基板将得到更多的推动。台积电(TSMC)的基板上芯片(CoWoS)使用硅衬底,12 年来一直是首选技术。最近,他们推出了 CoWoS-R,使用的是聚酰胺薄膜,更接近于有机基板类型。现在,我们听到了很多关于玻璃基板的说法。

随着时间的推移,封装内的总面积可能会增加。"Park 补充说:"对于代工厂来说,继续制造 30 英寸印刷电路板大小的产品是没有意义的。Park 补充说:"有些材料能够满足更大的设计要求。我们真正需要的是芯片到芯片的密度。我们希望芯片之间紧紧相连,互连长度只有几毫米。我们要的是非常短。但剩下的部分只是将 I/O 划成扇形,以便连接到 PCB 上。

这就是为什么桥接很流行的原因。"Synopsys 公司的 Stahn 说:"我们确实看到了接口高速部分向桥接发展的趋势。"它的背面是扇出,比如 RDL 扇出。我们看到 RDL 封装将更像传统封装。

内插器可提供更多功能。"如今,99% 的内插器都是无源的,"Park 说。"没有线路前端,没有设备层。它纯粹是生产线的后端处理。你要在硅上增加三、四、五个金属层。这就是我们所说的无源内插层。它只是建立芯片与芯片之间的互连。但也有人把芯片做成有源插层,基本上就是在芯片上添加逻辑"。

这可能出于不同的目的。"莫塔说:"你已经看到一些公司在做有源内插件,在其中添加电源管理或一些控制逻辑。莫塔说:"当你开始把有源电路放到内插板上时,它仍然是 2.5D 集成,还是变成 3D 集成?目前我们还没有看到有源内插板的大趋势。

不过也有一些新问题。"你必须考虑热膨胀系数(CTE)不匹配的问题,"Stahn 说。"当两种具有不同热膨胀系数的材料粘合在一起时,就会出现这种情况。让我们从硅内插板开始。你可以获得更高瓦数的系统,在这种系统中,系统级芯片可以与它们的同级芯片对话,这可能会消耗大量的电能。硅内插层仍需装入封装中。硅与封装材料之间存在 CTE 误差。有了桥接器,你可以在需要的地方使用它,但它仍然是硅芯片到芯片。你必须进行热机械分析,以确保所提供的功率和所存在的 CTE 不匹配能产生可行的系统。

虽然理论上信号长度可以变长,但这也带来了一些问题。"Mastroianni 说:"当你在芯片内部进行这些长连接时,通常会将这些线路限制在几毫米的范围内,然后进行缓冲。"无源硅插层的问题在于没有缓冲器。这确实会成为一个严重的问题。如果你确实需要进行这些连接,你需要非常仔细地进行规划。此外,还需要确保进行时序分析。通常情况下,你的软件包人员不会进行这种分析。这更像是一个已经由硅工程师通过静态时序分析解决的问题。我们确实需要引入 STA 流程,并处理所有包括有机和硅类型迹线的提取,这就成为了一个新问题。当你开始接触一些非常长的迹线时,普通 STA 时延计算器中假设的简单 RC 时延并没有考虑到这些迹线之间的一些电感和互感,因此对于这些长迹线,你可能会遇到严重的精度问题。

有源内插器可以提供帮助。"有了有源内插器,你就可以通过安装缓冲器或信号中继器来克服一些长距离问题,"Swinnen 说。"这样一来,它看起来又更像一个芯片了,而你只能在硅片上实现这一点。英特尔公司推出了 EMIB 技术,他们将 chiplet 嵌入中间件中,这是一个有源桥接器。芯片与 EMIB 芯片对话,它们都通过这个小的有源桥接芯片与你对话,它不完全是有源插层,但作用几乎与有源插层一样。

不过,即使是无源元件也能增加价值。"Mastroianni 说:"首先要做的就是在插接器中加入沟槽电容器。Mastroianni 说:"这样就能在最重要的地方,即靠近芯片的地方,实现良好的去耦。如果把它们放在电路板上,就会失去高速接口的很多优势。如果能把它们放在内插层中,置于快速切换速度信号的正下方,就能实现局部去耦。

除了不同的材料,还有谁来设计内插板的问题。"Ansys 公司产品管理高级经理 Matt Commens 说:"在由谁进行设计的问题上,业界似乎把它看成是一个小小的 PCB。"尽管内插板是硅工艺,但通常是由封装工程师设计的。高性能内插器尤其如此。这似乎与直觉相反,但他们有信号完整性背景,他们一直在设计传输线并尽量减少互连处的不匹配。而传统的集成电路设计师则是从元件的角度进行设计。因此,业界肯定会告诉我们,他们指派从事设计工作的人员都是封装类型的角色。

电源

印刷电路板和集成电路之间的布线有很大的不同。"Fraunhofer IIS/EAS 高效电子部门主管 Andy Heinig 说:"内插板的布线要容易得多,因为与 PCB 相比,元件的数量大大减少。"另一方面,由于金属层的电阻较高,而且电源网被信号线切断,因此插接板上的电源网要复杂得多。由于布线密度较高,芯片到芯片接口的布线也更为复杂"。

功率传输看起来非常不同。"Park 说:"如果你看印刷电路板,他们会在各层中嵌入这些大的金属浇注区,然后将需要穿过的区域作废。"你先铺上一层铜,然后再把其他地方空出来。我们不能用这种方法制造内插层。我们必须沉积互联,因此硅内插板上的电源和接地结构看起来更像数字芯片。但信号看起来更像 PCB 或层压封装。

路由看起来确实更像印刷电路板,而不是芯片。"Park 补充说:"你会看到像水滴或圆角这样的东西,它与焊盘或通孔连接,以创造更好的产量。Park 补充说:"现在的布线方式更像 PCB,而不是数字集成电路,后者只有 90° 正交角和干净的布线通道。无论是硅还是有机内插件,通孔通常都比导线大,这是典型的 PCB 问题。如果我们谈论的是数字电路,那么路由器又更像是小型印刷电路板,而不是芯片。

TSV 也会带来问题。"Swinnen 说:"如果将它们视为正方形,就会在边角处损失大量空间。"你真的希望这些物体周围呈 45° 角。硅路由器传统上是曼哈顿式的,但 RDL 路由器的传统由来已久,它是连接凸点的顶层。这种路由器传统上使用八角形凸点或圆形凸点,然后进行 45° 路由。它不像 PCB 路由那样灵活,但他们有再分布层路由器,也有一些来自全定制方面的路由器,具有全河路由功能。

本文译自:https://semiengineering.com/2-5d-integration-big-chip-or-small-pcb/