ISSCC2024,中国内地论文已经涵盖全部12个技术领域,并且收录文章数量持续上涨,进一步表明中国大陆的科研实力。

正如中国科学院院士刘明在ISSCC2024中国区发布会的致辞中表示,首先祝贺中国内地加上港澳在ISSCC再次取得好成绩;第二是有更多的高校在ISSCC上发表论文,表明我国的固态电路的队伍越来越壮大;第三是随着海外优青的加入,让我国固态电路人员规模越来越大,实力更强;第四是要把现在一些面的工作形成点,一些点的工作要逐渐形成面,然后形成体系;第五最好能有一些原创性工作,成为这个行业的引领,最终对产业形成影响。

下面我们一起走进ISSCC2024,盘点一下中国内地高校论文情况。

1、北京大学入选5篇

全部来自集成电路学院

集成电路学院黄如院士-叶乐教授团队

针对物联网传感器芯片应用不断提升的高能效模拟前端放大器需求,设计并实现了一款超高能效、超低功耗的电容耦合型斩波仪表放大器,突破了传统放大器中功耗与噪声之间折中关系的性能瓶颈,跨工艺验证得到其综合性能达到国际领先水准。针对以上瓶颈,团队提出了基于输入倍增技术的高能效放大器:该技术创新性地提出了输入信号倍增技术,将输入耦合到输入对管的栅极与源极从而提升其等效增益,在相同的功耗下实现了更低的噪声水平。与此同时,针对超低功耗应用中的漏电问题,采用漏电补偿技术解决了寄生阱二极管与开关衬底漏电导致的直流偏置偏移问题。Paper3.10《A 069/0.58-PEF 16nW/24nW Capacitively Coupled Chopper Instrumentation Amplifier with an Input-Boosted First Stage in22nm/180nm CMOS》在180nm CMOS和22nm CMOS下分别研制出了一款高能效放大器。在180nm工艺下该结构以24nW的功耗实现了1.6kHz带宽内5uV的积分噪声;在22nm工艺下以1.6nW的功耗实现了230Hz带宽内8uV的积分噪声;在综合评估放大器能效的指标(Power efficiency factor, PEF)下,分别达到了0.58和0.69的指标,是目前能效最优的连续时间模拟前端放大器。该放大器在不同温度与电压下进行了验证,保证了其在复杂工作环境下的稳定性。该电路可广泛应用于面向传感应用的物联网芯片中,作为其中模拟信号链最前端的模块。北京大学集成电路学院博士生许欣航、叶思源为共同一作,通讯作者为沈林晓研究员和叶乐教授。

ISSCC2024,中国内地论文已经涵盖全部12个技术领域,并且收录文章数量持续上涨,进一步表明中国大陆的科研实力。

正如中国科学院院士刘明在ISSCC2024中国区发布会的致辞中表示,首先祝贺中国内地加上港澳在ISSCC再次取得好成绩;第二是有更多的高校在ISSCC上发表论文,表明我国的固态电路的队伍越来越壮大;第三是随着海外优青的加入,让我国固态电路人员规模越来越大,实力更强;第四是要把现在一些面的工作形成点,一些点的工作要逐渐形成面,然后形成体系;第五最好能有一些原创性工作,成为这个行业的引领,最终对产业形成影响。

下面我们一起走进ISSCC2024,盘点一下中国内地高校论文情况。

1、北京大学入选5篇

全部来自集成电路学院

集成电路学院黄如院士-叶乐教授团队

针对物联网传感器芯片应用不断提升的高能效模拟前端放大器需求,设计并实现了一款超高能效、超低功耗的电容耦合型斩波仪表放大器,突破了传统放大器中功耗与噪声之间折中关系的性能瓶颈,跨工艺验证得到其综合性能达到国际领先水准。针对以上瓶颈,团队提出了基于输入倍增技术的高能效放大器:该技术创新性地提出了输入信号倍增技术,将输入耦合到输入对管的栅极与源极从而提升其等效增益,在相同的功耗下实现了更低的噪声水平。与此同时,针对超低功耗应用中的漏电问题,采用漏电补偿技术解决了寄生阱二极管与开关衬底漏电导致的直流偏置偏移问题。Paper3.10《A 069/0.58-PEF 16nW/24nW Capacitively Coupled Chopper Instrumentation Amplifier with an Input-Boosted First Stage in22nm/180nm CMOS》在180nm CMOS和22nm CMOS下分别研制出了一款高能效放大器。在180nm工艺下该结构以24nW的功耗实现了1.6kHz带宽内5uV的积分噪声;在22nm工艺下以1.6nW的功耗实现了230Hz带宽内8uV的积分噪声;在综合评估放大器能效的指标(Power efficiency factor, PEF)下,分别达到了0.58和0.69的指标,是目前能效最优的连续时间模拟前端放大器。该放大器在不同温度与电压下进行了验证,保证了其在复杂工作环境下的稳定性。该电路可广泛应用于面向传感应用的物联网芯片中,作为其中模拟信号链最前端的模块。北京大学集成电路学院博士生许欣航、叶思源为共同一作,通讯作者为沈林晓研究员和叶乐教授。

针对宽带通信系统应用,不断提升的高速高精度模数转换器的要求,提出并实现了一款高速,高精度,高能效的流水线-逐次逼近型模数转换器,突破了传统流水线-逐次逼近型模数转换器的架构中转换级和级间放大器两大速度和能效的瓶颈。针对以上瓶颈,团队针对转换级和级间放大器两个方面提出解决方案。转换级方面,提出了基于连续时间逐次逼近型模数转换器的采样转换并行技术,创新性地将模数转化器的采样过程与高位量化过程并行起来,从而在保持高能效的同时显著缩短转换级的采样转换时间,提升了整体的速率;级间放大器方面,首次提出了基于先开环后闭环的相关电平抬升技术,利用开环放大显著提升余量放大的速率,同时采用了自检测切断环路用于实现工艺电压温度鲁棒的高增益。此外,还提出了混合静态-动态环形放大器的电路架构,显著提高了级间放大器的噪声和能效性能。在提高采样转换速率的同时,实现了高速高精度模数转换器的能量效率世界纪录,相较现有工作将能效提升将近一倍。Paper9.1(亮点论文)《A 2mW 70.7dB SNDR 200MS/s Pipelined-SAR ADC with Continuous-Time SAR-Assisted Detect-and-Skip and Open-then-Close Correlated Level Shifting》研制了一款基于22nm CMOS工艺的高速高精度高能效的模数转换器芯片。在22nm工艺下,该芯片在200MS/s的采样率下实现了70.7dB SNDR的精度和2.0mW的功耗,在所有相同或更高采样率的模数转换器中达到了能量效率的世界纪录(177.7dB FoMs),能效提升了将近一倍。该电路具有高速,高精度,高能效等特点,可广泛应用于宽带通信和射频前端,高保真音视频信号接口处理,工业控制测量等应用中。一作是博士生叶思源,通讯作者是沈林晓研究员和叶乐教授。

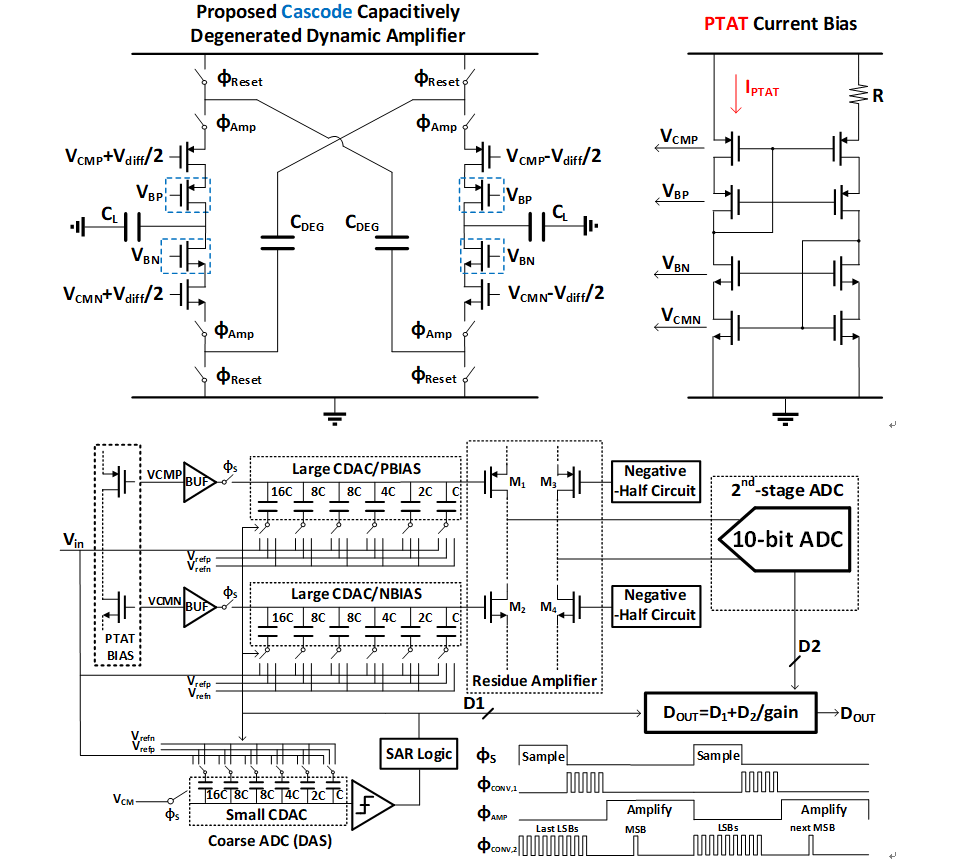

该工作面向通信、医学成像等需求,针对不断提升的高能效模数转换器的需求,提出了一个高性能,低功耗的动态放大器,解决了传统动态放大器线性度差、增益低、输出摆幅小等问题,并将其应用于模数转换器中,实现了极高能效的流水线-逐次逼近型模数转换器芯片。针对以上问题,团队首次提出了共源共栅的容性源极负反馈的动态放大器和最高位提前转换技术:其中共源共栅的容性源极负反馈的动态放大器改良了之前的技术,具有高线性度和高增益的特点,同时采用了温度补偿的电流偏置方案提升了PVT涨落下的性能鲁棒性。而另一方面,最高位提前转换技术在余量放大的过程中进行了第二级最高位的转换,这不仅进一步提高了动态放大器的输出摆幅,同时让第二级的最高位切换更快稳定。值得一提的是,这个技术获得的这些好处并不需要引入额外的硬件开销。利用以上技术,本工作提出了一个高能效、高增益、高线性度、高输出摆幅且PVT鲁棒的动态放大器,并实现了一个高能效的流水线-逐次逼近型模数转换器芯片。Paper9.4《A 182.3dB FoMs 50MS/s Pipelined-SAR ADC using Cascode Capacitively Degenerated Dynamic Amplifier and MSB Pre-Conversion Technique》研制了一款基于22nmCMOS工艺的高能效流水线-逐次逼近型模数转换器,该电路在奈奎斯特输入下达到了73.9dB的SNDR,仅消耗0.36mW。这达到了目前在相同或更高采样率的模数转换器中能效的世界纪录(FoMs=182.3dB)。第一作者是本科生陈卓毅,通讯作者是沈林晓研究员和叶乐教授。

面向边缘AI的应用场景,均使用稀疏脉冲作为信息介质的动态视觉传感器和脉冲神经网络推理引擎提供了可靠的高能效解决方案。课题组为了在有限的存储资源和功耗下,芯片能够集成更多的突触连接数量以提升芯片的推理能力,针对传统脉冲神经网络芯片中存在的突触权重,膜电位等数据类型在多时间步上数据搬运的问题,创新性地融合了时间步优先的数据流和存算一体阵列技术,使得权重在整个时间窗口内缓存于存算一体的子阵列中,最小化数据的片内外搬运次数。团队提出了时间步数据流和SRAM存算一体融合架构,利用存算一体阵列以避免突触权重在多时间步上的数据搬运;提出了无时钟自适应稀疏性存算一体电路技术,依据脉冲神经网络输入稀疏性,存算一体阵列实现动态调整计算延迟和计算功耗,并且无需任何全局时钟,通过异步握手信号控制以适应事件触发特性;此外,还使用了高细粒度的脉冲触发和时钟门控电路设计方法,最小化降低时钟树带来的“暗硅”消耗。Paper30.2《A 22nm 0.26nW/Synapse Spike-Driven Spiking Neural Network Processing Unit Using Time-Step-First Dataflow and Sparsity-Adaptive In-Memory Computing》研制了基于存算一体的领域专用脉冲神经网络芯片,在22nm工艺下,该芯片可实现每突触结构消耗0.26nW的功耗密度,以及18 Synapse/bit的存储密度,相比国际最好水平分别优化6倍和2.3倍。该芯片具备高能效,高网络密度,低功耗密度等优势,可应用于边缘端AI,如图像分类,目标识别等应用场景。第一作者是博士生刘影和马宇飞研究员,通讯作者为北京大学叶乐教授和王志轩。

集成电路学院王源教授-唐希源研究员团队 针对组合优化问题求解,不断提升的计算速度、系数精度、与求解质量需求,设计并实现了一款具有多值互联系数,嵌入退火功能的连续时间存内伊辛机芯片,突破了传统连续时间伊辛机的系数精度与求解质量瓶颈。团队提出了基于嵌入式动态随机存储器的存内伊辛机:该技术创新性地使用电流编程动态随机存储器来进行存内连续时间自旋节点更新。在相互作用系数写入时,编程电流产生自校准的权重电压,实现多值模拟相互作用系数的高精度编程。与此同时,针对连续时间伊辛机的求解质量问题,课题组采用负反馈来帮助系统跳出局部最优解,并利用动态随机存储器中的漏电来逐渐降低负反馈强度,模拟退火过程,从而达到更高的求解质量。Paper30.5《A Variation-Tolerant In-eDRAM Continuous-Time Ising Machine Featuring 15-Level Coefficients and Leaked Negative-Feedback Annealing》研制了基于动态随机存储器的连续时间存内伊辛机芯片。在65nm工艺下,该芯片可实现15值的相互作用系数,小于20.7ns的最快求解速度,0.33nJ的求解能量,以及848um2/Spin的面积效率,并在工艺、电压、温度偏移下均有高稳定性。该芯片具备高求解速度、高系数精度、和高求解质量等优势,在现实生活中时间关键的组合优化问题求解中极具应用前景。博士后宋嘉豪和博士生吴子涵共同一作,通讯作者为唐希源研究员和王源教授。

2、北京理工大学 实现ISSCC零的突破 集成电路与电子学院孙厚军教授-朱伟副教授团队 Paper32.8《A 27.8-to-38.7GHz Load-Modulated Balanced Power Amplifier with Scalable 7-to-1 Load-Modulated Power-Combine Network Achieving 27.2dBm Output Power and 28.8%/23.2%/16.3%/11.9% Peak/6/9/12dB Back-Off Efficiency》针对面向5G毫米波频段应用的功率放大器不断上升的输出功率和调制效率需求,从架构和电路两个层面提出解决方案,设计了国际上第一款可应用于5G毫米波通信的多路负载调制功率放大器,该放大器解决了5G毫米波通信中功率放大器在高阶调制下效率低的问题,可增加5G毫米波通信的可部署性。架构层面,在引入多级正交混合网络来增加辅路功放数量的基础上,团队创新性地提出将主路功放的位置挪移至多级正交混合网络前直接连接,形成功放嵌入型宽带正交混合网络,显著改善了架构的简洁性、电路性能和设计优化效率。基于上述架构和电路层面的创新,研制了一款基于65nm CMOS工艺的7路负载调制平衡功率放大器芯片。测试结果表明,放大器的小信号增益可达18.4dB,在27.2-to-45GHz频带内都实现了较好的端口匹配。该放大器在26-40GHz的频率范围内都达到了大于25.4dBm的饱和功率和大于22%的峰值效率,并展示出卓越的功率回退效率提升和AM-PM线性度。在38GHz频点,放大器实现了17.1dB增益, 在峰值/6/9/12dB回退点效率分别为28.8%/23.2%/16.3%/11.9%。在当前国际上公开报道的工作在30GHz及以上的功率放大器中,该电路实现了最高的峰值效率和功率回退效率。芯片的调制测试结果则证明了该电路可广泛应用于宽带高速无线通信链路中。

3、电子科技大学入选4篇

信息与通信工程学院2篇,电子科学与工程学院2篇

信息与通信工程学院周军教授团队入选2篇

Paper14.8《NASP:A 96.8% 10-Keyword Accuracy and 1.68uJ/Classification Keyword Spotting and Speaker Verification Processor Using Adaptive Beamforming and Progressive Wake-Up》设计并实现了一款超低功耗自适应抑噪的离线语音控制AI芯片,结合算法、架构和电路协同优化,提出了多任务动态重构AI处理架构、多阶段自适应事件驱动处理电路、基于波束成形的自适应噪声抑制电路、关键词/声纹识别融合电路等多项技术,实现了微瓦级高准确率离线语音控制,平均每次识别能耗仅为约2微焦,安静场景识别准确率在95%以上,人声干扰下也可达90%以上,达到了国际同类设计最低能耗和最高准确率,并可同时支持关键词和声纹识别。该芯片适用于智能家居、智能座舱、智能玩具等低功耗离线语音控制应用。第一作者是博士生肖剑彪。

Paper33.1(亮点论文)《A High-Accuracy and Energy-Efficient Zero-Shot-Retraining Seizure-Detection Processor withHybrid-Feature-Driven Adaptive Processing and Learning-Based Adaptive Channel Selection》设计并实现了一款超低功耗脑电识别AI芯片,提出了融合机器学习和深度学习的自适应AI处理架构、小样本片上在线学习电路和基于在线学习的自适应脑电通道筛选电路等多项技术,降低了对用户样本的需求,同时实现了极低处理能耗。在癫痫检测任务中,该芯片在不需要采集病人癫痫信号的前提下,准确率达到98%以上,同时平均每次识别能耗仅为约0.07微焦,达到了国际同类设计最低能耗,相比发表在ISSCC 2023的最新工作,准确率提升了近10%,能耗降低了90%以上。该芯片支持神经网络编程和多通道脑电处理,也可用于脑机接口、睡眠监测等其他智能脑电应用。第一作者是博士生刘嘉豪。

电子科学与工程学院王成教授和张波教授团队

Paper24.2(亮点论文)《A Scalable 134-to-141GHz 16-Element CMOS 2D λ/2-Spaced Phased Array》介绍了一种二维可拓展的半波长布局的D波段太赫兹相控阵芯片。创新提出了行波 LO/IF 分配网络实现相控阵的2D扩展;采用亚采样三倍器和中频波束形成来提高效率;通过具有三重谐振的片上天线缩减面积占用,实现半波长布局。并实现了16阵元和64阵元两种相控阵原型,该相控阵已在室内10米距离实现了14Gbit/s的数据传输,波束扫描角度可达±60°,扫描精度为10位。该通信实验得到了通信抗干扰全国重点实验室陈智教授和刘轲博士等研究人员的支持。

电子科学与工程学院无线技术与集成系统团队

Paper5.4《A 22.4-to-30.7GHz Phased-Array Receiver with Beam-Pattern Null-Steering and Beam-Tracking Techniques Achieving >30.2dB OTA-Tested Spatial Rejection》提出了一种波束零点调谐技术应用于5G毫米波相控阵接收机前端的设计,在相控阵接收机前端芯片上引入干扰消除电路实现了在射频链路的带内高功率空间干扰信号的消除功能,从而保护混频器以及后级电路免于功率过饱和。同时,芯片上还集成了配套的波束追踪模块,可以同时识别干扰信号和有用信号的来波方向。这两项技术摆脱了传统相控阵接收机对高功耗毫米波幅度控制电路或者高插损衰减器的需求,降低了射频通道的复杂度和功耗。此外,这项技术拥有良好的可扩展性,只需要在通道间添加适量的干扰消除电路即可应对多个不同入射方向的干扰信号。测试结果表明芯片能够支持n257、n258和n261多个5G毫米波频段。传输数据率达到3.2Gb/s。在空口测试条件下,应用该技术在目标方位实现了30.2~39.0dB的干扰抑制比。

3、电子科技大学入选4篇

信息与通信工程学院2篇,电子科学与工程学院2篇

信息与通信工程学院周军教授团队入选2篇

Paper14.8《NASP:A 96.8% 10-Keyword Accuracy and 1.68uJ/Classification Keyword Spotting and Speaker Verification Processor Using Adaptive Beamforming and Progressive Wake-Up》设计并实现了一款超低功耗自适应抑噪的离线语音控制AI芯片,结合算法、架构和电路协同优化,提出了多任务动态重构AI处理架构、多阶段自适应事件驱动处理电路、基于波束成形的自适应噪声抑制电路、关键词/声纹识别融合电路等多项技术,实现了微瓦级高准确率离线语音控制,平均每次识别能耗仅为约2微焦,安静场景识别准确率在95%以上,人声干扰下也可达90%以上,达到了国际同类设计最低能耗和最高准确率,并可同时支持关键词和声纹识别。该芯片适用于智能家居、智能座舱、智能玩具等低功耗离线语音控制应用。第一作者是博士生肖剑彪。

Paper33.1(亮点论文)《A High-Accuracy and Energy-Efficient Zero-Shot-Retraining Seizure-Detection Processor withHybrid-Feature-Driven Adaptive Processing and Learning-Based Adaptive Channel Selection》设计并实现了一款超低功耗脑电识别AI芯片,提出了融合机器学习和深度学习的自适应AI处理架构、小样本片上在线学习电路和基于在线学习的自适应脑电通道筛选电路等多项技术,降低了对用户样本的需求,同时实现了极低处理能耗。在癫痫检测任务中,该芯片在不需要采集病人癫痫信号的前提下,准确率达到98%以上,同时平均每次识别能耗仅为约0.07微焦,达到了国际同类设计最低能耗,相比发表在ISSCC 2023的最新工作,准确率提升了近10%,能耗降低了90%以上。该芯片支持神经网络编程和多通道脑电处理,也可用于脑机接口、睡眠监测等其他智能脑电应用。第一作者是博士生刘嘉豪。

电子科学与工程学院王成教授和张波教授团队

Paper24.2(亮点论文)《A Scalable 134-to-141GHz 16-Element CMOS 2D λ/2-Spaced Phased Array》介绍了一种二维可拓展的半波长布局的D波段太赫兹相控阵芯片。创新提出了行波 LO/IF 分配网络实现相控阵的2D扩展;采用亚采样三倍器和中频波束形成来提高效率;通过具有三重谐振的片上天线缩减面积占用,实现半波长布局。并实现了16阵元和64阵元两种相控阵原型,该相控阵已在室内10米距离实现了14Gbit/s的数据传输,波束扫描角度可达±60°,扫描精度为10位。该通信实验得到了通信抗干扰全国重点实验室陈智教授和刘轲博士等研究人员的支持。

电子科学与工程学院无线技术与集成系统团队

Paper5.4《A 22.4-to-30.7GHz Phased-Array Receiver with Beam-Pattern Null-Steering and Beam-Tracking Techniques Achieving >30.2dB OTA-Tested Spatial Rejection》提出了一种波束零点调谐技术应用于5G毫米波相控阵接收机前端的设计,在相控阵接收机前端芯片上引入干扰消除电路实现了在射频链路的带内高功率空间干扰信号的消除功能,从而保护混频器以及后级电路免于功率过饱和。同时,芯片上还集成了配套的波束追踪模块,可以同时识别干扰信号和有用信号的来波方向。这两项技术摆脱了传统相控阵接收机对高功耗毫米波幅度控制电路或者高插损衰减器的需求,降低了射频通道的复杂度和功耗。此外,这项技术拥有良好的可扩展性,只需要在通道间添加适量的干扰消除电路即可应对多个不同入射方向的干扰信号。测试结果表明芯片能够支持n257、n258和n261多个5G毫米波频段。传输数据率达到3.2Gb/s。在空口测试条件下,应用该技术在目标方位实现了30.2~39.0dB的干扰抑制比。

芯片照片

芯片照片

系统Demo板

4、东南大学入选6篇

集成电路学院2篇,电子信息科学与工程学院4篇

集成电路学院单伟伟教授团队

Paper14.2《Proactive Voltage Droop Mitigation Using Dual-Proportional-Derivative Control Based on Current and Voltage Prediction Applied to a Multicore Processor in 28nm CMOS》提出了一种基于电压、电流双预测的主动式片上电压陡降缓解方法,该方法具有基于机器学习的电流预测、基于芯片供电网络的电压预测和基于双PD控制的电压陡降控制策略,当应用于Risc-V 8核处理器时,在电压降发生时刻即开启调节,具有0延迟和仅0.6%的性能损失。

集成电路学院司鑫副教授团队

Paper34.3《A 22nm 64kb Lightning-like Hybrid Computing-in-Memory Macro with Compressed Adder tree and Analog-storage Quantizers for Transformer and CNNs》提出了一个混合的模拟-数字SRAM CIM宏,在模拟和数字域之间进行了新的计算划分。它报告了在22纳米CMOS中INT8操作的最高能效(60.8TOPS/W),且不损失精度。

电子信息科学与工程学院尤肖虎院士-张川教授团队

Paper2.7《BayesBB: A 9.6Gb/s 1.61ms Configurable All-Message-Passing Baseband-Accelerator for B5G/6G Cell-Free Massive-MIMO in 40nm CMOS》提出了一款19mm2可配置的全消息传递基带加速器,用于40nm的beyond-5G/6G无小区大规模MIMO。SoC实现了9.6Gbps的吞吐量、1.61ms的延迟,并集成了10 Gbps SERDES链路,在128×128 MIMO阵列测试时,支持>100bps/Hz的频谱效率。

电子信息科学与工程学院尤肖虎院士-李连鸣教授-王东明教授团队

Paper10.7《An 11GHz 2nd-order DPD FMCW Chirp Generator with 0.051% rms Frequency Error under a 2.3GHz Chirp Bandwidth, 2.3GHz/μs Slope, and 50ns Idle Time in 65nm CMOS》提出了一种基于模拟PLL的65nm FMCW调制器。调制器使用二阶DPD来补偿VCO非线性。在9.6-12.4GHz的输出频率下,在2.3GHz的线性调频带宽上,它实现了2.3GHz/μs的线性调频斜率,均方根频率误差为0.051%。

电子信息科学与工程学院胡三明教授团队

Paper19.2《A 12.4% Efficiency, 11dBm Psat, Odd-Harmonics-Recycling, 62-to-92GHz CMOS Frequency Quadrupler Using an Amplitude-Phase Coordinating Technique》提出一种40nm CMOS工艺中的奇次谐波回收(OHR)倍频器。62-92GHz四倍频器的功率效率为12.4%,3dB功率带宽为39%,饱和输出功率为11dBm。

电子信息科学与工程学院洪伟教授团队

Paper24.1《A 90-to-180GHz APD-Integrated Transmitter Achieving 18dBm Psat in 28nm CMOS》提出了一种90-180GHz的发射机,结合模拟预失真,并实现了18dBm的饱和输出功率。

5、复旦大学入选3篇

全部来自微电子学院

微电子学院徐鸿涛教授-殷韵教授团队

由于6GHz频段以下频谱资源非常紧张,为了减少对不同频段不同设备的干扰,射频发射机必须满足带外抑制度要求,其中强驱动本振信号的三阶谐波是造成带外干扰的主要因素之一。传统的解决方案通常采用片外滤波器,系统集成度较差,增加BOM成本且带来额外的插损。针对以上问题,Paper4.4《A Highly-Integrated 6-Phase Cell-Reused Digital Transmitter Using 1/3 Duty-Cycle LO Signals for Harmonic Rejection》提出了一种1/3占空比本振信号的全数字发射机,利用1/3占空比方波的三阶谐波为0的特点,大幅提升三阶谐波抑制能力;同时,采用6相基础矢量并结合单元复用技术,实现更高的输出功率和更大的复平面覆盖范围;此外,通过Doherty负载调制及关态电阻优化技术,进一步提高系统效率和线性度。采用28nm CMOS工艺,该芯片在0.7-2.5GHz频段内实现了大于45dBc的三阶谐波抑制,是同类数字化发射机工作的首创,同时输出功率、效率和核心面积均达到国际领先水平。殷韵教授是本文通讯作者,WiCAS(无线集成电路与系统)课题组博士生李嘉祥、李梓木为共同第一作者。

微电子学院闫娜教授团队

系统Demo板

4、东南大学入选6篇

集成电路学院2篇,电子信息科学与工程学院4篇

集成电路学院单伟伟教授团队

Paper14.2《Proactive Voltage Droop Mitigation Using Dual-Proportional-Derivative Control Based on Current and Voltage Prediction Applied to a Multicore Processor in 28nm CMOS》提出了一种基于电压、电流双预测的主动式片上电压陡降缓解方法,该方法具有基于机器学习的电流预测、基于芯片供电网络的电压预测和基于双PD控制的电压陡降控制策略,当应用于Risc-V 8核处理器时,在电压降发生时刻即开启调节,具有0延迟和仅0.6%的性能损失。

集成电路学院司鑫副教授团队

Paper34.3《A 22nm 64kb Lightning-like Hybrid Computing-in-Memory Macro with Compressed Adder tree and Analog-storage Quantizers for Transformer and CNNs》提出了一个混合的模拟-数字SRAM CIM宏,在模拟和数字域之间进行了新的计算划分。它报告了在22纳米CMOS中INT8操作的最高能效(60.8TOPS/W),且不损失精度。

电子信息科学与工程学院尤肖虎院士-张川教授团队

Paper2.7《BayesBB: A 9.6Gb/s 1.61ms Configurable All-Message-Passing Baseband-Accelerator for B5G/6G Cell-Free Massive-MIMO in 40nm CMOS》提出了一款19mm2可配置的全消息传递基带加速器,用于40nm的beyond-5G/6G无小区大规模MIMO。SoC实现了9.6Gbps的吞吐量、1.61ms的延迟,并集成了10 Gbps SERDES链路,在128×128 MIMO阵列测试时,支持>100bps/Hz的频谱效率。

电子信息科学与工程学院尤肖虎院士-李连鸣教授-王东明教授团队

Paper10.7《An 11GHz 2nd-order DPD FMCW Chirp Generator with 0.051% rms Frequency Error under a 2.3GHz Chirp Bandwidth, 2.3GHz/μs Slope, and 50ns Idle Time in 65nm CMOS》提出了一种基于模拟PLL的65nm FMCW调制器。调制器使用二阶DPD来补偿VCO非线性。在9.6-12.4GHz的输出频率下,在2.3GHz的线性调频带宽上,它实现了2.3GHz/μs的线性调频斜率,均方根频率误差为0.051%。

电子信息科学与工程学院胡三明教授团队

Paper19.2《A 12.4% Efficiency, 11dBm Psat, Odd-Harmonics-Recycling, 62-to-92GHz CMOS Frequency Quadrupler Using an Amplitude-Phase Coordinating Technique》提出一种40nm CMOS工艺中的奇次谐波回收(OHR)倍频器。62-92GHz四倍频器的功率效率为12.4%,3dB功率带宽为39%,饱和输出功率为11dBm。

电子信息科学与工程学院洪伟教授团队

Paper24.1《A 90-to-180GHz APD-Integrated Transmitter Achieving 18dBm Psat in 28nm CMOS》提出了一种90-180GHz的发射机,结合模拟预失真,并实现了18dBm的饱和输出功率。

5、复旦大学入选3篇

全部来自微电子学院

微电子学院徐鸿涛教授-殷韵教授团队

由于6GHz频段以下频谱资源非常紧张,为了减少对不同频段不同设备的干扰,射频发射机必须满足带外抑制度要求,其中强驱动本振信号的三阶谐波是造成带外干扰的主要因素之一。传统的解决方案通常采用片外滤波器,系统集成度较差,增加BOM成本且带来额外的插损。针对以上问题,Paper4.4《A Highly-Integrated 6-Phase Cell-Reused Digital Transmitter Using 1/3 Duty-Cycle LO Signals for Harmonic Rejection》提出了一种1/3占空比本振信号的全数字发射机,利用1/3占空比方波的三阶谐波为0的特点,大幅提升三阶谐波抑制能力;同时,采用6相基础矢量并结合单元复用技术,实现更高的输出功率和更大的复平面覆盖范围;此外,通过Doherty负载调制及关态电阻优化技术,进一步提高系统效率和线性度。采用28nm CMOS工艺,该芯片在0.7-2.5GHz频段内实现了大于45dBc的三阶谐波抑制,是同类数字化发射机工作的首创,同时输出功率、效率和核心面积均达到国际领先水平。殷韵教授是本文通讯作者,WiCAS(无线集成电路与系统)课题组博士生李嘉祥、李梓木为共同第一作者。

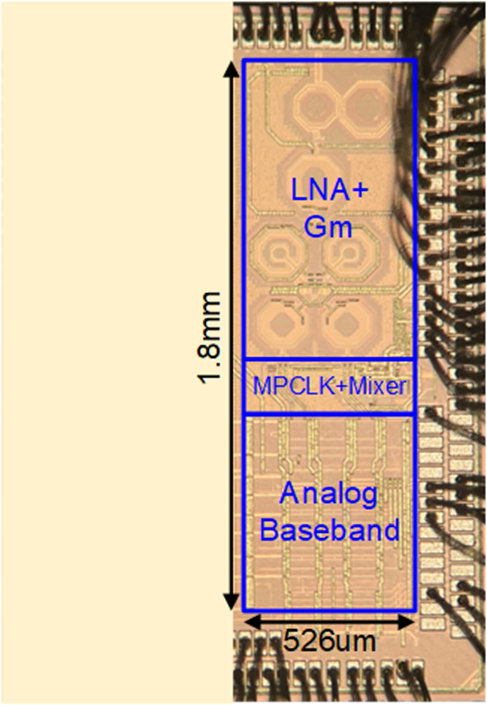

微电子学院闫娜教授团队随着5G、卫星通信、雷达等技术的飞速发展,一个终端装备往往需要支持多种工作模式和多个频带的工作范围,传统方案多采用多个窄带射频收发芯片集成实现,但以系统复杂度、成本和尺寸为代价。超宽带可重构射频芯片是多功能一体化终端的核心器件,具有灵活可配置、低成本、小尺寸等优势,在新一代通信、雷达等多功能应用中具有广泛的应用前景。针对多功能一体化终端需求面临的多制式、高集成度、可重构等问题,如何突破硅基超宽带射频电路在带宽、线性度、功率、噪声等方面的性能折中,寻求新的架构和新的方法,在同一射频前端实现中心频率、带宽、增益的可重构,同时满足系统所需的噪声和线性度要求,满足一体化射频的“尺寸、性能和灵活性”的需求,具有十分重要的现实意义,对其进行深入的研究和探索具有非常深远的理论研究意义和实用价值。由闫娜教授负责的RFiCAE课题组在该方向取得了突破性进展,Paper5.1《A 5-to-16GHz Reconfigurable Quadrature Receiver with 50% Duty-Cycle LO and IQ-Leakage Suppression》提出了一种能够适用于多种通信模式以及多种传输带宽的超宽带可重构接收机电路。该接收机能够覆盖5-16GHz的宽频带范围,能够适用于5G、卫星通讯和雷达等多种通信协议。同时在宽频带范围内,该接收机能够保持较低噪声系数和较低功耗。和国内外最新研究成果相比,该接收机在76-110mW功耗下,实现了5-16GHz频带覆盖范围、100-500MHz的连续可调基带带宽、40dB的增益可调范围以及2.2-5.7dB的噪声系数;同时在输入64QAM调制信号下能够得到最好-33dB的EVM性能,为宽带多功能射频一体化系统提供了一种高性能高能效的解决方案。论文第一作者为许灏青年研究员,闫娜教授为通讯作者。

芯片显微图

微电子学院徐佳伟教授团队

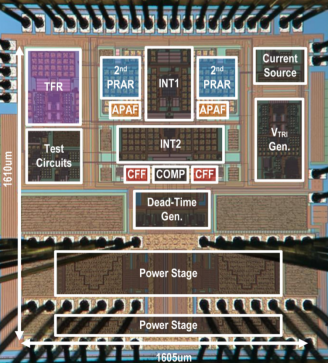

随着物联网时代的到来,人们的日常生活与智能化、小型化电子产品交织得越来越紧密。针对便携式/可穿戴设备应用的音频放大器也成为了学术界和工业界关注的研究热点。为了在电池供电的音频系统中实现超长使用/待机时间,同时减小对大容量电池的需求,实现设备小型化/轻量化,相关放大器要具有低静态功耗与高输出效率。此外为了保证高质量用户体验,放大器还要能够实现低噪声与高线性度的声学输出。设计能同时满足上述需求的音频放大器是当前存在的挑战。为了解决上述问题,复旦大学集成电路设计实验室(ICD Lab)的Paper21.2(亮点论文)《A 0.81mA, -105.2dB THD+N Class-D Audio Amplifier with Capacitive Feedforward and PWM-Aliasing Reduction for Wide-Band-Effective Linearity Improvement》提出了多种可满足低功耗设计需求的宽带线性度提升技术,可以在降低放大器电流消耗的情况下实现高线性度声学输出,适合于有小型化/轻量化需求的应用环境。该放大器在0.81mA的静态电流消耗性下,可以实现最优-105.2dB的非线性失真与噪声水平(THD+N),同时在20Hz-20kHz的全音频带宽内实现了优于-100dB的THD+N,最大实现了1.76W的功率输出水平,达到94.4%的峰值输出效率。不同与传统的D类放大器,该放大器采用电容前馈脉冲宽带调制技术,有效降低了比较器延时耦合输入信号的失真问题,同时使用混叠失真抑制技术与内嵌抗混叠滤波器,解决了传统放大器固有的混叠失真问题。由于上述技术主要采用无源器件实现,该放大器可以实现低的静态功耗开销。该新型D类放大器为未来便携式/可穿戴音频设备提供了一种高精度低功耗的设计思路。第一作者为直博生周凯文,徐佳伟教授和洪志良教授作为指导老师。

芯片显微图

微电子学院徐佳伟教授团队

随着物联网时代的到来,人们的日常生活与智能化、小型化电子产品交织得越来越紧密。针对便携式/可穿戴设备应用的音频放大器也成为了学术界和工业界关注的研究热点。为了在电池供电的音频系统中实现超长使用/待机时间,同时减小对大容量电池的需求,实现设备小型化/轻量化,相关放大器要具有低静态功耗与高输出效率。此外为了保证高质量用户体验,放大器还要能够实现低噪声与高线性度的声学输出。设计能同时满足上述需求的音频放大器是当前存在的挑战。为了解决上述问题,复旦大学集成电路设计实验室(ICD Lab)的Paper21.2(亮点论文)《A 0.81mA, -105.2dB THD+N Class-D Audio Amplifier with Capacitive Feedforward and PWM-Aliasing Reduction for Wide-Band-Effective Linearity Improvement》提出了多种可满足低功耗设计需求的宽带线性度提升技术,可以在降低放大器电流消耗的情况下实现高线性度声学输出,适合于有小型化/轻量化需求的应用环境。该放大器在0.81mA的静态电流消耗性下,可以实现最优-105.2dB的非线性失真与噪声水平(THD+N),同时在20Hz-20kHz的全音频带宽内实现了优于-100dB的THD+N,最大实现了1.76W的功率输出水平,达到94.4%的峰值输出效率。不同与传统的D类放大器,该放大器采用电容前馈脉冲宽带调制技术,有效降低了比较器延时耦合输入信号的失真问题,同时使用混叠失真抑制技术与内嵌抗混叠滤波器,解决了传统放大器固有的混叠失真问题。由于上述技术主要采用无源器件实现,该放大器可以实现低的静态功耗开销。该新型D类放大器为未来便携式/可穿戴音频设备提供了一种高精度低功耗的设计思路。第一作者为直博生周凯文,徐佳伟教授和洪志良教授作为指导老师。

6、华东师范大学

实现ISSCC零的突破

通信与电子工程学院(集成电路科学与工程学院)张润曦教授团队

Paper23.1《A 44μW IoT Tag Enabling 1μs Synchronization Accuracy and OFDMA Concurrent Communication with Software-Defined Modulation》展示了一款具有软件定义调制的44μW OFDMA反向散射标签芯片,采用两级同步方法:唤醒接收机和同步接收机,实现了1 μs的同步精度和-51 dBm的射频接收灵敏度。为国际上首次支持多标签无碰撞反向散射传输芯片,并具有微瓦级别功耗,对于物联网设备的广泛部署意义重大。第一作者为硕士生申家齐。

合作单位有上海交通大学电子信息与电气工程学院田晓华教授团队,共同第一作者博士生朱丰源为。

6、华东师范大学

实现ISSCC零的突破

通信与电子工程学院(集成电路科学与工程学院)张润曦教授团队

Paper23.1《A 44μW IoT Tag Enabling 1μs Synchronization Accuracy and OFDMA Concurrent Communication with Software-Defined Modulation》展示了一款具有软件定义调制的44μW OFDMA反向散射标签芯片,采用两级同步方法:唤醒接收机和同步接收机,实现了1 μs的同步精度和-51 dBm的射频接收灵敏度。为国际上首次支持多标签无碰撞反向散射传输芯片,并具有微瓦级别功耗,对于物联网设备的广泛部署意义重大。第一作者为硕士生申家齐。

合作单位有上海交通大学电子信息与电气工程学院田晓华教授团队,共同第一作者博士生朱丰源为。

7、南方科技大学入选5篇

实现ISSCC零的突破

深港微电子学院潘权教授团队入选3篇:高速有线通信方向2篇,之前大陆高校仅有北京大学在此方向发表论文;高密度存储器和接口方向1篇,是中国大陆在ISSCC高密度存储器和接口方向有史以来的首篇论文。

随着全球数据流量吞吐的指数增长,数据中心交换机系统的带宽容量在过去12年里增加了80倍。目前,交换机高速接口要求高速收发机的速率达到每通道224Gb/s。针对224G链路长距高损耗场景下高能效、高密度、低延迟的需求,团队首次提出了基于“XSR/VSR SerDes或retimer+单端收发前端”的长距链路方案,此方案利用单端收发前端实现了高能效和低延迟的损耗补偿和传输距离拓展。此外,发射机和接收机前端电路的连接是基于高密度的单端传输线阵列,这可以帮助实现高密度的布线难题。收发机前端使用了直接耦合的设计,避免了使用大面积的片上或片外隔直电容以支持高密度的Pin口和传输线布局。收发机前端基于高共模抑制的差分和伪差分电路设计,改善单端链路对电源噪声敏感的问题。收发机前端设计了低频/中频/高频的均衡,在不同的损耗场景下均可获得平整的链路响应。发射机和接收机前端分别引入了群时延和电源反弹消除技术。收发机前端选取了SiGe工艺进行设计,充分利用SiGe工艺高增益、低噪声、高摆幅范围的特点以实现高均衡能力、高SNR、高线性度。基于上述创新设计,Paper7.5《A 224Gb/s/wire Single-Ended PAM-4 Transceiver Front-End with 29dB Equalization for 800GbE/1.6TbE》提出了一款基于130nm SiGe工艺的4通道高速单端收发机,并完成了测试验证。此电路在224Gb/s/wire速率下可以实现最高补偿29dB损耗,FOM(能效/损耗)值为0.07pJ/b/dB,误码率低至1E-7。

7、南方科技大学入选5篇

实现ISSCC零的突破

深港微电子学院潘权教授团队入选3篇:高速有线通信方向2篇,之前大陆高校仅有北京大学在此方向发表论文;高密度存储器和接口方向1篇,是中国大陆在ISSCC高密度存储器和接口方向有史以来的首篇论文。

随着全球数据流量吞吐的指数增长,数据中心交换机系统的带宽容量在过去12年里增加了80倍。目前,交换机高速接口要求高速收发机的速率达到每通道224Gb/s。针对224G链路长距高损耗场景下高能效、高密度、低延迟的需求,团队首次提出了基于“XSR/VSR SerDes或retimer+单端收发前端”的长距链路方案,此方案利用单端收发前端实现了高能效和低延迟的损耗补偿和传输距离拓展。此外,发射机和接收机前端电路的连接是基于高密度的单端传输线阵列,这可以帮助实现高密度的布线难题。收发机前端使用了直接耦合的设计,避免了使用大面积的片上或片外隔直电容以支持高密度的Pin口和传输线布局。收发机前端基于高共模抑制的差分和伪差分电路设计,改善单端链路对电源噪声敏感的问题。收发机前端设计了低频/中频/高频的均衡,在不同的损耗场景下均可获得平整的链路响应。发射机和接收机前端分别引入了群时延和电源反弹消除技术。收发机前端选取了SiGe工艺进行设计,充分利用SiGe工艺高增益、低噪声、高摆幅范围的特点以实现高均衡能力、高SNR、高线性度。基于上述创新设计,Paper7.5《A 224Gb/s/wire Single-Ended PAM-4 Transceiver Front-End with 29dB Equalization for 800GbE/1.6TbE》提出了一款基于130nm SiGe工艺的4通道高速单端收发机,并完成了测试验证。此电路在224Gb/s/wire速率下可以实现最高补偿29dB损耗,FOM(能效/损耗)值为0.07pJ/b/dB,误码率低至1E-7。

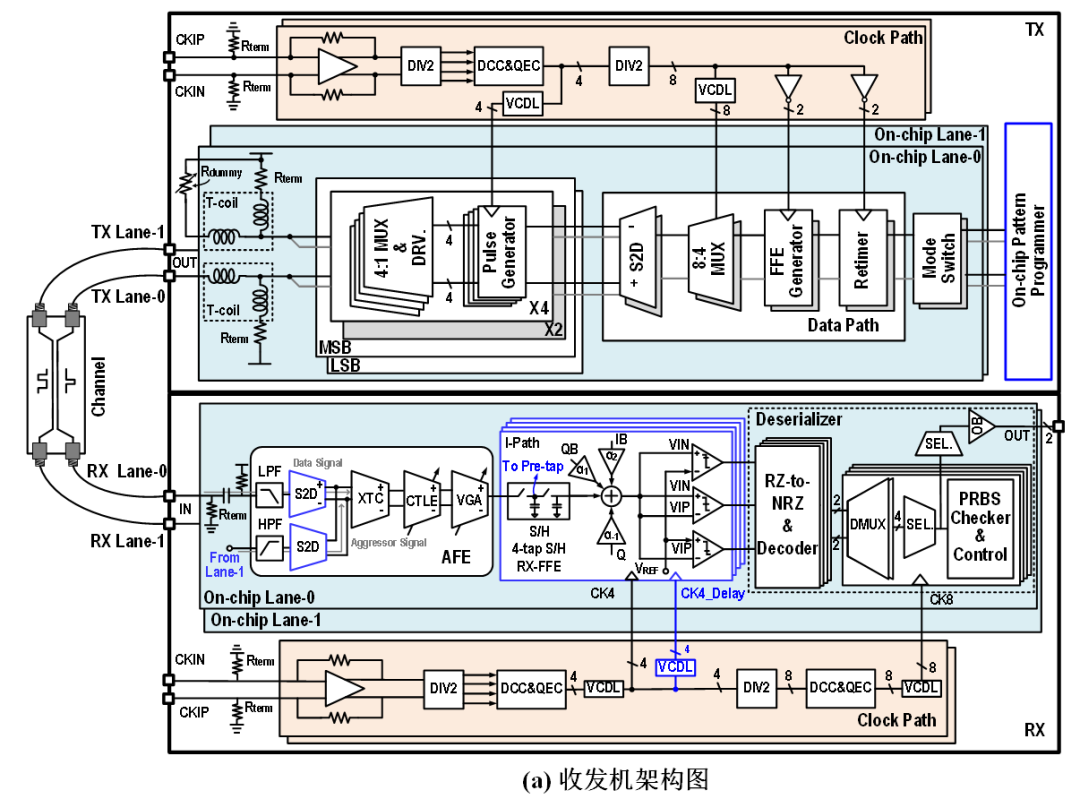

云计算和人工智能等应用的发展,将数据中心的高速接口推向了更高的数据速率,目前超高速有线收发机的数据速率正迫切需要推动到200+Gb/s量级。然而,这个数据速率对无源组件(如连接器、信道和封装)的信号完整性提出了更严格的要求。单端方案可能是数据速率的实用且经济高效的解决方案。首先,它通过一个差分信道传输两路单端信号,使吞吐密度翻倍。此外,该方案还放松了对无源组件的奈奎斯特带宽要求。但是,单端链路遭受了更严重的噪声,特别是长距(LR),中距(MR)和超短距(VSR)链路中引入的串扰噪声。团队从系统架构和电路设计入手,针对复杂的信道环境引入的串扰问题,在发射机中提出可重构串扰消除技术来灵活地处理轻度的感性串扰噪声和容性串扰噪声,接收机采用低功耗的MIMO串扰消除技术处理严重的感性串扰噪声。为了抑制单端电路中的电源噪声等,在接收机侧的第一级使用伪差分架构抑制噪声,后续所有级使用全差分电路架构。为了缓解伪差分失配和提升带宽,该工作提出了Gm-TIA型的单端转差分转换器,使用强弱路径相加和非对称有源电感技术实现优秀的伪差分失配缓解和带宽提升。此外,为了在基于相对落后的28nm CMOS工艺上实现112Gb/s的数据速率,基于多相位时钟技术的接收机侧FFE提出以消除ISI并实现低功耗。基于上述创新设计,Paper7.6《A 112Gb/s/pin Single-Ended Crosstalk-Cancellation Transceiver with 31dB Loss Compensation in 28nm CMOS》提出了一款基于28nm CMOS工艺的超高速单端串扰消除收发机,并进行了测试验证。该芯片在一对差分信道实现了2×112Gb/s,功率效率为2.77pJ/b(发射机为1.56pJ/b,接收机为1.21pJ/b)。它展示了未来800G/1.6T以太网中具有成本效益的解决方案的潜力。

云计算和人工智能等应用的发展,将数据中心的高速接口推向了更高的数据速率,目前超高速有线收发机的数据速率正迫切需要推动到200+Gb/s量级。然而,这个数据速率对无源组件(如连接器、信道和封装)的信号完整性提出了更严格的要求。单端方案可能是数据速率的实用且经济高效的解决方案。首先,它通过一个差分信道传输两路单端信号,使吞吐密度翻倍。此外,该方案还放松了对无源组件的奈奎斯特带宽要求。但是,单端链路遭受了更严重的噪声,特别是长距(LR),中距(MR)和超短距(VSR)链路中引入的串扰噪声。团队从系统架构和电路设计入手,针对复杂的信道环境引入的串扰问题,在发射机中提出可重构串扰消除技术来灵活地处理轻度的感性串扰噪声和容性串扰噪声,接收机采用低功耗的MIMO串扰消除技术处理严重的感性串扰噪声。为了抑制单端电路中的电源噪声等,在接收机侧的第一级使用伪差分架构抑制噪声,后续所有级使用全差分电路架构。为了缓解伪差分失配和提升带宽,该工作提出了Gm-TIA型的单端转差分转换器,使用强弱路径相加和非对称有源电感技术实现优秀的伪差分失配缓解和带宽提升。此外,为了在基于相对落后的28nm CMOS工艺上实现112Gb/s的数据速率,基于多相位时钟技术的接收机侧FFE提出以消除ISI并实现低功耗。基于上述创新设计,Paper7.6《A 112Gb/s/pin Single-Ended Crosstalk-Cancellation Transceiver with 31dB Loss Compensation in 28nm CMOS》提出了一款基于28nm CMOS工艺的超高速单端串扰消除收发机,并进行了测试验证。该芯片在一对差分信道实现了2×112Gb/s,功率效率为2.77pJ/b(发射机为1.56pJ/b,接收机为1.21pJ/b)。它展示了未来800G/1.6T以太网中具有成本效益的解决方案的潜力。

随着海量计算和人工智能应用的发展,对内存接口的数据吞吐量要求不断提高。影响内存接口吞吐量的两个关键指标分别是单通道数据率和通道密度,随着通道间距的减少,串扰导致的信号完整性问题愈发严重,严重限制了通道密度和数据吞吐量的提高,并且GDDR6X等先进DRAM应用已经采用PAM-4信令来提高数据传输速率,PAM-4信号对串扰的敏感性更会加剧这一问题。虽然已经报道了一些发射机串扰消除技术,但这些技术主要集中在NRZ,且存在信噪比低、接口效率低或能耗高的缺点。因此,非常需要一种同时兼顾高信噪比、高接口效率和低功耗的PAM-4串扰消除技术。团队提出了一种集成型预加重电容-峰化串扰消除技术,采用电容阵列生成串扰消除信号不降低输出摆幅,该电路集成在驱动器内部避免发射机输出节点的寄生堆积,支持高速率运行。发射机串行器采用动态逻辑门以减小寄生、提高带宽;采用无静态电流的反相器型数据选择器以降低功耗开销;采用抽头位置调制器通过时钟相位调制实现可重构的3抽头分数间隔前馈均衡,可根据信道特性定制化抽头顺序,并提供超奈奎斯特频率的补偿范围,从而进一步拓展带宽和PAM-4眼图的水平眼宽。此外,在时钟路径上,采用自适应占空比校正器和正交误差校正器消除时钟的偏斜,减少输出抖动。基于上述创新设计,Paper13.5《A 64-Gb/s/pin PAM4 Single-Ended Transmitter with a Merged Pre-Emphasis Capacitive-Peaking Crosstalk Cancellation Scheme for Memory Interfaces in 28nm CMOS》提出了一款基于28nm CMOS工艺的4通道高速PAM-4单端串扰消除发射机,并完成了测试验证。与先前已发表的单端存储器发射机接口相比,本工作实现了最高的数据率64Gb/s/pin,功率效率为1.27pJ/bit,同时达到了82%的串扰引入抖动消除率。据悉,这是中国大陆在ISSCC高密度存储器和接口方向有史以来的首篇论文。

随着海量计算和人工智能应用的发展,对内存接口的数据吞吐量要求不断提高。影响内存接口吞吐量的两个关键指标分别是单通道数据率和通道密度,随着通道间距的减少,串扰导致的信号完整性问题愈发严重,严重限制了通道密度和数据吞吐量的提高,并且GDDR6X等先进DRAM应用已经采用PAM-4信令来提高数据传输速率,PAM-4信号对串扰的敏感性更会加剧这一问题。虽然已经报道了一些发射机串扰消除技术,但这些技术主要集中在NRZ,且存在信噪比低、接口效率低或能耗高的缺点。因此,非常需要一种同时兼顾高信噪比、高接口效率和低功耗的PAM-4串扰消除技术。团队提出了一种集成型预加重电容-峰化串扰消除技术,采用电容阵列生成串扰消除信号不降低输出摆幅,该电路集成在驱动器内部避免发射机输出节点的寄生堆积,支持高速率运行。发射机串行器采用动态逻辑门以减小寄生、提高带宽;采用无静态电流的反相器型数据选择器以降低功耗开销;采用抽头位置调制器通过时钟相位调制实现可重构的3抽头分数间隔前馈均衡,可根据信道特性定制化抽头顺序,并提供超奈奎斯特频率的补偿范围,从而进一步拓展带宽和PAM-4眼图的水平眼宽。此外,在时钟路径上,采用自适应占空比校正器和正交误差校正器消除时钟的偏斜,减少输出抖动。基于上述创新设计,Paper13.5《A 64-Gb/s/pin PAM4 Single-Ended Transmitter with a Merged Pre-Emphasis Capacitive-Peaking Crosstalk Cancellation Scheme for Memory Interfaces in 28nm CMOS》提出了一款基于28nm CMOS工艺的4通道高速PAM-4单端串扰消除发射机,并完成了测试验证。与先前已发表的单端存储器发射机接口相比,本工作实现了最高的数据率64Gb/s/pin,功率效率为1.27pJ/bit,同时达到了82%的串扰引入抖动消除率。据悉,这是中国大陆在ISSCC高密度存储器和接口方向有史以来的首篇论文。

电子与电气工程系姜俊敏教授团队入选2篇

Paper31.7《A 3.6W 16V-Output 180ns-Response-Time 94%-Efficiency SC Sigma Converter with Output Impedance Compensation and Ripple Mitigation for LiDAR Driver Applications》提出了一款用于激光雷达的Sigma构型DC-DC开关电容变换器,采用低压LDO进行稳压,无需电感即实现了5V输入、16V225mA的输出下94%的峰值效率,具有低至180ns的瞬态响应速度和高达44μV/mA的电压精度。

Paper31.9《An 85-264 Vac to 3-4.2 Vdc 1.05W Capacitive Power Converter with Idle Power Reduction and 4-Phase 1/10X SC Converter Achieving 5.11mW Quiescent Power and 78.2% Peak Efficiency》提出了一款用于交流市电的非隔离式AC-DC变换器,包含三模式整流桥和1/10X开关电容变换器,实现了低成本、低待机功耗、高效率、高能量密度的交流-直流转换。

8、清华大学入选13篇

集成电路学院10篇,电子工程系3篇。

集成电路学院尹首一教授-胡杨教授团队入选3篇

Paper15.1《A 0.795-fJ/b Physically-Unclonable-Function-Protected TCAM for Software-Defined Networking Switch 》提出了一种0.795fJ/b物理上不可克隆的功能保护6T-TCAM,用于软件定义的网络交换。

Paper20.2《A 28nm 74.34TFLOPS/W BF16 Heterogenous CIM-Based Accelerator Exploiting Denoising-Similarity for Diffusion Models》提出了一种基于28nm 3.66mm2异构CIM的加速器,该加速器利用扩散模型的去噪相似性,集成了符号幅度基-8布斯CIM核、具有内存冗余搜索消除技术的四操作数指数CIM核和尾数处理引擎。对于Stable Diffusion v1.5(U-net,CelebA 64×64数据集),在0.65V、120MHz下,FP16和BF16的峰值系统能效分别为67.89TFLOPS/W和74.34TFLOPS/W。

Paper34.1《A 28nm 83.23TFLOPS/W POSIT-Based Compute-in-Memory Macro for High-Accuracy AI Application》描述了第一个支持POSIT数字表示格式的数字CIM宏,在28nm工艺中达到83.23TFLOPS/W。

集成电路学院刘雷波教授团队

Paper16.2《A 28nm 69.4kOPS 4.4μJ/Op Versatile Post-Quantum Crypto-Processor Across Multiple Mathematical Problems 》提出了一款28nm 3.2mm2后量子密码(PQC)处理器,支持美国NIST当前所有标准化及第4轮候选算法,覆盖格、编码和哈希等不同数学难题。该芯片密码计算速率达到69 KOps,单次操作能耗仅为4.4μJ。

集成电路学院揭路教授团队

Paper9.3《A 71dB SNDR 200MHz BW Interleaved Pipe-SAR ADC with a Shared Residue Integrating Amplifier Achieving 173dB FoMs》提出了一种采用共享残差积分放大器的200MHz BW 1.6GS/s交错流水线SAR ADC设计,通过噪声整形提高了运算放大器的效率。28nm CMOS中的ADC在13mW中实现了71.2dB的SNDR和173dB的FoMs。

集成电路学院李宇根教授团队

Paper14.7《 A 0.45V 0.72mW 2.4GHz Bias-Current-Free Fractional-N Hybrid PLL Using a Voltage-Mode Phase Interpolator in 28nm CMOS》在28nm CMOS工艺下实现了一款工作在2.4GHz的无偏置电流的混合型分数锁相环。该锁相环在0.45V电压下实现了小于600fs的积分抖动以及-57dBc的最差杂散,功耗为0.72mW,且无内置升压模块。博士生冯礼群为论文第一作者。

集成电路学院贾海昆教授团队

Paper19.5(亮点论文)《 A 13.7-to-41.5GHz 214.1dBc/Hz FoMT Quad-Core Quad-Mode VCO Using an Oscillation-Mode-Splitting Technique》提出了一种四模四核VCO。VCO利用模式分割技术来减少FoM的退化。它的峰值FoMT为214.1dBc/Hz,频率范围为13.7至41.5GHz。第一作者是本科生葛桓羽。

集成电路学院姜汉钧教授团队

Paper29.4《 A Cryo-CMOS Quantum Computing Unit Interface Chipset in 28nm Bulk CMOS with Phase-Detection Based Readout and Phase-Shifter-Based Pulse Generation》展示了一个接口芯片组,该芯片组由控制器和反射式读出装置组成,用于28nm CMOS量子计算。读出ASIC对于两个transmon量子位消耗11mW,而控制器电路在3.5K下每量子位耗费4.3mW。论文第一作者为郭衍束博士。

集成电路学院张雷教授团队

Paper32.4《 A 67.8-to-108.2GHz Power Amplifier with a Three-Coupled-Line-Based Complementary-Gain-Boosting Technique Achieving 442GHz GBW and 23.1% peak PAE》展示了一种65nm CMOS宽带毫米波功率放大器。该PA的-3dB频率范围为67.8至108.2 GHz,峰值功率增益为20.8dB,峰值PAE为23.1%。博士生吴伟平是第一作者。

集成电路学院潘思宁助理教授团队

Paper3.2《A 0.028mm2 32MHz RC Frequency Reference in 0.18μm CMOS with±900ppm Inaccuracy from -40°C to 125°C and ±1600ppm Inaccuracy After Accelerated Aging》介绍了一种基于N-diff电阻器的紧凑型RC频率基准,该基准使用基于BJT的温度补偿电路来抵消RC电路一阶和二阶温度系数。在标准0.18μm工艺下,频率基准面积为0.028mm2,并在加速老化测试后,实现了从-40°C到125°C范围内±1600ppm的精度。

电子工程系孙楠教授团队

Paper22.4《A 4.8GS/s 7-ENoB Time-Interleaved SAR ADC with Dither-Based Background Timing-Skew Calibration and Bit-Distribution-Based Background Ping-Pong Comparator Offset Calibration》介绍了一种4.8GS/s 8b 4×时间交织SAR ADC,该ADC具有基于抖动的背景定时偏斜校准和背景比较器偏移校准。该设计在28nm CMOS中实现,消耗10.4mW,在奈奎斯特达到44.3dB的SNDR,产生6.2fJ/转换步长的FoM,包括输入缓冲器。

电子工程系刘勇攀教授团队

Paper34.7《A 28nm 2.4Mb/mm2 6.9-16.3 TOPS/mm2 eDRAM-LUT-Based Digital Computing-in-Memory Macro with In-Memory Encoding and Refreshing》展示了一款基于eDRAM LUT的DCIM宏。在28nm工艺下,实现了较高的算力密度。

电子工程系张沕琳教授团队

Paper6.9《A 0.35V 0.367TOPS/W Image Sensor with 3-Layer Optical-Electronic Hybrid Convolutional Neural Network》报道了第一个具有3层光电混合卷积神经网络的图像传感器,在采集和计算模式下,在1fps和0.35V电源电压下分别实现了1.579μW和2.351μW的功耗。在32fps时实现了49.02pJ/pix/fps的iFoM,而在1fps时计算能量效率达到0.367TOPS/W。

9、上海交通大学

微电子学院赵健副教授团队

频域近红外光学检测技术(FD-NIRS)通过测量光穿过生物组织前后的强度和飞行时间,推测组织中的代谢物质浓度变化,具有无创、高空间分辨率的优势,在脑机接口、肿瘤筛查、药效监控等领域具有应用前景。然而,相比于车载激光雷达等类似原理的应用场景,生物组织表面进行光飞行时间测量面临距离短(~数厘米)、功耗受限(~数毫瓦)两大挑战,此前少有全集成的专用接口芯片报导。Paper33.10《A 2.7ps-ToF-Resolution and 12.5mW Frequency-domain NIRS Readout IC withDynamic Light Sensing Frontend and Cross-Coupling-Free Inter-Stabilized Data Converter》提出了“全动态的光信号链”技术,借助高占空比的工作模式,使载波信号获得较高的瞬时光功率与载波频率,在有限的功耗开销下实现高分辨率的光延时测量。芯片在180nm工艺下制造,集成光驱动、光电流采集、数据转换等核心模块。经测试,其飞行时间分辨率为2.7皮秒,功耗仅12.5毫瓦,综合指标达到同类工作最优水平。微电子学院马周辰博士生是第一作者,赵健副教授是通讯作者。

10、同济大学

实现ISSCC零的突破

微电子学院孟淼教授团队

Paper12.4《A 19μW 200Mb/s IoT Tag Demonstrating High-Definition Video Streaming via a Digital-Switch-Based reconfigurable 16-QAM Backscatter Communication Technique》展示了一款工作于200Mb/s的数据速率下功耗低至19μW的带有无线唤醒功能基于数字控制的16-QAM(兼容BPSK、QPSK)调制反向散射物联网通信芯片,该芯片的测试结果显示在-42dBm~3dBm输入功率范围内实现稳定的EVM表现,表明该芯片可以稳定的工作于200Mb/s以下的数据传输速率,相较于国际同类型的反向散射芯片具有领先的无线输入功率调制范围和EVM性能,此外,该芯片首次提出基于数字控制的16-QAM调制技术,并结合超低电压锁相环技术成功应用于物联网标签,相较于同类芯片,在提高芯片数据传输速率与频谱效率的同时总功耗降低至少30%。这项工作为国际上首次支持宽输入功率范围的稳定、高数据速率16-QAM并同时兼容BPSK与QPSK调制的超低功耗反向散射通信芯片,对于部署高数据传输速率需求物联网终端设备意义重大。

此论文为同济大学首次以第一作者单位在集成电路设计领域最高级别会议ISSCC上发表正文,实现零的突破。论文第一作者为博士生张永领,孟淼教授为通讯作者,参加芯片研发的还有研究生罗荣亮、熊纪、梁思奇等。

电子与电气工程系姜俊敏教授团队入选2篇

Paper31.7《A 3.6W 16V-Output 180ns-Response-Time 94%-Efficiency SC Sigma Converter with Output Impedance Compensation and Ripple Mitigation for LiDAR Driver Applications》提出了一款用于激光雷达的Sigma构型DC-DC开关电容变换器,采用低压LDO进行稳压,无需电感即实现了5V输入、16V225mA的输出下94%的峰值效率,具有低至180ns的瞬态响应速度和高达44μV/mA的电压精度。

Paper31.9《An 85-264 Vac to 3-4.2 Vdc 1.05W Capacitive Power Converter with Idle Power Reduction and 4-Phase 1/10X SC Converter Achieving 5.11mW Quiescent Power and 78.2% Peak Efficiency》提出了一款用于交流市电的非隔离式AC-DC变换器,包含三模式整流桥和1/10X开关电容变换器,实现了低成本、低待机功耗、高效率、高能量密度的交流-直流转换。

8、清华大学入选13篇

集成电路学院10篇,电子工程系3篇。

集成电路学院尹首一教授-胡杨教授团队入选3篇

Paper15.1《A 0.795-fJ/b Physically-Unclonable-Function-Protected TCAM for Software-Defined Networking Switch 》提出了一种0.795fJ/b物理上不可克隆的功能保护6T-TCAM,用于软件定义的网络交换。

Paper20.2《A 28nm 74.34TFLOPS/W BF16 Heterogenous CIM-Based Accelerator Exploiting Denoising-Similarity for Diffusion Models》提出了一种基于28nm 3.66mm2异构CIM的加速器,该加速器利用扩散模型的去噪相似性,集成了符号幅度基-8布斯CIM核、具有内存冗余搜索消除技术的四操作数指数CIM核和尾数处理引擎。对于Stable Diffusion v1.5(U-net,CelebA 64×64数据集),在0.65V、120MHz下,FP16和BF16的峰值系统能效分别为67.89TFLOPS/W和74.34TFLOPS/W。

Paper34.1《A 28nm 83.23TFLOPS/W POSIT-Based Compute-in-Memory Macro for High-Accuracy AI Application》描述了第一个支持POSIT数字表示格式的数字CIM宏,在28nm工艺中达到83.23TFLOPS/W。

集成电路学院刘雷波教授团队

Paper16.2《A 28nm 69.4kOPS 4.4μJ/Op Versatile Post-Quantum Crypto-Processor Across Multiple Mathematical Problems 》提出了一款28nm 3.2mm2后量子密码(PQC)处理器,支持美国NIST当前所有标准化及第4轮候选算法,覆盖格、编码和哈希等不同数学难题。该芯片密码计算速率达到69 KOps,单次操作能耗仅为4.4μJ。

集成电路学院揭路教授团队

Paper9.3《A 71dB SNDR 200MHz BW Interleaved Pipe-SAR ADC with a Shared Residue Integrating Amplifier Achieving 173dB FoMs》提出了一种采用共享残差积分放大器的200MHz BW 1.6GS/s交错流水线SAR ADC设计,通过噪声整形提高了运算放大器的效率。28nm CMOS中的ADC在13mW中实现了71.2dB的SNDR和173dB的FoMs。

集成电路学院李宇根教授团队

Paper14.7《 A 0.45V 0.72mW 2.4GHz Bias-Current-Free Fractional-N Hybrid PLL Using a Voltage-Mode Phase Interpolator in 28nm CMOS》在28nm CMOS工艺下实现了一款工作在2.4GHz的无偏置电流的混合型分数锁相环。该锁相环在0.45V电压下实现了小于600fs的积分抖动以及-57dBc的最差杂散,功耗为0.72mW,且无内置升压模块。博士生冯礼群为论文第一作者。

集成电路学院贾海昆教授团队

Paper19.5(亮点论文)《 A 13.7-to-41.5GHz 214.1dBc/Hz FoMT Quad-Core Quad-Mode VCO Using an Oscillation-Mode-Splitting Technique》提出了一种四模四核VCO。VCO利用模式分割技术来减少FoM的退化。它的峰值FoMT为214.1dBc/Hz,频率范围为13.7至41.5GHz。第一作者是本科生葛桓羽。

集成电路学院姜汉钧教授团队

Paper29.4《 A Cryo-CMOS Quantum Computing Unit Interface Chipset in 28nm Bulk CMOS with Phase-Detection Based Readout and Phase-Shifter-Based Pulse Generation》展示了一个接口芯片组,该芯片组由控制器和反射式读出装置组成,用于28nm CMOS量子计算。读出ASIC对于两个transmon量子位消耗11mW,而控制器电路在3.5K下每量子位耗费4.3mW。论文第一作者为郭衍束博士。

集成电路学院张雷教授团队

Paper32.4《 A 67.8-to-108.2GHz Power Amplifier with a Three-Coupled-Line-Based Complementary-Gain-Boosting Technique Achieving 442GHz GBW and 23.1% peak PAE》展示了一种65nm CMOS宽带毫米波功率放大器。该PA的-3dB频率范围为67.8至108.2 GHz,峰值功率增益为20.8dB,峰值PAE为23.1%。博士生吴伟平是第一作者。

集成电路学院潘思宁助理教授团队

Paper3.2《A 0.028mm2 32MHz RC Frequency Reference in 0.18μm CMOS with±900ppm Inaccuracy from -40°C to 125°C and ±1600ppm Inaccuracy After Accelerated Aging》介绍了一种基于N-diff电阻器的紧凑型RC频率基准,该基准使用基于BJT的温度补偿电路来抵消RC电路一阶和二阶温度系数。在标准0.18μm工艺下,频率基准面积为0.028mm2,并在加速老化测试后,实现了从-40°C到125°C范围内±1600ppm的精度。

电子工程系孙楠教授团队

Paper22.4《A 4.8GS/s 7-ENoB Time-Interleaved SAR ADC with Dither-Based Background Timing-Skew Calibration and Bit-Distribution-Based Background Ping-Pong Comparator Offset Calibration》介绍了一种4.8GS/s 8b 4×时间交织SAR ADC,该ADC具有基于抖动的背景定时偏斜校准和背景比较器偏移校准。该设计在28nm CMOS中实现,消耗10.4mW,在奈奎斯特达到44.3dB的SNDR,产生6.2fJ/转换步长的FoM,包括输入缓冲器。

电子工程系刘勇攀教授团队

Paper34.7《A 28nm 2.4Mb/mm2 6.9-16.3 TOPS/mm2 eDRAM-LUT-Based Digital Computing-in-Memory Macro with In-Memory Encoding and Refreshing》展示了一款基于eDRAM LUT的DCIM宏。在28nm工艺下,实现了较高的算力密度。

电子工程系张沕琳教授团队

Paper6.9《A 0.35V 0.367TOPS/W Image Sensor with 3-Layer Optical-Electronic Hybrid Convolutional Neural Network》报道了第一个具有3层光电混合卷积神经网络的图像传感器,在采集和计算模式下,在1fps和0.35V电源电压下分别实现了1.579μW和2.351μW的功耗。在32fps时实现了49.02pJ/pix/fps的iFoM,而在1fps时计算能量效率达到0.367TOPS/W。

9、上海交通大学

微电子学院赵健副教授团队

频域近红外光学检测技术(FD-NIRS)通过测量光穿过生物组织前后的强度和飞行时间,推测组织中的代谢物质浓度变化,具有无创、高空间分辨率的优势,在脑机接口、肿瘤筛查、药效监控等领域具有应用前景。然而,相比于车载激光雷达等类似原理的应用场景,生物组织表面进行光飞行时间测量面临距离短(~数厘米)、功耗受限(~数毫瓦)两大挑战,此前少有全集成的专用接口芯片报导。Paper33.10《A 2.7ps-ToF-Resolution and 12.5mW Frequency-domain NIRS Readout IC withDynamic Light Sensing Frontend and Cross-Coupling-Free Inter-Stabilized Data Converter》提出了“全动态的光信号链”技术,借助高占空比的工作模式,使载波信号获得较高的瞬时光功率与载波频率,在有限的功耗开销下实现高分辨率的光延时测量。芯片在180nm工艺下制造,集成光驱动、光电流采集、数据转换等核心模块。经测试,其飞行时间分辨率为2.7皮秒,功耗仅12.5毫瓦,综合指标达到同类工作最优水平。微电子学院马周辰博士生是第一作者,赵健副教授是通讯作者。

10、同济大学

实现ISSCC零的突破

微电子学院孟淼教授团队

Paper12.4《A 19μW 200Mb/s IoT Tag Demonstrating High-Definition Video Streaming via a Digital-Switch-Based reconfigurable 16-QAM Backscatter Communication Technique》展示了一款工作于200Mb/s的数据速率下功耗低至19μW的带有无线唤醒功能基于数字控制的16-QAM(兼容BPSK、QPSK)调制反向散射物联网通信芯片,该芯片的测试结果显示在-42dBm~3dBm输入功率范围内实现稳定的EVM表现,表明该芯片可以稳定的工作于200Mb/s以下的数据传输速率,相较于国际同类型的反向散射芯片具有领先的无线输入功率调制范围和EVM性能,此外,该芯片首次提出基于数字控制的16-QAM调制技术,并结合超低电压锁相环技术成功应用于物联网标签,相较于同类芯片,在提高芯片数据传输速率与频谱效率的同时总功耗降低至少30%。这项工作为国际上首次支持宽输入功率范围的稳定、高数据速率16-QAM并同时兼容BPSK与QPSK调制的超低功耗反向散射通信芯片,对于部署高数据传输速率需求物联网终端设备意义重大。

此论文为同济大学首次以第一作者单位在集成电路设计领域最高级别会议ISSCC上发表正文,实现零的突破。论文第一作者为博士生张永领,孟淼教授为通讯作者,参加芯片研发的还有研究生罗荣亮、熊纪、梁思奇等。

芯片显微图

芯片显微图

芯片的性能测试和无线应用功能演示图

11、西安交通大学

微电子学院耿莉教授-樊超老师团队

毫米波低噪声多相位时钟信号在无线通讯和高速有线通系统中有着十分重要的应用场景。传统的8相位多核振荡器电路采用电容耦合或者有源晶体管耦合的设计方案,其有限的耦合强度和晶体管的噪声注入使得多相位输出信号的相位噪声和相位精度性能较差;同时,多个独立的电感占用较大的芯片面积。针对毫米波多相位频率源芯片在相位噪声、相位精度和芯片面积效率等方面的设计折中,Paper19.4《A 0.07mm2 20-to-23.8GHz 8-phase Oscillator Incorporating Magnetic + Dual-Injection Coupling Achieving 189.2dBc/Hz FoM@10MHz and 200.7dBc/Hz FoMA in 65nm CMOS》采用“磁耦合+双注入耦合”电路结构,并结合风车型变压器模型,利用自身多相位信号相互注入锁定,有效增强多核振荡器间的耦合强度,提升多相位输出信号相位精度。同时,注入锁定的尾电流晶体管减小流入谐振腔的噪声电流,有效降低输出信号的相位噪声,实现189.2dBc/Hz FoM。风车型变压器集成多核振荡器,显著提升芯片面积效率,实现200.7dBc/Hz FoMA。论文一作是博士生赵亚,通讯作者是樊超老师和耿莉教授。

12、香港中文大学(深圳)入选2篇

实现ISSCC零的突破

刘寻教授团队

paper8.3《A Li-ion-Battery-Input 1-to-6V-Output Bootstrap-Free Hybrid Buck-orBoost Converter Without RHP Zero Achieving 97.3% Peak Efficiency 6μs Recovery Time and 1.13μs/V DVS Rate》提出了一种应用于功放平均电压跟踪技术的降压-升压变换器,实现了宽范围电压转换比和快速负载电流响应和快速动态电压跟踪的效果。合作单位南方科技大学姜俊敏教授团队。第一作者阮珺逸荣获ISSCC2024丝绸之路奖(Silk Road Award)。

吴亮教授团队

paper19.3《An 8.9-to-21.9GHz Single-Core Oscillator with Reconfigurable Class-F–1 and Enhanced-Colpitts Dual-Mode Operation Achieving 209dBc/Hz FoMT》提出了一种可在逆F类振荡器和考毕兹振荡器之间重构的单核双模式振荡器。在差模工作时,二次谐波频率处的高阻抗峰可进行谐波整形,达到压制相位噪声的目的;在共模工作时,顶部电感并入电路,有效提升谐振器的品质因数并增大电压摆幅,从而降低相位噪声。测试结果表明,采用40nm CMOS工艺加工的振荡器原型达到了14.16至21.92GHz的调谐范围和184.8-190.5dBc/Hz的FoMT。

13、浙江大学入选2篇

集成电路学院赵博教授团队入选2篇

Paper23.3(亮点论文)《A Passive Crystal-Less Wi-Fi-to-BLE Tag Demonstrating Battery-Free FDD Communication with Smartphones》提出了一种相位翻转跟踪技术和一种相位补偿反向散射技术,同时实现 Wi-Fi解调和 BLE 反射的双向通信,芯片无需电池、无需片外晶振。据悉这是目前国际上唯一一款能将 Wi-Fi 信号反射成BLE 信号的零功耗通信芯片。博士生常子怡、肖起京是共同一作。

芯片的性能测试和无线应用功能演示图

11、西安交通大学

微电子学院耿莉教授-樊超老师团队

毫米波低噪声多相位时钟信号在无线通讯和高速有线通系统中有着十分重要的应用场景。传统的8相位多核振荡器电路采用电容耦合或者有源晶体管耦合的设计方案,其有限的耦合强度和晶体管的噪声注入使得多相位输出信号的相位噪声和相位精度性能较差;同时,多个独立的电感占用较大的芯片面积。针对毫米波多相位频率源芯片在相位噪声、相位精度和芯片面积效率等方面的设计折中,Paper19.4《A 0.07mm2 20-to-23.8GHz 8-phase Oscillator Incorporating Magnetic + Dual-Injection Coupling Achieving 189.2dBc/Hz FoM@10MHz and 200.7dBc/Hz FoMA in 65nm CMOS》采用“磁耦合+双注入耦合”电路结构,并结合风车型变压器模型,利用自身多相位信号相互注入锁定,有效增强多核振荡器间的耦合强度,提升多相位输出信号相位精度。同时,注入锁定的尾电流晶体管减小流入谐振腔的噪声电流,有效降低输出信号的相位噪声,实现189.2dBc/Hz FoM。风车型变压器集成多核振荡器,显著提升芯片面积效率,实现200.7dBc/Hz FoMA。论文一作是博士生赵亚,通讯作者是樊超老师和耿莉教授。

12、香港中文大学(深圳)入选2篇

实现ISSCC零的突破

刘寻教授团队

paper8.3《A Li-ion-Battery-Input 1-to-6V-Output Bootstrap-Free Hybrid Buck-orBoost Converter Without RHP Zero Achieving 97.3% Peak Efficiency 6μs Recovery Time and 1.13μs/V DVS Rate》提出了一种应用于功放平均电压跟踪技术的降压-升压变换器,实现了宽范围电压转换比和快速负载电流响应和快速动态电压跟踪的效果。合作单位南方科技大学姜俊敏教授团队。第一作者阮珺逸荣获ISSCC2024丝绸之路奖(Silk Road Award)。

吴亮教授团队

paper19.3《An 8.9-to-21.9GHz Single-Core Oscillator with Reconfigurable Class-F–1 and Enhanced-Colpitts Dual-Mode Operation Achieving 209dBc/Hz FoMT》提出了一种可在逆F类振荡器和考毕兹振荡器之间重构的单核双模式振荡器。在差模工作时,二次谐波频率处的高阻抗峰可进行谐波整形,达到压制相位噪声的目的;在共模工作时,顶部电感并入电路,有效提升谐振器的品质因数并增大电压摆幅,从而降低相位噪声。测试结果表明,采用40nm CMOS工艺加工的振荡器原型达到了14.16至21.92GHz的调谐范围和184.8-190.5dBc/Hz的FoMT。

13、浙江大学入选2篇

集成电路学院赵博教授团队入选2篇

Paper23.3(亮点论文)《A Passive Crystal-Less Wi-Fi-to-BLE Tag Demonstrating Battery-Free FDD Communication with Smartphones》提出了一种相位翻转跟踪技术和一种相位补偿反向散射技术,同时实现 Wi-Fi解调和 BLE 反射的双向通信,芯片无需电池、无需片外晶振。据悉这是目前国际上唯一一款能将 Wi-Fi 信号反射成BLE 信号的零功耗通信芯片。博士生常子怡、肖起京是共同一作。

Paper26.5《A 977μW Capacitive Touch Sensor with Noise-Immune Excitation Source and Direct Lock-In ADC Achieving 25.2pJ/step Energy Efficiency高能效触摸屏读取芯片》提出了一种噪声免疫激励技术和直接锁定ADC技术,消除了传统触摸屏读取信号链中的带通滤波器、混频器和低通滤波器,显著降低了功耗,实现了25.2pJ/step的高能效。博士生冯向东是第一作者。

Paper26.5《A 977μW Capacitive Touch Sensor with Noise-Immune Excitation Source and Direct Lock-In ADC Achieving 25.2pJ/step Energy Efficiency高能效触摸屏读取芯片》提出了一种噪声免疫激励技术和直接锁定ADC技术,消除了传统触摸屏读取信号链中的带通滤波器、混频器和低通滤波器,显著降低了功耗,实现了25.2pJ/step的高能效。博士生冯向东是第一作者。

14、中国科技大学入选5篇

微电子学院程林教授团队入选5篇

创下中国大陆单课题组单年入选篇数最高记录!值得庆祝的是,5篇论文有4篇入选亮点(Highliahts)文章。

也是程林教授团队连续四年发表论文,累计发布9篇。

Paper8.1(亮点论文)《A 94.5%-Peak-Efficiency3.99W/mm2-Power-Density Single-lnductor Bipolar-Output Converter with a Concise PWM Control for AMOLED Displays》:针对现有AMOLED供电芯片低效率、低功率密度的问题,论文提出了一种新型单电感双极性输出(SIBO)转换器拓扑结构,显著降低电感的电流应力和功率管的电压应力,实现了当前最高的94.5%的峰值效率和3.99W/mm2功率密度。同时还针对SIBO转换器提出了一种简洁的PWM控制方案,实现了高鲁棒性和快速瞬态响应。该工作为AMOLED屏幕高效供电提供了一种高效高功率密度的解决方案。论文合作单位为乘翎微电子有限公司,第一作者为博士生靳吉。

Paper27.2(亮点论文)《A 6.78-MHz 79.5%-Peak-Efficiency Wireless Power Transfer System using aWireless Mode-Recognition Technique and a Fully-On/off Class-D Power Amplifier》针对无线充电系统在轻载下传输效率低的问题,论文提出了一种能够根据负载变化自适应地完全开启/关闭发射端的功率放大器的控制方法,并且收发系统不需要额外的通讯组件。在轻载时可将系统效率最高提高20.1%,并且实现了当前最高的端到端峰值效率79.5%。第一作者为博士生葛俊飞。

Paper28.2(亮点论文)《A 12V-Input 1V-1.8V-Output 94.7%-Peak-Efficiency 685A/cm3-Current-Density Hybrid DC-DC Converter with a Charge Converging Phase》针对12V供电系统,论文提出一款新型混合拓扑架构,通过引入电荷汇聚相位,将电感均值电流在全转换比范围降低至负载电流一半以下,电感损耗得到充分降低。因此本方案仅需采用2016系列的小尺寸电感(2mm×1.6mm×1mm),以最小的片外无源器件尺寸与成本,实现了当前最高的效率94.7%与最高的电流密度685A/cm3。第一作者为博士生季逸超。

Paper31.1(亮点论文)《An 83.4%-Peak-EfficiencyEnvelope-Tracking Supply Modulator Using a Class-GLinear Amplifier and a Single-Inductor Dual-Input-Dual-Output Converter for 200MHz Bandwidth 5G New Radio RF Applications》针对5G应用下射频信号的包络带宽高、摆幅大,功率放大器的去耦电容高频充放电电流大,导致电源调制器效率低的问题,论文提出了一种新型的混合结构包络跟踪电源调制器,通过采用G类线性放大器和单电感双输入双输出转换器,有效降低了电流在线性放大器输出晶体管的平均电压降,提升了系统效率。并且G类线性放大器可在高低电源轨之间平滑过渡,保证了高线性度和低失真。该设计在同时满足200MHz跟踪带宽,200pF负载电容和1V~5V大输出摆幅的条件下,实现了当前最高的83.4%的峰值效率。第一作者为博士生陈昶金。

Paper31.8《A 11.7W 9mV/A-Cross-Regulation Single-Inductor Triple-Output Buck Converter using Unordered Power-Distributive Control for a 2A Load Transient》针对单电感多输出(SIMO)直流-直流转换器长期存在的交叉调整问题,论文提出了一种变序能量分配的控制技术以应对剧烈的瞬态变化,并且无需空转周期作为缓冲。该技术使得SIMO转换器在2A的快速负载跳变下,实现了当前最小的9mV/A的交叉调整,最大输出功率可达11.7W。第一作者为硕士生王保创。

15、中科院微电子所入选2篇

来自刘明院士团队。

Paper34.6《A 28nm 72.12-TFLOPS/W Hybrid-Domain Outer-Product Based Floating-Point SRAM Computing-in-Memory Macro with Logarithm Bit-Width Folding ADC》设计了一种数模混合浮点 SRAM 存内计算方案,提出了模拟与数字存算宏的混合方法,在28nm CMOS工艺下流片,可以支持BF16浮点精度运算以及INT8定点精度运算,BF16浮点矩阵-矩阵-向量计算峰值能效达到了72.12TFLOP/W,INT8定点矩阵-矩阵-向量计算峰值能效达到了111.17TFLOP/W。

14、中国科技大学入选5篇

微电子学院程林教授团队入选5篇

创下中国大陆单课题组单年入选篇数最高记录!值得庆祝的是,5篇论文有4篇入选亮点(Highliahts)文章。

也是程林教授团队连续四年发表论文,累计发布9篇。

Paper8.1(亮点论文)《A 94.5%-Peak-Efficiency3.99W/mm2-Power-Density Single-lnductor Bipolar-Output Converter with a Concise PWM Control for AMOLED Displays》:针对现有AMOLED供电芯片低效率、低功率密度的问题,论文提出了一种新型单电感双极性输出(SIBO)转换器拓扑结构,显著降低电感的电流应力和功率管的电压应力,实现了当前最高的94.5%的峰值效率和3.99W/mm2功率密度。同时还针对SIBO转换器提出了一种简洁的PWM控制方案,实现了高鲁棒性和快速瞬态响应。该工作为AMOLED屏幕高效供电提供了一种高效高功率密度的解决方案。论文合作单位为乘翎微电子有限公司,第一作者为博士生靳吉。

Paper27.2(亮点论文)《A 6.78-MHz 79.5%-Peak-Efficiency Wireless Power Transfer System using aWireless Mode-Recognition Technique and a Fully-On/off Class-D Power Amplifier》针对无线充电系统在轻载下传输效率低的问题,论文提出了一种能够根据负载变化自适应地完全开启/关闭发射端的功率放大器的控制方法,并且收发系统不需要额外的通讯组件。在轻载时可将系统效率最高提高20.1%,并且实现了当前最高的端到端峰值效率79.5%。第一作者为博士生葛俊飞。

Paper28.2(亮点论文)《A 12V-Input 1V-1.8V-Output 94.7%-Peak-Efficiency 685A/cm3-Current-Density Hybrid DC-DC Converter with a Charge Converging Phase》针对12V供电系统,论文提出一款新型混合拓扑架构,通过引入电荷汇聚相位,将电感均值电流在全转换比范围降低至负载电流一半以下,电感损耗得到充分降低。因此本方案仅需采用2016系列的小尺寸电感(2mm×1.6mm×1mm),以最小的片外无源器件尺寸与成本,实现了当前最高的效率94.7%与最高的电流密度685A/cm3。第一作者为博士生季逸超。

Paper31.1(亮点论文)《An 83.4%-Peak-EfficiencyEnvelope-Tracking Supply Modulator Using a Class-GLinear Amplifier and a Single-Inductor Dual-Input-Dual-Output Converter for 200MHz Bandwidth 5G New Radio RF Applications》针对5G应用下射频信号的包络带宽高、摆幅大,功率放大器的去耦电容高频充放电电流大,导致电源调制器效率低的问题,论文提出了一种新型的混合结构包络跟踪电源调制器,通过采用G类线性放大器和单电感双输入双输出转换器,有效降低了电流在线性放大器输出晶体管的平均电压降,提升了系统效率。并且G类线性放大器可在高低电源轨之间平滑过渡,保证了高线性度和低失真。该设计在同时满足200MHz跟踪带宽,200pF负载电容和1V~5V大输出摆幅的条件下,实现了当前最高的83.4%的峰值效率。第一作者为博士生陈昶金。

Paper31.8《A 11.7W 9mV/A-Cross-Regulation Single-Inductor Triple-Output Buck Converter using Unordered Power-Distributive Control for a 2A Load Transient》针对单电感多输出(SIMO)直流-直流转换器长期存在的交叉调整问题,论文提出了一种变序能量分配的控制技术以应对剧烈的瞬态变化,并且无需空转周期作为缓冲。该技术使得SIMO转换器在2A的快速负载跳变下,实现了当前最小的9mV/A的交叉调整,最大输出功率可达11.7W。第一作者为硕士生王保创。

15、中科院微电子所入选2篇

来自刘明院士团队。

Paper34.6《A 28nm 72.12-TFLOPS/W Hybrid-Domain Outer-Product Based Floating-Point SRAM Computing-in-Memory Macro with Logarithm Bit-Width Folding ADC》设计了一种数模混合浮点 SRAM 存内计算方案,提出了模拟与数字存算宏的混合方法,在28nm CMOS工艺下流片,可以支持BF16浮点精度运算以及INT8定点精度运算,BF16浮点矩阵-矩阵-向量计算峰值能效达到了72.12TFLOP/W,INT8定点矩阵-矩阵-向量计算峰值能效达到了111.17TFLOP/W。

28nm 基于外积的数模混合浮点存算一体宏芯片:(a)芯片显微镜照片,(b)芯片特性总结表

Paper34.9《A Flash-SRAM-ADC Fused Plastic Computing-in-Memory Macro for Learning in Neural Networks in a Standard 14nm FinFET Process》设计了基于非易失/易失存储融合型的片上学习存算一体宏芯片。在14nm FinFET工艺下流片,可以实现小样本学习等片上学习任务,8比特矩阵-矩阵-向量计算能效达到了22.64TOP/W。

28nm 基于外积的数模混合浮点存算一体宏芯片:(a)芯片显微镜照片,(b)芯片特性总结表

Paper34.9《A Flash-SRAM-ADC Fused Plastic Computing-in-Memory Macro for Learning in Neural Networks in a Standard 14nm FinFET Process》设计了基于非易失/易失存储融合型的片上学习存算一体宏芯片。在14nm FinFET工艺下流片,可以实现小样本学习等片上学习任务,8比特矩阵-矩阵-向量计算能效达到了22.64TOP/W。

14nm FinFET非易失-易失融合型片上学习存算一体芯片:(a)显微镜照片,(b)非易失逻辑闪存单元编程电压与时间对比,(c)工作频率与计算能效

16、中山大学

来自微电子学院郭建平教授团队

Paper27.5《A Wireless Power Transfer System with Up-to-27.9% Efficiency Improvement under Coupling Coefficient Ranging from 0.1 to 0.39 Based on Phase-Shift/Time-Constant Detection and Hybrid Transmission Power Control》提出了一款适用于宽耦合系数范围的高效率谐振式无线能量传输系统,包括发射芯片和接收芯片。该论文提出一种相移与时间常数识别技术,突破了传统幅值识别技术的适用范围限制,配合提出的混合式发射功率控制技术,在宽耦合系数范围内实现了高能量转换效率,获得了最高28%的效率提升和74.3%的峰值效率,实现了高自由度、高效率的无线传能系统。论文第一作者为中山大学电子与信息工程学院(微电子学院)2023级博士生陈宇棠同学,通讯作者为郭建平教授。

14nm FinFET非易失-易失融合型片上学习存算一体芯片:(a)显微镜照片,(b)非易失逻辑闪存单元编程电压与时间对比,(c)工作频率与计算能效

16、中山大学

来自微电子学院郭建平教授团队

Paper27.5《A Wireless Power Transfer System with Up-to-27.9% Efficiency Improvement under Coupling Coefficient Ranging from 0.1 to 0.39 Based on Phase-Shift/Time-Constant Detection and Hybrid Transmission Power Control》提出了一款适用于宽耦合系数范围的高效率谐振式无线能量传输系统,包括发射芯片和接收芯片。该论文提出一种相移与时间常数识别技术,突破了传统幅值识别技术的适用范围限制,配合提出的混合式发射功率控制技术,在宽耦合系数范围内实现了高能量转换效率,获得了最高28%的效率提升和74.3%的峰值效率,实现了高自由度、高效率的无线传能系统。论文第一作者为中山大学电子与信息工程学院(微电子学院)2023级博士生陈宇棠同学,通讯作者为郭建平教授。

17、万高科技

ISSCC2024唯一一篇来自内地产业界的文章

Paper3.4(亮点论文)《A 14b 98Hz-to-5.9kHz1.7-to-50.8uW BW/Power Scalable Sensor Interfacewith a Dynamic Bandgap Reference and anUntrimmed Gain Error of +0.26% from -40°C to125°C》论文介绍了一个可拓展传感器接口。研究创新点是通盘考虑了模数转换器的内核、外围电路,对整个系统做了新的架构方案,目的是为了在不同复杂的应用场景下仍然保持了高能效高精度。这篇论文是万高科技和浙江大学、代尔夫特理工大学一起合作的成果。

17、万高科技

ISSCC2024唯一一篇来自内地产业界的文章

Paper3.4(亮点论文)《A 14b 98Hz-to-5.9kHz1.7-to-50.8uW BW/Power Scalable Sensor Interfacewith a Dynamic Bandgap Reference and anUntrimmed Gain Error of +0.26% from -40°C to125°C》论文介绍了一个可拓展传感器接口。研究创新点是通盘考虑了模数转换器的内核、外围电路,对整个系统做了新的架构方案,目的是为了在不同复杂的应用场景下仍然保持了高能效高精度。这篇论文是万高科技和浙江大学、代尔夫特理工大学一起合作的成果。

写在最后

最近几年,中国内地高校在ISSCC入选论文数量大爆发,一是内地高校在IC领域的沉淀积累到了临界点;二是海外回国人员增多! 接下来,我们就不单纯统计数量,而是要统计highlights数量了,要有更多的原创性idea。