智能汽车安全新媒体

接口(interface)是模块间、芯片间以及芯片与外设进行通信以及数据传输的必备结构。

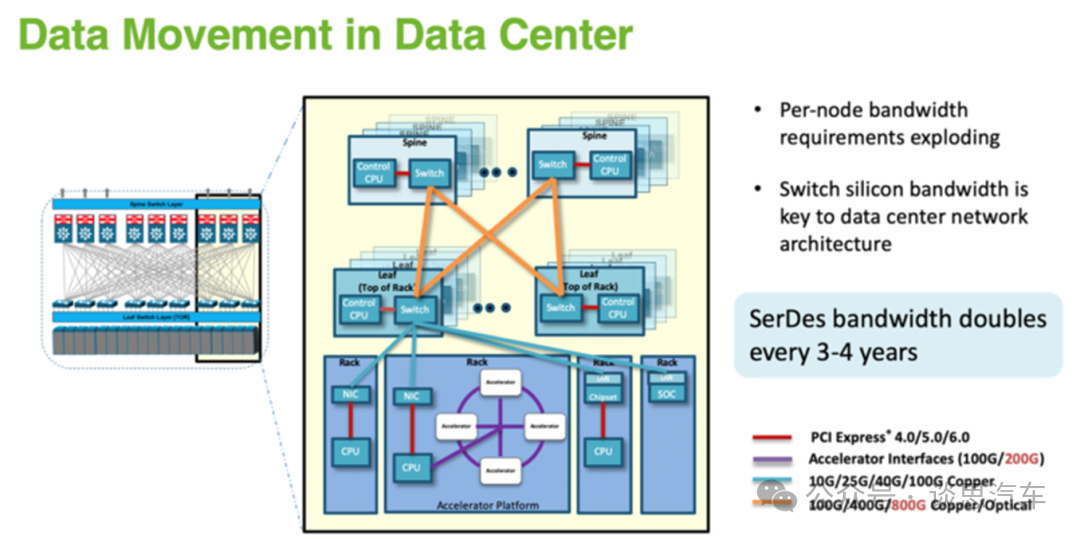

数据量的增长对更快的服务器接口提出了需求,因为在服务器内部和服务器之间需要搬运大量数据。服务器内的数据移动可能是主要的瓶颈,也是延时的根源。

要提高性能,所有内部服务器接口都在进行升级:

如DDR5接口速度提高到6400Mbps;

NVMe SSD正从PCIe3.0转向PCIe5.0,带宽增加四倍;

CXL提供了PCIe电接口上运行的缓存一致性接口,并允许多个处理器共享数据和内存,从而减少系统中需要移动的数据量;

通过采用PAM4编码并支持多协议的56Gbps和112Gbps新型高速Serdes技术。

Serdes是Serializer/Deserializer的缩写。它是一种时分多路复用(TDM)、点对点的通信技术,即在发送端多路低速并行信号被转换成高速串行信号,经过传输媒体(光缆或铜线),最后在接收端高速串行信号重新转换成低速并行信号。

这种点对点的串行通信技术充分利用介质的信道容量,减少所需的传输信道和器件引脚数目,从而减少了传输线之间的干扰,增大了背板传输距离,并且大大降低通信成本。同时带来了诸如减少布线冲突、降低开关噪声、更低的功耗和封装成本等许多好处。

而 Serdes技术的主要缺点是需要非常精确、超低抖动的元件来提供用于控制高数据速率串行信号所需的参考时钟。

已经有许多文章详细描述过Serdes变得越来越重要甚至不可或缺的原因,本文主要介绍高速Serdes技术的应用场景与目前面临的难点。

01

高速Serdes

高速 Serdes IP及相关技术,包括基于DSP的 112G/56GSerdes、PCI-Express(支持 PCI-EGen5/6)、ReTimer、D2D(die-to-die interface)等,被广泛地应用在各种电路与光纤通信技术中。

可以说,所有的高速器件都是使用Serdes的串行组件连接,转化为最终接收器的数据。国际领先的制造商已推出数据率56Gbps 及以上的 PAM-4 Serdes,来支持 100Gbps+数据率的以太网设计。由于 Serdes 应用广泛且至关重要,每个厂商都格外重视。

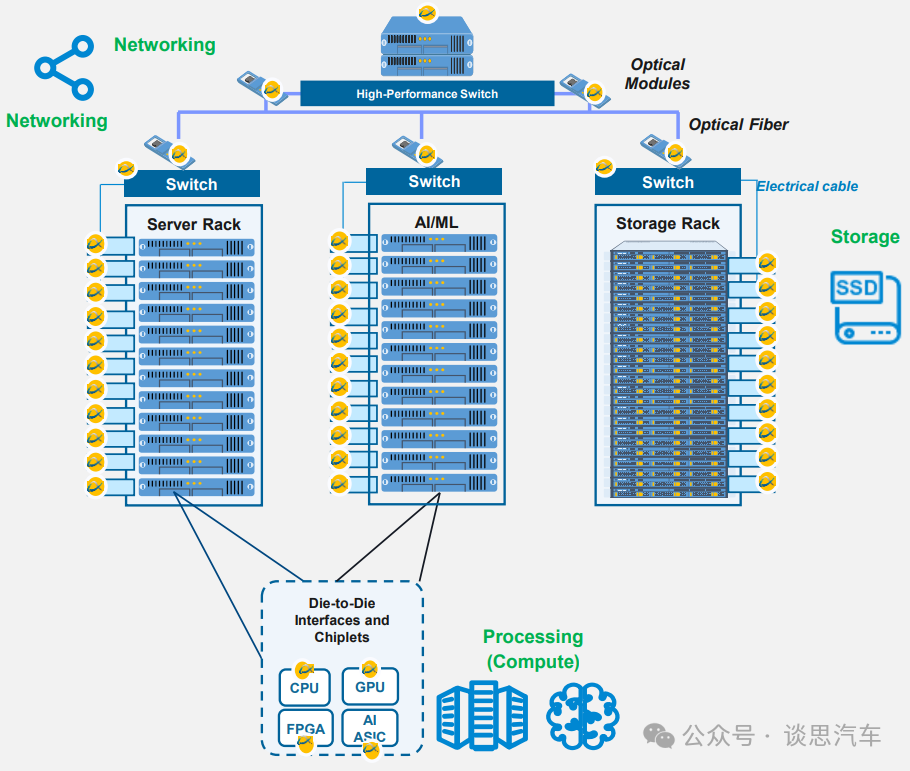

下图为在数据中心内部,高速数据传输的典型应用场景,包括处理计算(CPU、GPU、FPGA、AI)、网络(网卡、Switch、光模块及线缆)以及存储:

通常在56Gbit/s以下的应用可以采用传统的NRZ编码,56Gbit/s以上的应用需要考虑采用PAM-4编码,通过牺牲信号的幅度来换取时序上的宽裕。因此,Serdes架构有了很大变化,通常会采用DSP和高速ADC等技术来处理PAM-4编码。

一个完整的Serdes系统,包括参考时钟、PLL、上层协议、编解码、发送端 (TX)、信道(Channel)、接收端(RX)等部分组成,Serdes通常作为phy芯片或者集成在IP核中。

接下来主要介绍高速Serdes IP主要典型应用场景:芯片与芯片的互联(如在PCIe/CXLPHY中)、以太网互连(如在Ethernet switch PHY)以及芯片与光模块的互联(如在ODSP PHY中)。

应用一:具有PCIe/CXL链路通信功能的芯片

下一代外设、平板电脑、服务器和其他应用都要求以更低的成本和功率获得更大的带宽。为了满足这些需求,像PCIe这样的通信协议已经大大加快了速度——PCIe 4.0要求信号传输速度达到16Gbps;在存储应用中使用缓存一致性接口Compute Express Link (CXL) 可以使多个设备在共享内存时保持缓存一致性,从而提高性能,并减少数据移动。

基于PCIe 5.0 的CXL1.1 以32GT/s的速度为缓存、内存和I/O设备提供数据传输。NVMe存储设备纷纷采用PCIe5.0 接口,将 SSD吞吐量提高到每个PCIe通道 4GB/s,比PCIe3.0速度提高了4倍,目前,x86服务器中一般都应用了 PCIe3.0。

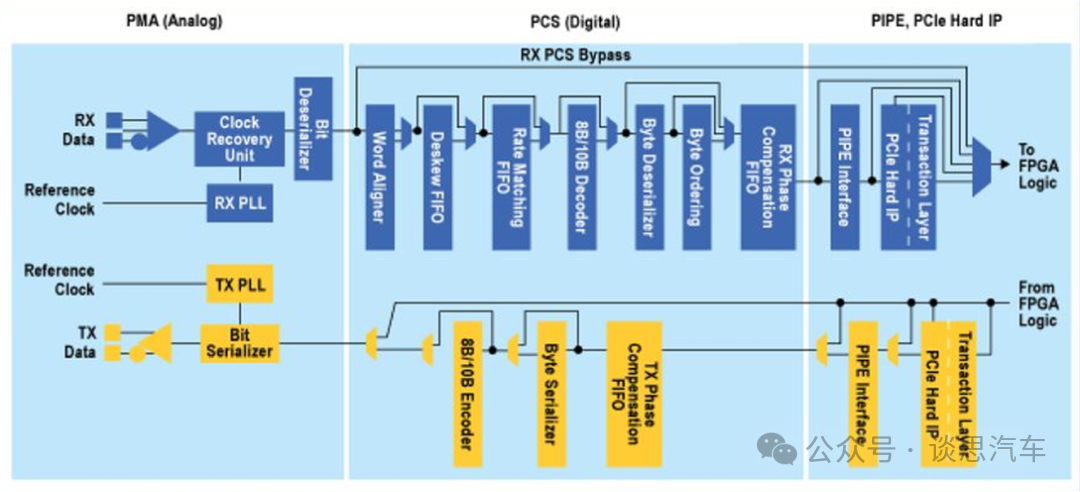

目前高速串行链路数据通信协议都是基于Serdes:Serdes协议的主要作用是把数据实现串并转换,但是PCIe、CXL等协议则是完整的协议,包含物理层、链路层等,其中的物理层PHY就是Serdes协议实现的。

因此,希望具备PCIe/CXL链路通信功能的processing芯片(如FPGA想要与CPU进行通信)都与要集成相应的Controller和PHY IP模块,此外也包括PCIe Switch交换芯片、PCIe Retimer芯片。

PHY本身可以分成:PIPE接口+PCS(物理编码子层)+PMA(Serdes功能),框图如下。PCIe 6.0的主要变化包括从NRZ编码转换到PAM-4编码,以及由此带来的纠错影响,大多数设计将采用基于新PIPE 6.0规范的Serdes架构PIPE接口。

下图为一个服务器的典型框图,该服务器分别配备采用 CXL 和 PCIe 的一致性和非一致性 I/O 接口,以及一个大容量 DDR5 内存接口:

应用二:Ethernet PHY

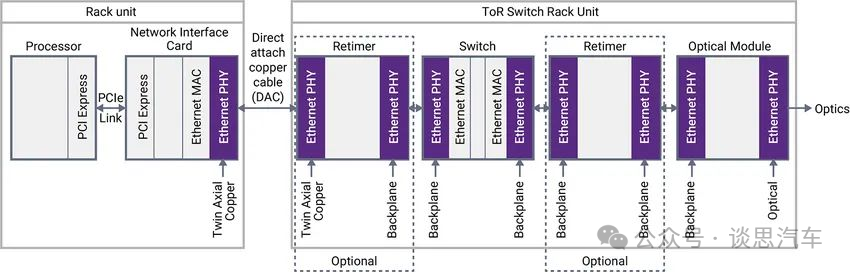

数据增长对网络速度提出了更高的要求。许多数据中心正在将从服务器到架顶(ToR)交换机的网络接口速度从25GbE提高到100GbE。

支持 400Gbps以太网端口的基础架构交换机可采用56Gx8或112Gx4 Serdes电接口,领先的以太网交换机厂商已经在开发基于112G Serdes的800Gbps交换机,而且随着数据量的持续增长,未来几年可能会推出1.6Tbps以太网。

目前国际领先的交换机厂商包括Cisco、Huawei、Arista、Juniper等。

下图为数据包从服务器中的Rack移动到ToR交换机的移动过程:

其中以太网PHY就由PCS与Serdes组成,下图为支持 400Gbps以太网端口的基础架构交换机SoC示意图:

应用三:ODSP PHY芯片

如前所述,ToR 交换机对数据帧进行路由后,光模块则通过实现电气和光学 PHY 功能将媒介从电转换为光。200G以上的光模块中,每一个光电模块都需要一颗单独的PAM4 DSP电芯片对信号进行整形和恢复,以保障数据传输的误码率。

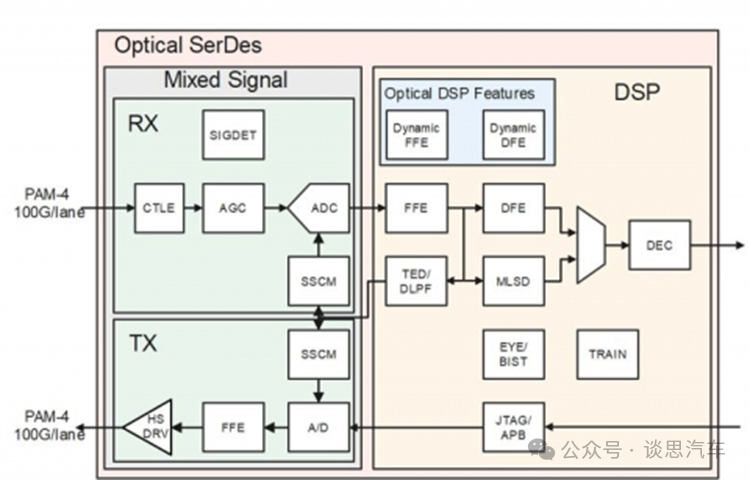

Optical Serdes IP模块集成在光模块中的DSP PHY芯片当中,目前112G ODSP PHY芯片玩家主要被Broadcom、Inphi(Marvell)两家垄断,且受良率的限制产能紧缺。

下图为Alphawave的集成Driver与Optical Serdes的Serdes IP框图:

此外,近期引发话题的Chiplet技术中也有运用到高速Serdes(通常是基于XSR/USR标准),尤其是在对带宽要求高的IO die中。

02

高速Serdes IP的发展挑战

1、设计复杂度高

Serdes是典型的数模混合电路,整个Serdes系统需要一个熟练的模拟/混合信号设计团队来完成。在速度大于56Gbps时,随着PAM-4DSP技术的使用,同样的28ghz带宽信道现在可以支持112gbps的数据速率,但是PAM4信号对噪声、反射、非线性和基线漂移更加敏感,接收器设计要更加复杂。

难点包括高频低抖动时钟的生成(Tx PLL的设计、各种各样的jitter对BER的影响)、信号完整性考虑(如Tx的FFE、Rx的CTLE和DFE)、Rx的CDR实现环路等等;这里面除了模拟电路设计之外,内部还包含了大量数字实现内容:编解码实现、PRBS生成和检查、环回测试、自适应算法实现、系统状态控制数字实现等;

往往客户应用前,都会用有spec的test case从不同维度对IP来进行performance评价,如Tx swing、Die loss、 Jitters、Eye diagram、BER等等。从测试特性来看,会包括延时、自适应能力、power intent、PVT补偿、插损、对时钟方案支持的多样性、形状、面积、功耗等。

2、对先进工艺的依赖性

上一代Serdes往往都是以传统模拟方式实现,从16nm开始,在速度大于56Gbps时,收发器已经转向基于ADC/ DSP的策略,其中有很大一部分仍为模拟电路,但还有接近50%的电路是数字电路。因此,当应用到更加先进节点时,面积和功耗会有一定程度的改善。

目前Synopsys的112G Serdes IP是5nm制程,ISSCC2023 Program中关于Serdes的研究也是有关在112G的速度上进行功耗优化、均衡能力提升等。因此未来Serdes发展可能有以下趋势:

(1)当工艺进一步走向高端,工艺加持下后续的架构就是TX:DSP+DAC、RX:ADC+DSP,流片成本会进一步增加,因此目前112G Serdes IP的license市场价就高达数百万美金。如这些高端工艺下的能效也得到市场印证,那么资本实力雄厚的公司则会获得更好的市场机会和发展。

(2)国内公司由于可能在设计技术和流片上面临限制,较好的发展路线包括以下两种:(i)利用成熟工艺,走低功耗路线;(ii)琢磨新架构,找到下游客户按照需求打磨产品,走不依赖于工艺提升速度的道路。

03

高速Serdes IP厂商

海外

海外公司包括Synopsys、Cadence、Alphawave、Credo等。

其中值得一提的是,Alphawave 是由一群Serdes专家团队于2017年创建,其深耕Serdes相关IP细分领域,并战略布局Chiplet方向。公司于2021年在伦敦交易所上市,并已开发出基于DSP的PAM-4 112G Serdes IP;公司在2022年创造了1.75亿美金收入,同比增长94%。

国内

国内独立Serdes IP公司现在竞争格局还未稳定,初创企业不断涌现,由于数据中心应用的Serdes IP相关技术规模不大,多数IP公司也会拓宽DDR、USB、MIPI等接口IP产品线。

其中,布局高速Serdes相关IP的独立厂商情况有晟联科eTopus、芯潮流Wisewave、集益威(钫铖)Joywell、芯原股份Verisilicon、合见工软Univista、芯耀辉Akrostar等。其中:

晟联科为硅谷华人团队背景回国,自研112G Serdes / PCIe 6.0 PHY 相关IP已回片并power on

合见工软目前已推出56G/112G Serdes Controller IP

芯潮流为Alphawave在中国的合资公司,以支持 Alphawave 高速Serdes IP在中国的销售和定制业务

集益微为华人团队,目前56G Serdes IP已在国内量产,112G Serdes IP也已流片

国内厂商产品的稳定性以及品类和国际领先厂商相比仍存在一定差距,但国内下游芯片以及EDA厂商正处于蓬勃发展阶段,若能激流勇进,抓住导入窗口并与下游客户共同迭代、打磨产品,尚有机会攻克难关、缩短与世界领先 Serdes厂商的设计代差,在国内市场拥有一席之地。

欲了解更多Serdes技术在汽车领域的前沿应用,可扫码报名「第五届中国国际汽车以太网峰会」,与汽车以太网发明人Kirsten Matheus博士零距离互动交流。

参考文章:

1.Synopsys,《借助 IP 满足中国不断演变的云呼叫中心技术需求》白皮书

2.Cadence,《Don’t Mess with Serdes!》

3.Cadence,《224G Serial Links are Next》

4.World of FPGA,《Serdes的好处在哪里(下)》

5.高速射频百花潭,《超详细:Serdes知识详解》

内容来源:

https://mp.weixin.qq.com/s/EvRLLMDlOmOmUXUcokLlnw

- THE END -

精品活动推荐

因文章部分文字及图片涉及到引用,如有侵权,请及时联系17316577586,我们将删除内容以保证您的权益。