台积电资深副总经理张晓强(Kevin Zhang)应邀在ISSCC2024做第一个开场主旨报告《Semiconductor Industry: Present & Future半导体产业:现在和未来》。这也是继2007年张忠谋、2017年侯永清、2021年刘德音之后,第四个在ISSCC做主旨开讲报告的台积电高管,充分说明台积电在业界的受重视程度。

半导体是当今数字经济的基础,正在推动塑造人类历史轨迹的创新。张晓强在报告中重点介绍了半导体行业的最新进展,以支持永远改变我们生活的广泛应用。深入介绍持续先进技术扩展的路径、设计技术协同优化(DTCO)的重要作用,以及系统级集成将如何将系统性能提升到新的高度。半导体的进步将使人工智能(AI)、高性能计算(HPC)、无线连接和自动驾驶领域的许多新创新成为可能。本报告还提供了从低功耗和边缘人工智能设备到基于云计算的技术趋势。通过利用半导体的新功能,这些创新将大大提高生产力、效率、安全性和可持续性。

本文根据现场录音以及张晓强的演讲PPT进行整理,以飨读者。限于水平,如有翻译不到位的地方,敬请谅解。

张晓强开场笑称,希望自己是ISSCC历史上唯一的虚拟大会主席(2021年和2022年由于疫情,ISSCC都是在线上举行。同时鼓励年轻的学生,可以站到大会主旨报告位置,但需要付出努力和白发。

以下为演讲正式内容。

凡是目光所及,从高性能计算(HPC)、人工智能、机器学习到通信,从交通、医疗保健到我们生活中各种消费产品,都与半导体技术发展息息相关。

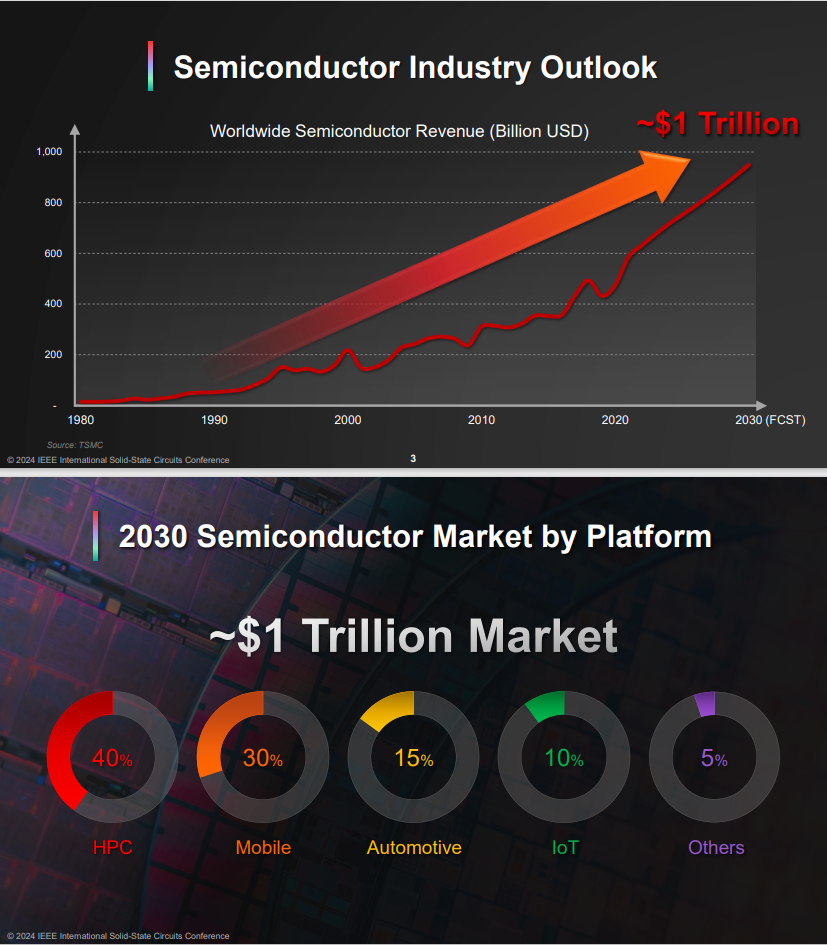

当下全球半导体收入大约在五千亿美元。业界都认为,到了2030年,这个数字将翻一番,达到1万亿美元。但张晓强在这里加上一个限定词:随着人工智能的激增。一万亿美元的数字并不能反映出OpenAI的数万亿美元的半导体计划投资。AMD的CEO苏姿丰(Lisa SU)认为,到2027年,仅人工智能市场就能够达到4000亿美元。

张晓强在演讲中强调,没有人能够确切的知道人工智能将如何塑造这条增长曲线。只有一件事能够确定,我们正在进入半导体的加速增长期。

如果更深入的了解这个潜在的万亿美元市场的高点,高性能计算将占据40%的份额,超过移动设备成为第一大领域。在几年前,如果说到与物联网结合,那是不可想象的。因为传统观点始终认为,边缘设备是用户消费数据的地方,但是到了现在有了AI。

当谈到AI,那不可避免的需要谈到ChatGPT。自从一年半以前ChatGPT推出以来,我们已经看到半导体行业的格局正在发生变化。看图上陡峭的曲线,这背后其实是对算力的永不满足。

2023年2月,英伟达CEO黄仁勋在加州大学伯克利分校哈斯商学院发表演讲,表示ChatGPT只是更伟大事物的开始。他将ChatGPT称为人工智能的“iPhone时刻”,并表示ChatGPT本质上使计算民主化,称这是人工智能和计算行业有史以来最伟大的事情。

张晓强表示,我们可以使用不同的方式描述AI,但确定的是,AI需要大量先进的半导体,这个需求数超越人们的想象。

通信在生活中非常的重要,蜂窝、WI-FI、蓝牙三种通信技术的所有高级标准都需要更高的数据速率,更先进的信号处理,这将继续推动加速采用先进的技术,例如Wi-Fi7。台积电2024年也正在着手生产Wi-Fi7的产品。从一开始,Wi-Fi7的产品就必须采用7nm技术才能够达到功耗性能目标。

在汽车领域,汽车正在经历一场根本性的革命。很多人认为新汽车将是软件定义汽车,但张晓强认为更好的术语是:硅定义汽车(silicon-definedautomotive)。因为所有的软件都必须在硅芯片上运行。无论是传感器、通信、网络,都在推动最先进的半导体技术自主向前发展。

业务创新-首创晶圆代工

在谈技术前,张晓强先谈了半导体行业的业务创新。30多年由张忠谋博首创的纯晶圆代工业务,该创新从根本上改变了半导体行业的格局。通过从传统的IDM模式中剔除非常复杂、成本高昂的晶圆制造,让无晶圆企业能够专注产品开发和创新。“Fabless+Foundry”的模式共同极大的加速了行业的创新。

由于代工厂的引入,出现了很多新玩家。快进到2030年,如上图所见,超过50%的半导体收入由优秀的无晶圆公司、系统公司或云公司贡献。这些都是因为业务创新、代工厂的出现。

先进技术

CFET

晶体管仍然是创新的核心,即硅创新(Silicon Innovation)。自1947年发明后,70多年来,晶体管经历了多次重大的演变。如上图可见,早期的晶体管创新主要集中在围绕几何尺寸减少,但现在情况不再如此。最近一代,一切都集中在晶体管架构的创新以及新材料的使用上。

比如说,16nm从平面晶体管转向FinFET晶体管。今天,台积电在2nm层面即将推出一种全新的晶体管:Nanosheet。将整个通道包裹起来,可以极大的改善设备的漏电,提高传导能力,并且在更低的电压下更好的工作。这对于高性能计算来说非常重要。

图案化技术方面,7纳米EUV的引入为我们铺平了道路,推动几何缩放向前发展。很多人会问:下一步是什么?张晓强表示,下一步需要利用Nanosheet,经过几代人的努力获得最佳值,达到新晶体管的极限。与此同时,台积电也在忙于制造全新的晶体管架构:CFET。本质上,是通过将N-transistor、NMOS和PMOS堆叠在一起,可以将密度大大提高近两倍。

在材料方面,台积电也致力于新材料,例如一种二维材料,通过使用这种新材料,我们可以实现更加节能的目标,远超当今的器件或者晶体管。

进一步了解CFET可以带来的好处,如上图可见,在逻辑门中,就像逆变器一样,你可以在pMOS器件上堆叠nMOS器件,也可以应用在6T SRAM上,可大幅改善零组件电流,使晶体管密度提升1.5~2倍。

张晓强强调这并不是仅仅在PPT上的想法。从上图可以看到,这是台积电实验室制造的真正集成器件,你可以看到晶体管优美的IV曲线。就推动创新而言,这是晶体管架构的一个重要里程碑。

这项技术将硅(Si)和锗(Ge)等不同材料从上下方堆叠,使p型和n型的场效晶体管更靠近。通过这种叠加方式,CFET消除ntop分开的瓶颈,将运作单元活动区域(cellactivearea)面积减少2倍。

DTCO

随着晶体管尺寸的缩小,继续缩小晶体管的几何形状变得越来越困难,成本也越来越高。设计师和工程师必须共同努力才能够实现产品层面效益的最佳缩放。因此,业界将其称为DTCO(设计与工艺协同优化)。

上图展示了一个基于FinFET技术的DTCO。通过使用DTCO技术,减少每个部分的鳍片数量,可以在减小几何尺寸的同时降低功耗。但是当每个器件达到两个鳍片式,设计人员会面临困境。如果你想走得更远,你将要付出更大的努力。

通过DTCO,台积电的设计和工艺团队共同努力,创新的提出了FinFlex的新想法。本质上,允许设计人员混合和匹配单鳍器件、双鳍器件或者双鳍器件和三鳍器件,因此我们可以同时实现最佳的性能、密度和功耗。

另一个很好的例子是SRAM位单元。上图展示了SRAM从130nm一直到今天的3nm,采用更先进的设计技术,实现了超过100倍的密度提升,这实际上是流程创新和协作结合的成果。设计和工艺团队,无法划定各自的工作量,但大家应该是同样重要。

说到SRAM,就不得不谈到最低工作电压,或者说Vmin。在过去很长时间,为了降低电压,必须采用更大的存储单元。通过应用创新的设计技术,可以实现超过300毫伏的Vmin改善,这对于低功耗运行非常重要。

张晓强特别强调,技术扩展的本质是为了节能计算。整个半导体行业走了很长一段路。上图展示台积电十年多的提升,从N28到N3,实现了超过80倍的能源效率。今天人工智能的出现,现场的所有人都应该感到自豪。

HPC和AI

今天的人工智能加速器,无论是GPU还是TPU或者是定制的ASIC,所有这些本质上具有特定的集成方案。基本上现在使用都是CowoS技术带来的先进芯片。如今主要是5nm技术和HBM在一起,张晓强认为这还远远不够。

展望未来,这个平台需要大幅提升,以满足高性能计算的需求。因此,这种配置的核心实际上是更高密度、更低能耗的计算。因此需要多个最先进的芯片垂直堆叠在一起,以提供所需的计算密度。并且还需要大量的内存带宽,因此硅中介层和CoWoS必须进一步扩展。这仍然不够。电力传输是一个问题,因此需要集成稳压器才能解决电力输送的挑战。I/O和带宽互联密度也是一个问题,因此需要将硅光子学引入封装中,这就是未来的发展方向。例如,光芯和电芯片的封装就是一个挑战。

3D堆叠

上图展示了互连密度。我们进行堆叠的原因是为了实现芯片到芯片之间的高密度互连,或者说是芯片与芯片间的通信。图中的曲线顶部是SoC,本质上是上种单芯片互连。底部曲线是常规封装能够达到的密度。中间部分是CoWoS封装,通常称作2.5D封装。

3D堆叠可以称之为SoC解决方案,通过Chip To Chip连结,透过3D堆叠可以使接合的Pitch一路缩小到几微米,实现单晶(Monolithic)的互连密度。所以3D堆叠才是未来。

硅光子/共封装光学(CPO)

张晓强博士谈到硅光电子技术在未来高性能计算中的重要作用。他强调了电子在计算方面的高效性,而光子则在信号传输或通信方面展现出更佳的性能。通过50Tb的交换机芯片举例来说明,如果全部采用电子技术,系统消耗高达2,400W的功率,系统面临功耗和效率的巨大挑战。目前解决方案是采用插拔式模组(Pluggable),可省下40%功耗(约1000W)。这远远不够,随着未来需要更高速信号、更高频宽,需要在封装中将电子更早的转化为光子,技术把光子能力带进来,因此使用共封装光学的先进封装技术来正确实现光子功能。

因此,结合先进的堆叠技术,将硅基光电子技术与电子芯片技术结合起来,是未来发展的关键方向。通过这种结合,可以显着降低功耗(减少至50%)并提高效率,达到5pJ/bit的能耗,展示了硅基光电子技术在未来半导体技术中的潜力和重要性。

张晓强指出,为了解决高性能计算平台中的功率传递问题和IO以及带宽互连密度的挑战,需要将硅基光电子技术引入封装中。这不仅能够提高数据处理和传输的效率,还能够通过在封装中集成电压调节器和利用硅基光电子技术来解决电力传递和互连密度的问题,从而为高性能计算设备提供更高的能效和性能。

张晓强博士的讨论突出了硅基光电子技术在推动未来半导体行业发展,尤其是在高性能计算领域中的重要作用。他的见解预示了硅基光电子技术是未来技术发展的一个关键方向,对于解决当前电子技术面临的一些基本限制提供了新的思路。

如今,使用最先进的晶体管技术,我们可以将大约1000亿个晶体管封装在同一个芯片中,但这还不足以解决未来的AI机器学习应用。必须利用先进的3D封装技术,才能够将晶体管的数量真正增加到一万亿个,以满足计算需求。

RF

谈到蜂窝射频方面,他提到,当从4G向5G过渡时,为了将数据速率提高十倍,需要结合更多的数字电路,比如先进的ADC、先进的信号处理能力。在这样做时,射频设计、射频收发器设计都可从28nm发展到16nm中收益。

如果展望未来,比如6G,就需要覆盖更广泛的频率范围,与FR3一样需要提高数据速率。这就需要更先进的半导体,因此未来收发器的设计,如果使用7nm、5nm不必感到太过惊讶。

汽车

谈到汽车方面,从根本上看,最新的汽车技术需要大量运算能力,为你的汽车提供动力和自动驾驶。张克强称之为“闭上眼睛,放松心灵”。

张克强认为,智能汽车目前存在相当的功耗问题。车用半导体技术在导入上一直落后消费性或HPC几个世代,是因为非常需要严格的安全性要求,汽车应用的DPPM(缺陷率)必须接近零,也因此晶圆厂、半导体制造和汽车设计人员必须更密切地合作,以加快这个速度。

台积电正在预先应用自动设计规则降低缺陷密度,张克强表示,在不久之后,你们会看到3nm导入汽车。

谈到MCU方面,MCU在汽车转型为区域架构后变更重要,也需要先进半导体技术给MCU提供运算能力。传统MCU大都采用浮动闸极(floatinggate)为基础的技术,但浮动闸极技术在28nm以下就卡关,所幸业界已经投资新内存技术,包括新的非挥发性存储器如磁性随机存取存储器(MRAM)或电阻式存储器(RRAM)。

也因此,从MCU转移到MRAM、RRAM为基础的技术,有助于推动技术持续微缩,从28nm缩小到16nm、甚至是7nm。

传感器和显示技术

逻辑技术是数字化转型的中心,但我们生活的世界是模拟的,物理世界是模拟的。因此传感器和显示技术在连接现实世界与物理世界方面发挥着至关作用,数码相机和智能手机实际 从根本上我们记录与交流的生活方式。

传感器技术已经取得了长足的发展,从最简单的2D设计、单层设计,到现在3D晶圆堆叠的智能系统,基本上将信号处理层叠在传感层上。张克强也表示,我们技术已经开始投资研究多层设计的技术。

进行三层或多层设计能追求画素最佳化,通过分层设计或移动,可以继续推动画素尺寸缩小同时兼顾解析度需求,也能同时达到最佳传感能力;另一个例子是AR、VR,透过将不同层的存储器分开,再堆叠到其他逻辑芯片,可有效缩小尺寸,同时维持高效能需求。

结语

谈到2023年的万亿美元市场,如果要衡量这个万亿美元市场的影响,必须考虑乘数效应。万亿美元半导体市场带到了高达3万亿美元的电子产业市场。产生了12万亿美元的信息产业市场,创造了超过145万亿美元GDP。因此半导体的经济影响是巨大的。

张克强最后分享了一个有关自己的轶事。他表示7年前离开当时最大的半导体公司,去了中国台湾。当时他认为半导体领域的黄金时代已经过去了,去亚洲是要迎接职涯的日落时刻,但时间快进7年后,张克强表示,我没看到日落,看到的是更加灿烂明亮的日出。随着AI出现,半导体将驱动许多新应用,触及人类生活每一个面向,并改变人类历史的轨迹,现在是半导体的全新时刻,半导体最美好好的日子还在前头,让我们一起努力实现这一目标。