今日光电

有人说,20世纪是电的世纪,21世纪是光的世纪;知光解电,再小的个体都可以被赋能。追光逐电,光赢未来...欢迎来到今日光电!

----追光逐电 光赢未来----

基于两步刻蚀工艺的锥形TSV制备方法

田苗,刘民,林子涵,付学成,程秀兰,吴林晟

(上海交通大学 a.电子信息与电气工程学院先进电子材料与器件平台;b.射频异质异构集成全国重点实验室)

以硅通孔(TSV)为核心的 2.5D/3D 封装技术可以实现芯片之间的高速、低功耗和高带宽的信号传输。常见的垂直 TSV 的制造工艺复杂,容易造成填充缺陷。锥形 TSV 的侧壁倾斜,开口较大,有利于膜层沉积和铜电镀填充,可降低工艺难度和提高填充质量。在相对易于实现的刻蚀条件下制备了锥形 TSV,并通过增加第二步刻蚀来改善锥形 TSV 形貌。成功制备了直径为 10~40 μm、孔口为喇叭形的锥形 TSV。通过溅射膜层和铜电镀填充,成功实现了直径为 15 μm、深度为 60 μm 的锥形 TSV 的连续膜层沉积和完全填充,验证了两步刻蚀工艺的可行性和锥形 TSV 在提高膜层质量和填充效果方面的优势。为未来高密度封装领域提供了一种新的 TSV 制备工艺,在降低成本的同时提高了 2.5D/3D 封装技术的性能。微电子技术的飞速发展促进了现代集成电路在高性能、低成本和低功耗方面的突破。然而,微电子封装技术的发展相对滞后,逐渐成为制约半导体技术进一步提升的主要瓶颈。以硅通孔(TSV)为核心的2.5D/3D 封装技术是一种新型的高密度封装技术,通过在硅基底上形成垂直方向的通孔,并用金属材料填充,实现了芯片之间的立体互联,被认为是未来高密度封装领域的主导技术。TSV 封装技术具有显著的优势,如缩减了芯片尺寸、提高了集成度、降低了信号传输延时和功耗、提升了数据传输速率和带宽等。常规的 TSV 是采用基于等离子刻蚀、循环交替刻蚀/钝化过程的博世(BOSCH)工艺来刻蚀制备的,所得通孔侧边垂直度接近 90°。该垂直圆柱形通孔有利于提升通孔的数量和密度。但是 BOSCH 工艺的循环刻蚀过程会造成侧壁呈扇贝状,导致后续沉积的膜层厚度不均匀。此外,垂直侧壁也增加了后续电介质绝缘层、阻挡层和铜种子层的沉积难度,难以实现良好的阶梯覆盖。膜层沉积时往往只能在 TSV 开口处形成较厚的膜层,而在 TSV 较深处的侧壁和底部很难进行沉积。这种厚度差异会影响 TSV 的电镀填充效果,导致孔口过度填充,孔底出现空缺 [1] 。同时,由于电镀液中的 Cu 2+ 在 TSV 开口处补充的速率远高于 TSV孔深处补充的速率,从而加剧了孔口和孔底部的沉积速率的不一致,进一步导致了填充缺陷的产生。为了解决这些问题,可以采用锥形TSV的结构。锥形TSV消除了侧壁上的扇贝状结构,并且具有倾斜的侧壁,可以显著提高绝缘层、阻挡层和铜种子层的均匀性和阶梯覆盖性能 [2] 。电镀过程中,其较大的开口也有利于电镀液中的Cu 2+ 在孔深处的快速补充,从而提高孔内部的电镀填充效率。因此,通过同时改善膜层质量和离子通道,锥形TSV可以改进TSV的填充效果和性能。研究表明,锥形TSV还具有可靠性和传输性能方面的优势。对不同几何形状TSV(包括纺锤形、锥形、椭圆形、三角形、四角形和圆柱形)的可靠性影响的研究表明,与其他TSV形状相比,锥形TSV能更有效地均匀释放垂直方向的热应力。这意味着TSV底部的应力集中程度较低,从而降低了晶圆之间外部接触区域发生故障的可能性,提高了TSV封装的机械可靠性 [3] 。另外,对圆柱形和具有不同锥形角度的锥形TSV的功率损耗进行比较研究,发现锥形TSV由于表面积和寄生参数较小,具有更好的功率性能,能够降低功率反射损耗,提高功率传输效率 [4] 。目前有两种方法可以制备锥形TSV,一种是改良的BOSCH工艺,一种是SF 6 /O 2 低温反应离子刻蚀(RIE)法。改良的 BOSCH 工艺是在传统的 BOSCH 工艺的基础上,通过调整脉冲时间,增加刻蚀脉冲时间,减少钝化时间,从而形成锥形 TSV [5] 。然而,这种方法只能获得有限的锥形角度(85°~90°),不能满足大多数应用的需求。为了改善锥形 TSV 的开口度,有些研究在 BOSCH 工艺后再进行一次各向异性刻蚀,使孔口呈喇叭状 [6-7] 。该工艺改善了孔口位置的膜层连续性,但对孔底,尤其是孔底拐角处的膜层改善还有待提高。另一种方法是 SF 6 /O 2 低温 RIE 法,此方法中 SF 6 分解得到的 F*自由基各向同性地刻蚀硅,O 2 的加入将F自由基与Si发生反应生成物SiF x 氧化成SiO x F y ,SiO x F y 附着在刻蚀槽的侧壁上,在侧壁上形成保护层,从而增加刻蚀的方向性 [8] 。低温可以增加对氧化硅掩膜的刻蚀选择比,降低反应产物 SiF 4 的挥发性,从而增强钝化效果,增加各向异性 [9] 。SF 6 /O 2 低温 RIE 法可以实现小于 85°且可控的倾斜角并得到较大的深宽比,扩大了 TSV 工艺整合的可能性 [10] 。但是,SF 6 /O 2 低温 RIE 法也存在一些缺点,如在掩膜与晶圆交界处容易形成侧掏尖角,导致在该处沉积的介质和金属薄膜断裂,增加了 TSV 通孔填充的难度和漏电的风险[11] 。另外,低温 RIE 通常要求极低的温度(-40~ -100 ℃),使得大部分刻蚀机难以实现 [10] 。因此,改良的 BOSCH 工艺和低温 RIE 法都有一定的局限性,不能适应大多数应用场景。为了解决这个问题,本文提出了一种在非低温条件下制备锥形 TSV 的两步刻蚀法,并研究了如何控制和改善锥形角度和锥形 TSV 形貌。同时,通过研究锥形 TSV 中的膜层厚度和电镀填充深度验证了所得到的锥形 TSV 在膜层沉积和电镀填充过程中的优势。锥形 TSV 的等离子体各向异性刻蚀是在 F * 自由基刻蚀和氧气钝化之间找到一个平衡,使得侧壁有节制地被刻蚀,且其刻蚀速率明显小于孔底的刻蚀速率。锥形深孔的刻蚀是在 SPTS 反应离子刻蚀机中进行的。在这个刻蚀过程中,温度、电感耦合等离子体(ICP)功率、腔室压力、射频(RF)偏压、气体体积流量、SF 6 与 O 2 的体积流速比均会影响刻蚀结果,如刻蚀速率、选择性、通孔轮廓、侧壁倾斜程度、侧掏。ICP 功率和 RF 偏压是影响刻蚀速率的主要因素。ICP 功率越高,等离子体的密度越大,离子通量越大,刻蚀速率越高。RF 偏压越高,轰击晶圆的离子能量越大,刻蚀速率和陡直度越高。腔室压力会影响反应离子的平均自由程,进而影响到各向异性。腔室压力的减小会产生较高的各向异性,增加刻蚀垂直度。而腔室压力增加,离子浓度增加,反应离子的平均自由程减小,离子偏转严重,会导致侧掏现象。侧掏会在掩膜下方形成侧掏尖角(或下切),形成如图 1(a)所示的孔形。

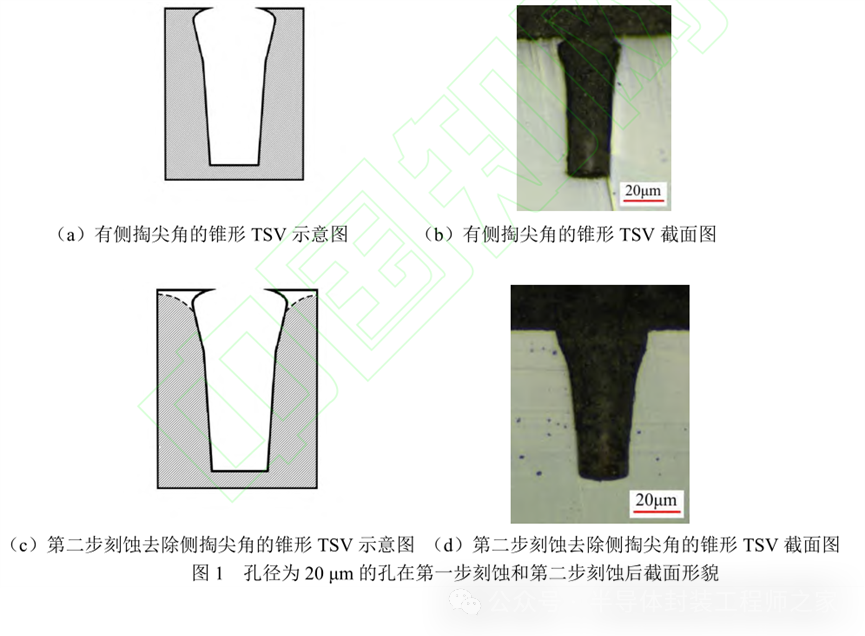

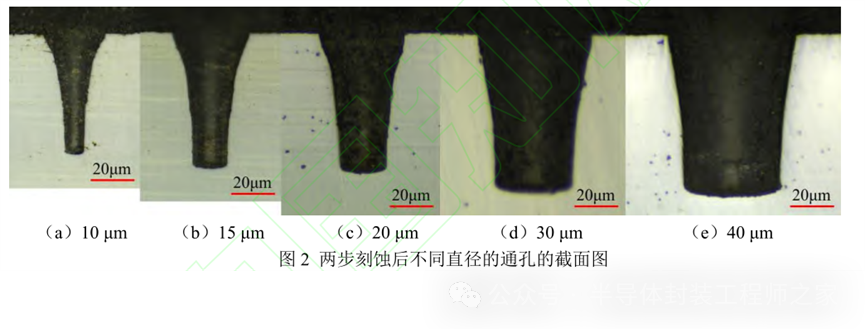

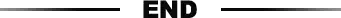

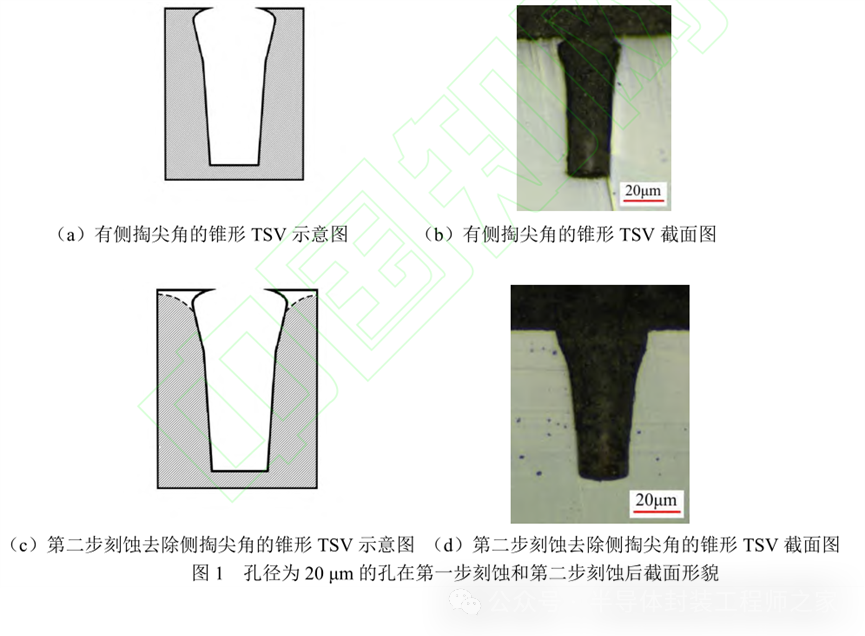

F 与 O 原子数比是影响侧壁倾斜度(即锥形角度)的主要因素 [12] 。这是由于 F 原子和 O 原子在表面的竞争吸附,O 原子的吸附导致钝化,而 F 原子的吸附导致硅刻蚀。F 与 O 原子数比增加,表面吸附的 O原子的侧壁钝化跟不上 F 原子的吸附导致的刻蚀,从而导致负锥度,孔形下大上小,同时侧掏现象严重。当 F 与 O 原子数比减小,O 原子的竞争吸附减少了 F 原子的吸附刻蚀,钝化效果增强,形成正锥形深孔。温度对各向异性和侧掏均有影响。温度降低,可降低反应产物 SiF 4 的挥发性,生成钝化层,增强钝化效果。在孔底,由于等离子体产生的离子轰击使钝化层脱离,进行所谓的溅射刻蚀。而侧壁由于受到较少的离子轰击,其上的钝化层得到部分保留。这样,温度降低,各向异性提高,侧掏减少。研究表明,将基底温度设置为约 -100 ℃,可以将各向异性刻蚀减至最低程度 [13] 。但是,这样的极低温对于大多数刻蚀机来说是很难实现的。为了找到更易于实现的技术方法,此处将温度控制为 5 ℃。经过调整,第一步刻蚀参数设置为:温度为 5 ℃,腔室压力为 25 mTorr (1 Torr≈133 Pa),ICP 功率为 800 W,射频(RF)功率为 50 W,SF 6 和 O 2 体积流量均为 40 cm 3 /min,刻蚀时间为 20 min。图 1(b)为第一步刻蚀后带有侧掏尖角的锥形 TSV 截面的光学显微镜图。经过 20 min 刻蚀,孔径为 20 μm的孔深度达到了 67 μm。侧壁的倾斜角度,即锥形 TSV 的锥形角度为 86°。虽然第一步刻蚀形成了锥形,孔内直径最大处达到了 30 μm,但是由于侧掏尖角的存在,开口处孔径依然较小,为 23 μm。为了消除侧掏尖角,改善孔的形状,在去除掩膜层后进行第二步各向同性刻蚀。刻蚀参数设置为:温度为25 ℃,腔室压力为35 mTorr,ICP功率为800 W,SF 6 、Ar和C 4 F 8 体积流量分别为80、40和10 cm 3 /min,刻蚀时间为 2 min。第二步刻蚀中只使用了有刻蚀作用的 SF 6 ,而不用有钝化作用的 O 2 。同时,Ar 和 C 4 F 8的加入可以降低刻蚀速度,避免由于刻蚀速率过快导致的表面粗糙。图 1(c)为第二步各向同性刻蚀去除侧掏尖角的示意图。图 1 (d)为经过 2 min 各向同性刻蚀后所得到的 TSV 截面的光学显微镜图。明显可以看到侧掏尖角已被去除。同时,孔底直径几乎没有变化,但是孔上部扩大,锥形角度增加,形成喇叭状。这一形貌更有利于膜层的连续沉积和无孔隙的电镀填充。图 2 为经过相同刻蚀过程(20 min 的第一步刻蚀和 2 min 的第二步刻蚀)后不同设计直径(即掩膜开口孔径)的深孔的截面图。可以明显看到孔深随着孔径的增大而增大,而锥形程度却减小了。

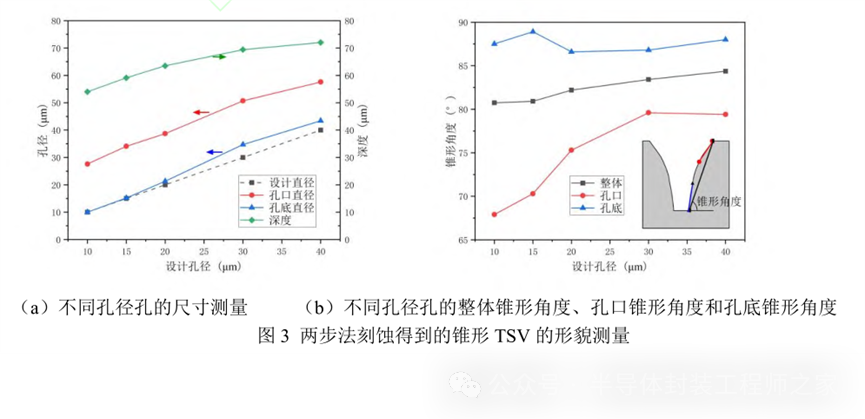

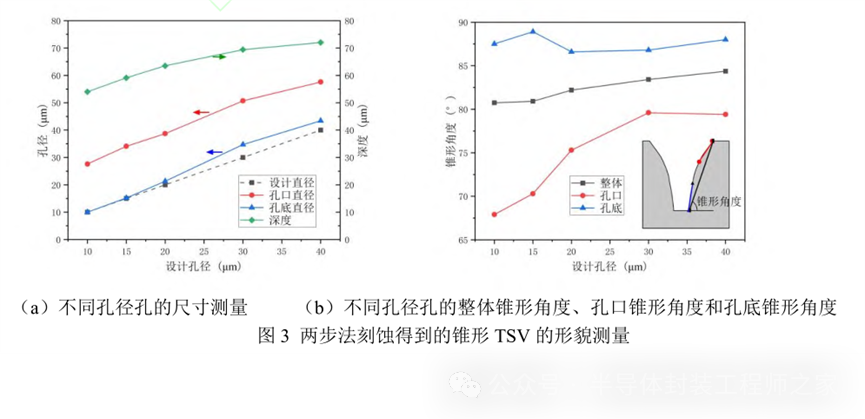

图 3(a)测量了孔深和孔底直径、孔口直径,并与设计直径进行了比较。结果显示,在相同的刻蚀条件下,大孔径的孔深度较大,孔底直径更容易比设计直径偏大。这是因为在相同的刻蚀条件下,刻蚀气体更容易进入大尺寸孔内,因此对于孔底及侧壁的刻蚀会更快。相反,对于小尺寸的孔径,刻蚀气体难以进入,因此刻蚀速率相对较慢。这与深硅刻蚀中与深宽比相关的负载效应(ARDE)相一致。

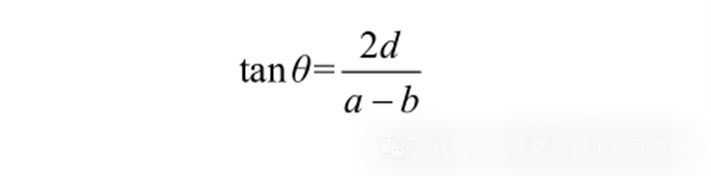

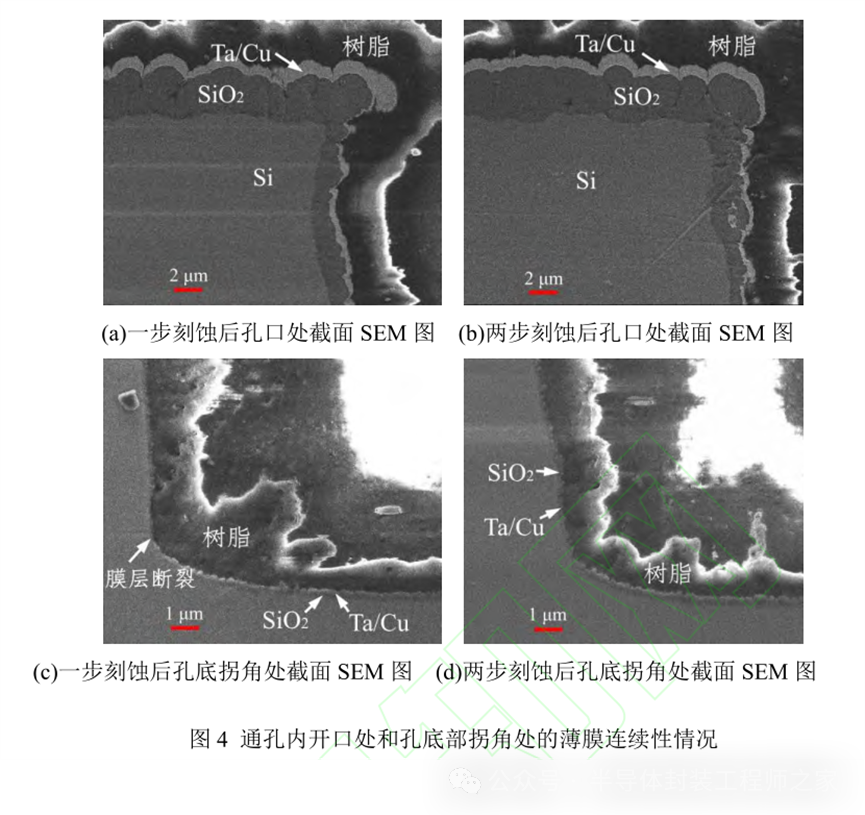

图 3(a)中可以看到,孔口直径均比孔底直径大 14~19 μm,印证了孔的锥形形貌。通过孔口直径(a),孔底直径(b)和孔深(d),计算得到孔壁的锥形角度(θ),即

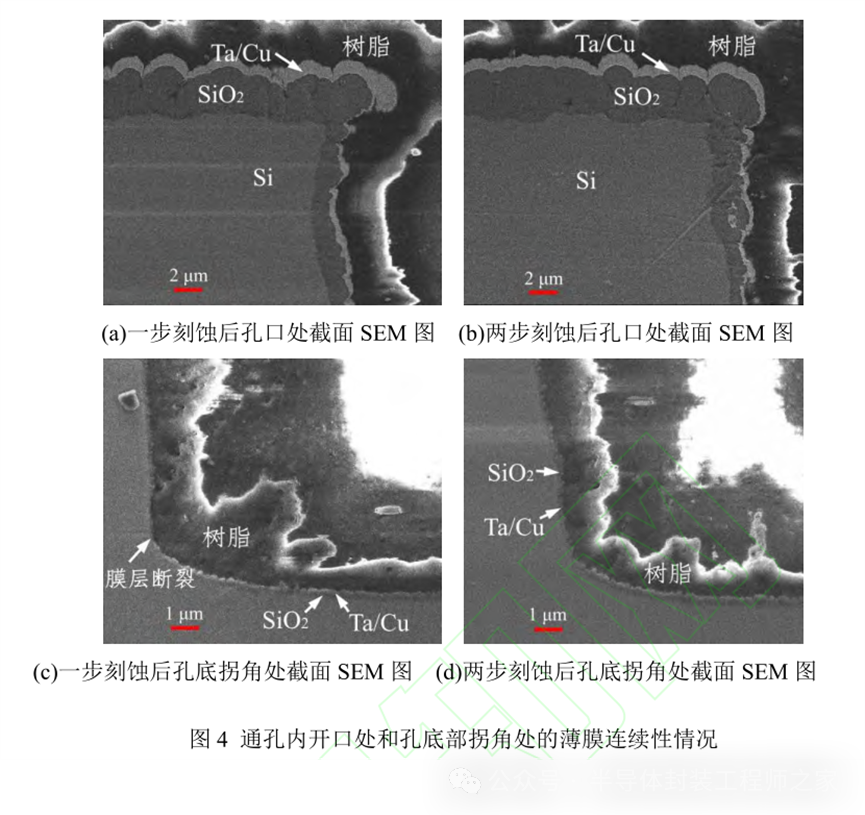

图 3 (b)中黑色的点线为通过孔深、孔口和孔底直径计算得到的锥形角度。但是通过图 2 可以观察到孔侧壁并不是直线,孔上部普遍孔壁更倾斜,锥形角度更小。因此选择测量孔的上 1/3 和下 1/3 分别作为孔口和孔底的锥形角度。图 3 (b)中红色和蓝色线分别画出了孔口和孔底的锥形角度。可以看到,不同孔径的孔底锥形角度比较相似,在 86.6°~88.9°之间。而孔口的锥形角度则比孔底小,在 68°~79°之间,并且在 10~30μm 孔径范围内随着孔径的增大而增大,即倾斜度降低。这说明大孔径的喇叭口倾斜程度更小,而小孔径的喇叭口倾斜程度更大,这一现象也可以在图 2 中直观地看出。这是因为,在相同的第二步各向同性刻蚀工艺下,样品表面部分刻蚀速率是相同的。无论是大孔径图形还是小孔径图形,在孔口处的侧向刻蚀速率是相同的。因此,对于小尺寸的孔径来说,相同时间的刻蚀会导致其孔口直径增加的比例更大,这也就意味着孔口处会更加倾斜。而当孔径继续增大,这一影响逐渐减小,导致孔径 30μm 以上的孔口锥形角度变化不大。刻蚀后的硅深孔内需要依次沉积绝缘层、阻挡层和种子层:绝缘层用来电隔离硅基底和填充的导电材料,通常选用二氧化硅;阻挡层用来防止铜原子穿透二氧化硅绝缘层而导致的封装器件产品性能下降甚至失效,一般使用化学稳定性较高的金属材料及其化合物,如 Ta、Ti、TaN 等;种子层在后续的电镀填充中提供导电,一般使用 Cu。两步刻蚀得到的喇叭状的孔口角度较平滑,有利于膜层在孔口的连续分布。上大下小的锥形 TSV 也使得孔口的遮蔽效应减小,有利于孔底部的膜层沉积。本文使用的绝缘层、阻挡层和种子层分别为 2 μm SiO 2 、50 nm Ta 和 800 nm Cu。在 Oxford 电感耦合等离子体化学气相沉积(PECVD)设备中沉积SiO 2 绝缘层, 沉积条件为:ICP功率为1 000 W,温度为200 ℃,腔室压力 12 mTorr,SiH 4 、Ar 和 N 2 O 体积流量分别为 14、60 和 70 cm 3 /min,沉积时间为 195 min。在 Denton多靶磁控溅射镀膜系统中溅射了阻挡层和种子层。阻挡层 Ta 的溅射条件为:溅射直流功率为 200 W,Ar体积流量为 40 cm 3 /min,时间为 150 s。种子层 Cu 的溅射条件为:溅射直流功率为 200 W,Ar 体积流量为40 cm 3 /min,时间为 1 200 s。图 4 对比了一步刻蚀和两步刻蚀后得到的 20 μm 直径,65 μm 深度孔的孔口处和孔底拐角处(一般为膜层最薄处)的膜层沉积情况。由于扫描电子显微镜(SEM)的成像原理和精度限制,Ta 和 Cu 层无法区分,在图像上表现为一层(Ta/Cu 层)。为了研磨得到可观察的截面,使用树脂填充了孔内空间,树脂在SEM 图中表现为不导电导致的高亮区域。可以在图 4 (a)和图 4 (b)中看到,ICP-化学气相沉积(CVD)沉积 SiO 2 的过程中会在孔口的侧掏尖角位置沉积更多的 SiO 2 ,使尖角更加突出,这会进一步恶化后续种子层的沉积环境。在图 4 (b)中,虽然同样孔口位置绝缘层沉积比较多,但是喇叭状开口可以部分弥补其导致的孔形变化。从图 4 (c)和图 4 (d)种可以看到,孔底拐角处的膜层厚度比孔口小了很多,而有侧掏尖角的图4(c)中膜层已经观察不到连续的膜层。

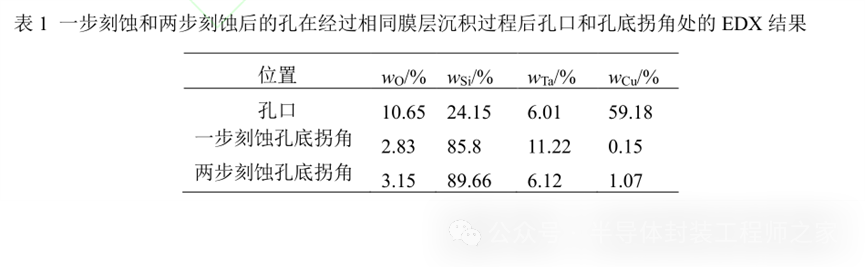

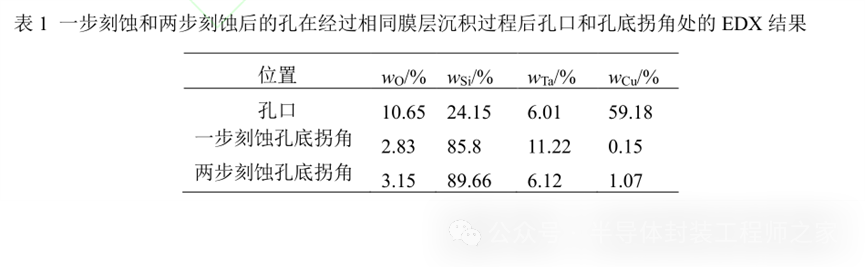

为了进一步确认孔底金属的分布情况,对孔底部拐角处和孔口位置进行了能量色散 X 射线光谱(EDX)分析。表 1 列出了孔口位置和孔底拐角处 O、Si、Ta 和 Cu 的质量分数(w O 、w Si 、w Ta 和 w Cu )。EDX 测试中电子束的穿透深度为 1~2 μm。因此,在孔口,当金属膜层较厚时,EDX 主要收集到金属膜层的信号。在孔底,当金属膜层较薄时,EDX 穿过金属膜层,更多地收集到了绝缘层和基底的材料信息。从表 1 中可以看到,在孔口,金属 Ta 和金属 Cu 的质量分数分别为 6.01%和 59.18%,这说明有充足量的阻挡层和种子层。而在一步刻蚀后的有侧掏尖角的孔底拐角处,金属 Ta 的质量分数为 11.22%。说明阻挡层的沉积受侧掏尖角影响不大,能够覆盖到孔底。而 O 元素和金属 Cu 的质量分数下降到了 2.83%和 0.15%。说明绝缘层和种子层的量不足。第二步刻蚀去除侧掏尖角后,O 元素和 Cu 的质量分数上升至 3.15%和 1.07%。可见,两步刻蚀去除侧掏尖角对孔底绝缘层和种子层的改善有明显作用。

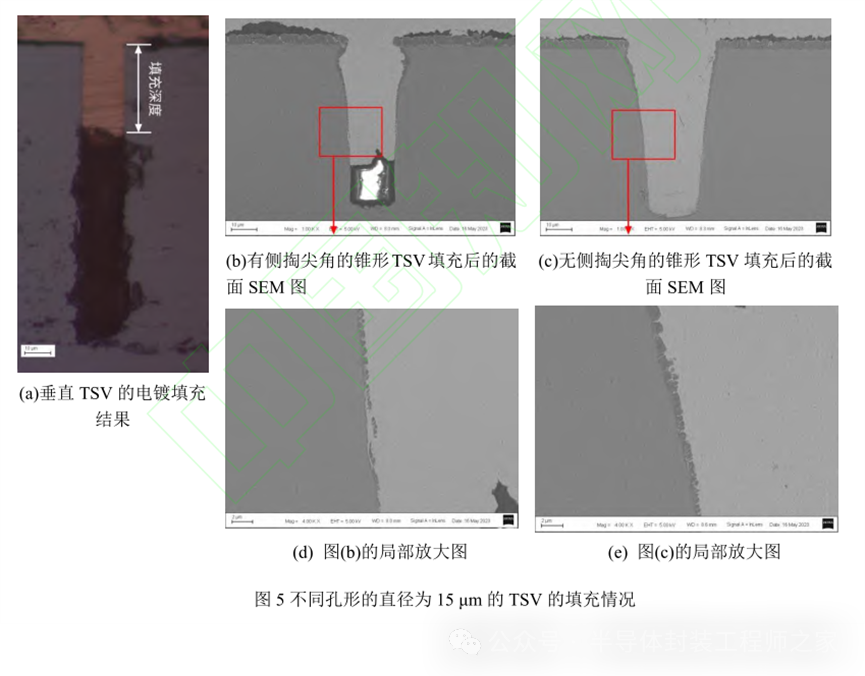

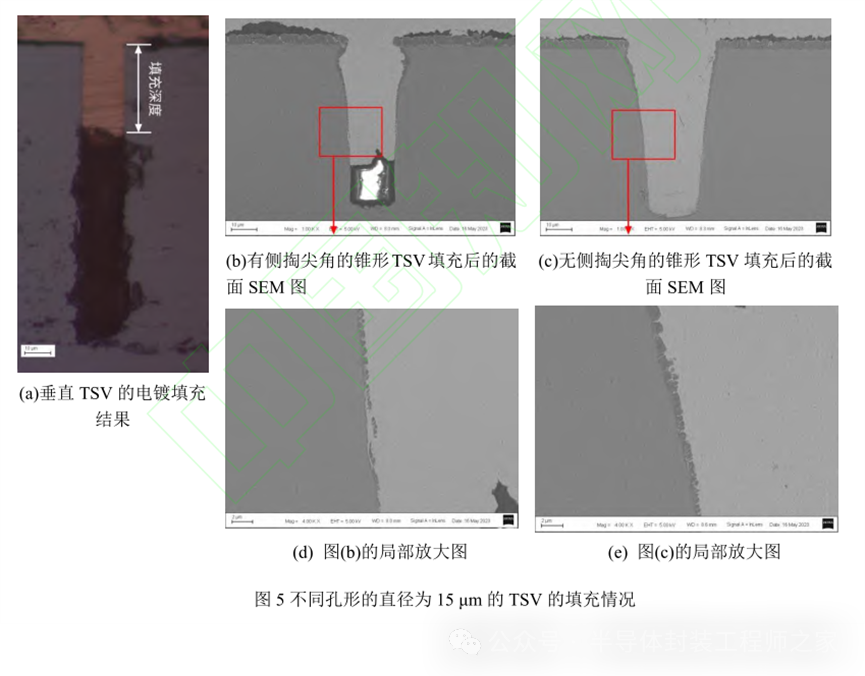

在电镀填充过程中,种子层是金属沉积的起始点,其厚度和连续性对电镀填充的质量具有重要影响。如果种子层过薄或不连续,金属无法在孔底沉积,就会导致孔底缺陷,如空洞、针孔、短路等[14] 。要确定膜层对填充的真实影响,还需要通过电镀填充结果来确定。以高纯铜片作为阳极,带有 TSV 的溅射了种子层的晶圆作为阴极进行电镀填充。电镀液采用新阳SYS2520 甲基磺酸体系电镀液,并加入针对深孔电镀的 UPT3360 系列添加剂。首先,采用 10 mA/cm 2 的电流密度进行预电镀,以在深孔内壁形成一层均匀的铜层。接着,将电流密度提高到 40 mA/cm 2 ,进行正式填充电镀。不同直径的 TSV 需要不同的电镀时间才能达到完全填充。如,10 μm 和 30 μm 直径的 TSV分别需要 6 h 和 10 h 的填充时间。图 5 为直径 15 μm 的孔,在不同的孔形下,经过相同的膜层溅射和电镀填充步骤后的截面图。图 5 (a)为一个通过 BOSCH 工艺刻蚀的直径为 15 μm、深度为 100 μm 的垂直 TSV 的电镀填充效果。填充深度大约为 30 μm。由于种子层未能完全覆盖,孔深处大部分没有得到填充。在图 5 (b)中,一步锥形刻蚀后形成的锥形深孔的填充深度增加到了 40 μm。然而,由于侧掏尖角的存在,孔的填充深度增加有限,因此孔仍然没有完全填满。在图 5 (c)中,第二步各向同性刻蚀将侧掏尖角完全消除,电镀填充深度进一步增加,使得深度为 60 μm 的孔得以完全填充。由此可见,锥形 TSV 的形成和侧掏尖角的消除有助于增加 TSV 的填充深度。这是由于扩大了的孔口提高了种子层在深孔侧壁,尤其是孔底区域的覆盖率,从而改善了电镀过程中孔内的导电情况;另外,较大的孔口也让镀液中的铜离子更容易扩散到孔内并发生还原反应。

图 5 (d)和(e)分别放大了图 5 (b)和 (c)中侧壁上的近似位置。由于阻挡层和种子层已经和填充的铜合为一层,很难观察到阻挡层和种子层的具体情况。但是,在图 5 (d)中可以观察到带有侧掏尖角的深孔中绝缘层出现了断裂。鉴于阻挡层和种子层在绝缘层的上层,可以推断它们也出现了断裂情况。绝缘层的断裂可能导致该区域出现电流泄漏和信号丢失。阻挡层的断裂会导致铜向硅基底的扩散。种子层的断裂会影响填充效果。在断裂位置附近出现了填充空缺与这一推断吻合。在图 5 (e)中侧掏尖角被消除后,绝缘层保持了连续性。虽然不能直接观察到阻挡层和种子层的连续分布,但阻挡层的 EDX 数据和孔的完全填充现象证明了阻挡层和种子层的完全连续覆盖。本文提出了一种用于制备锥形 TSV 的两步刻蚀工艺。该工艺首先采用 RIE 在相对常温下形成锥形TSV,然后进行各向同性刻蚀以消除侧掏尖角并优化锥形轮廓。通过这种工艺,可以在直径 10~40 μm 的孔中实现底部锥形角度约为 87°,顶部锥形角度为 68°~79° 的喇叭状锥形 TSV。本文还验证了锥形侧壁对薄膜连续性和 TSV 填充质量的影响,并在孔径 15 μm,孔深 60 μm 的 TSV 中实现了连续膜层分布和完全填充。证明了锥形 TSV 和侧掏尖角的去除有助于实现完整的薄膜覆盖,从而改善了 TSV 的隔离、阻挡和填充效果。通过两步刻蚀工艺,降低了 TSV 制备的工艺难度和工艺成本,提高了填充质量和工艺稳定性。这将在高密度、高质量封装中有巨大的应用潜力,对半导体产业链和科研领域都具有重要意义。

申明:感谢原创作者的辛勤付出。本号转载的文章均会在文中注明,若遇到版权问题请联系我们处理。

----与智者为伍 为创新赋能----

【说明】欢迎企业和个人洽谈合作,投稿发文。欢迎联系我们诚招运营合伙人 ,对新媒体感兴趣,对光电产业和行业感兴趣。非常有意者通过以下方式联我们!条件待遇面谈联系邮箱:uestcwxd@126.com

QQ:493826566