扫描关注一起学嵌入式,一起学习,一起成长

I2S(Inter—IC Sound)总线, 又称集成电路内置音频总线,是飞利浦公司为数字音频设备之间的音频数据传输而制定的一种总线标准。采用沿独立的导线传输时钟与数据信号的设计,通过分离数据和时钟信号,避免了时差诱发的失真。- 和PCM相比,I2S更适合立体声系统。I2S的变体也支持多通道的时分复用,因此可以支持多声道。

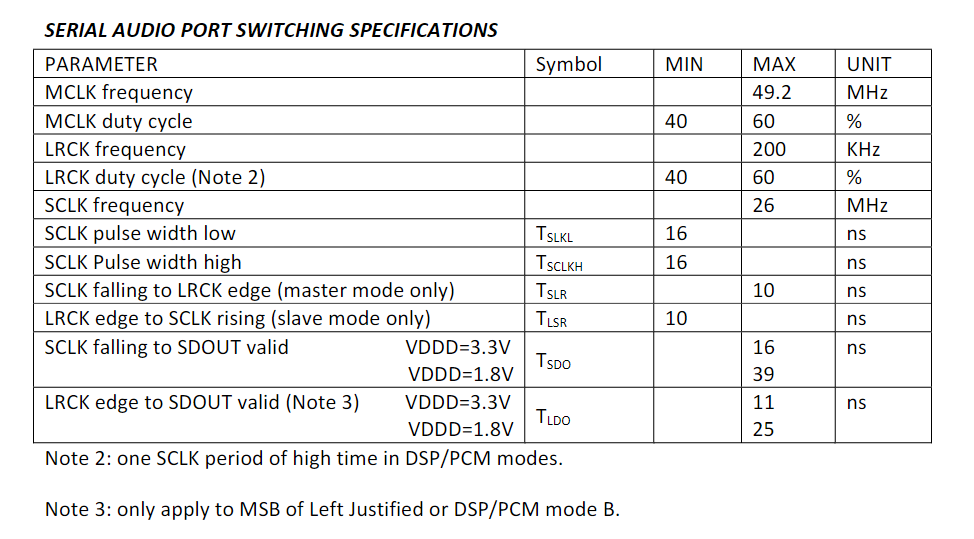

对于系统而言,产生SCK和WS的信号端就是主设备,用MASTER表示。I2S有3个主要信号

- SCLK(BCLK):串行时钟SCLK,也叫位时钟(BCLK),即对应数字音频的每一位数据,SCLK都有1个脉冲。SCLK的频率=2×采样频率×采样位数。

- LRCK:帧时钟LRCK,(也称WS),用于切换左右声道的数据。LRCK为“1”表示正在传输的是右声道的数据,为“0”则表示正在传输的是左声道的数据。LRCK的频率等于采样频率。

- 串行数据SDATA:就是用二进制补码表示的音频数据。最高位拥有固定的位置,而最低位的位置则是依赖于数据的有效位数。

- MCLK:称为主时钟,也叫系统时钟(Sys Clock),一般为了使系统间能够更好地同步时增加MCLK信号,是采样频率的256倍或384倍。

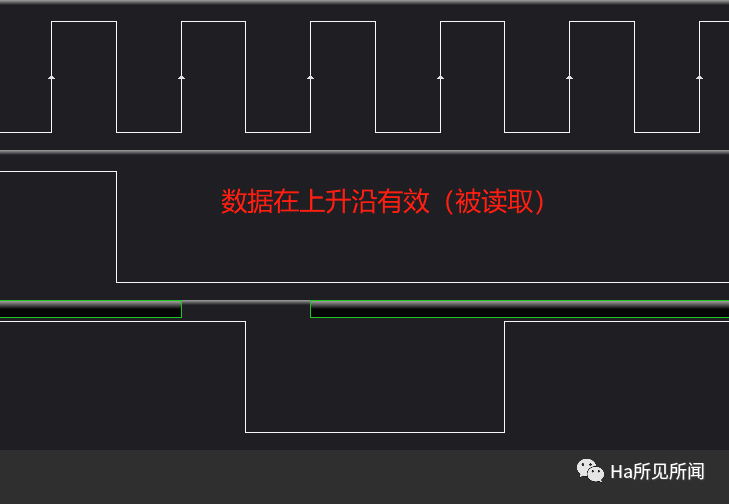

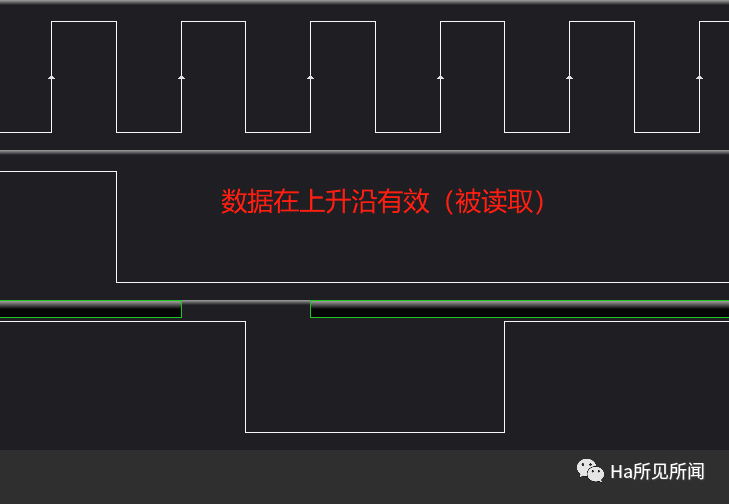

数据在上升沿有效时(被读取),信号只会在CLK为下降沿变化,上升沿时保持稳定状态。

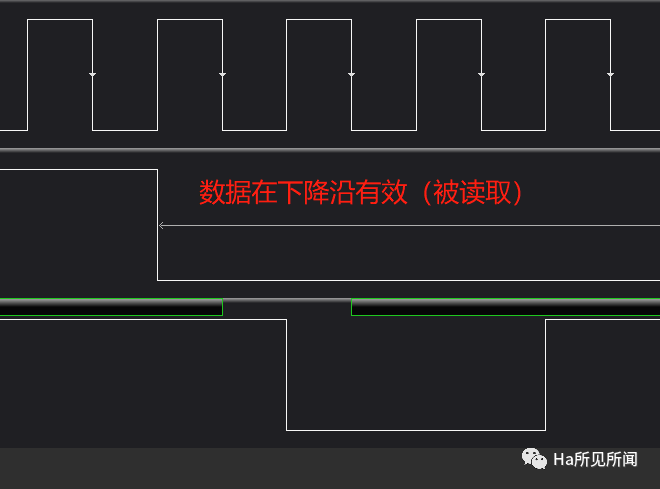

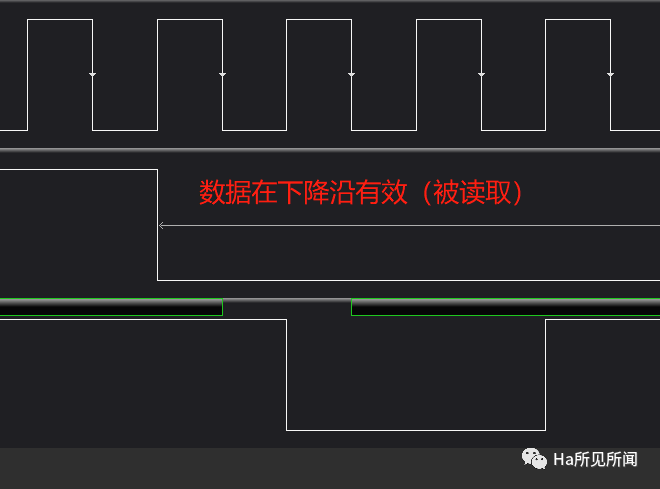

数据在下降沿有效时(被读取),信号只会在CLK为上升沿变化。下降沿时保持稳定状态。

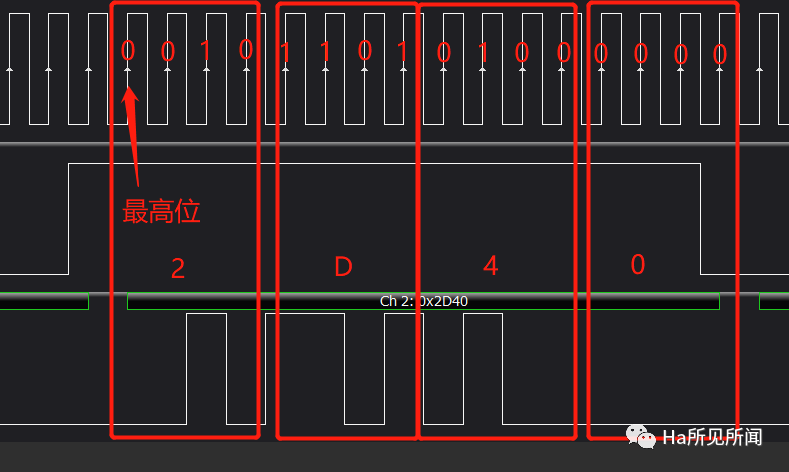

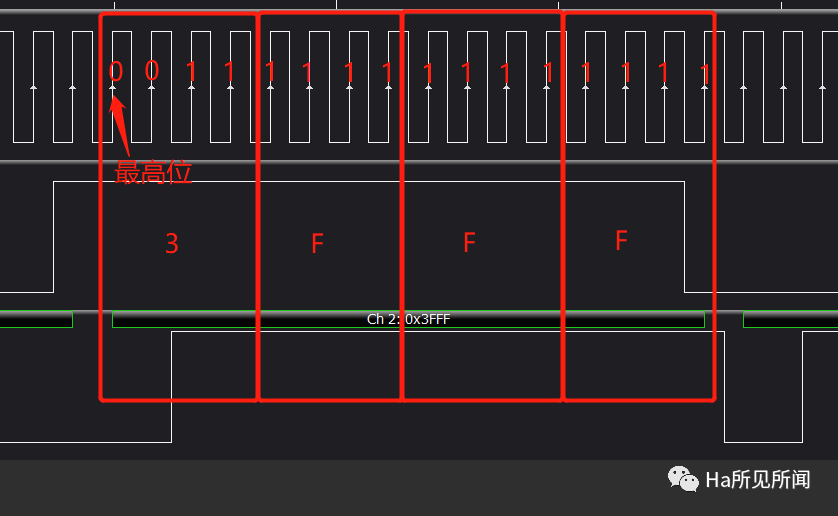

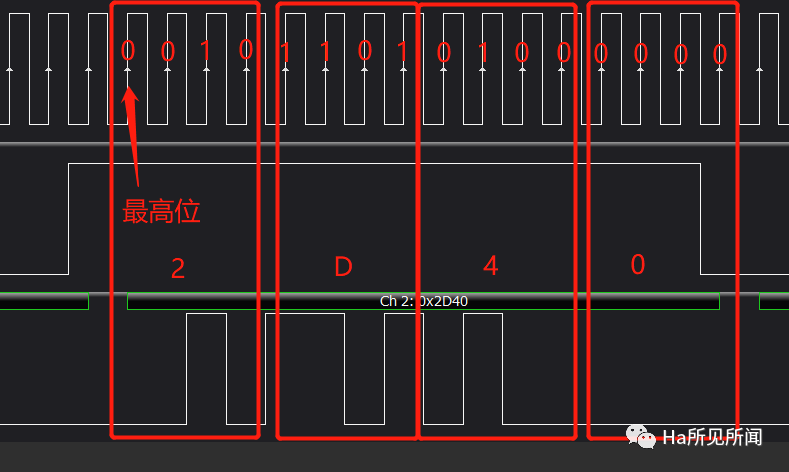

I2S格式的信号无论有多少位有效数据,数据的最高位总是出现在LRCK变化(也就是一帧开始)后的第2个SCLK脉冲处,(第一个脉冲处是上一段有效位数的最低位-此处为我的理解,按波形来看对的上,不知是否有误)。

这就使得接收端与发送端的有效位数可以不同。如果接收端能处理的有效位数少于发送端,可以放弃数据帧中多余的低位数据;如果接收端能处理的有效位数多于发送端,可以自行补足剩余的位(常补足为零)。

这种同步机制使得数字音频设备的互连更加方便,而且不会造成数据错位。

为了保证数字音频信号的正确传输,发送端和接收端应该采用相同的数据格式和长度。

格式

随着技术的发展,在统一的 I2S接口下,出现了多种不同的数据格式。

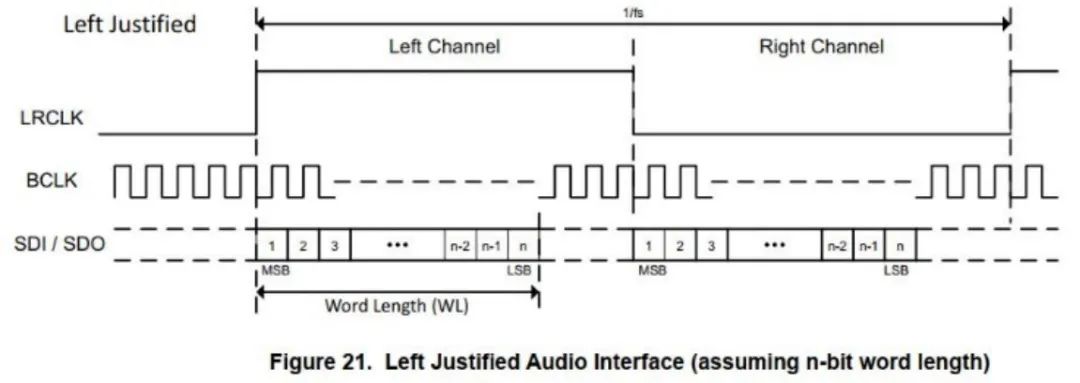

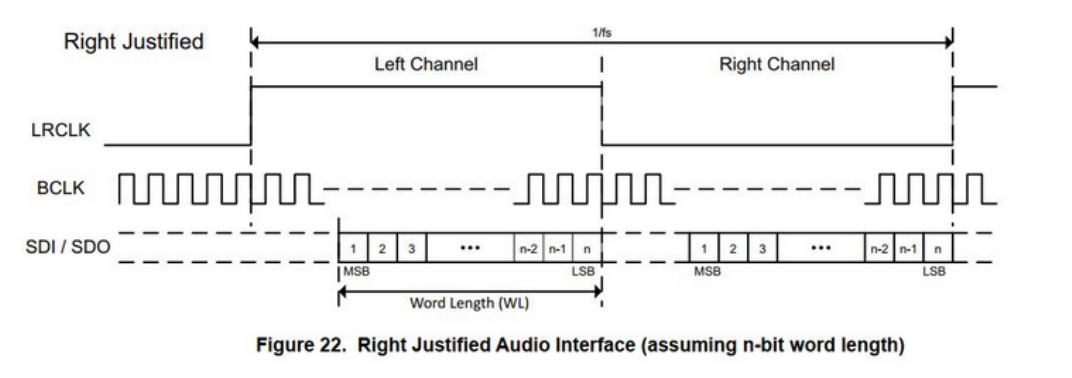

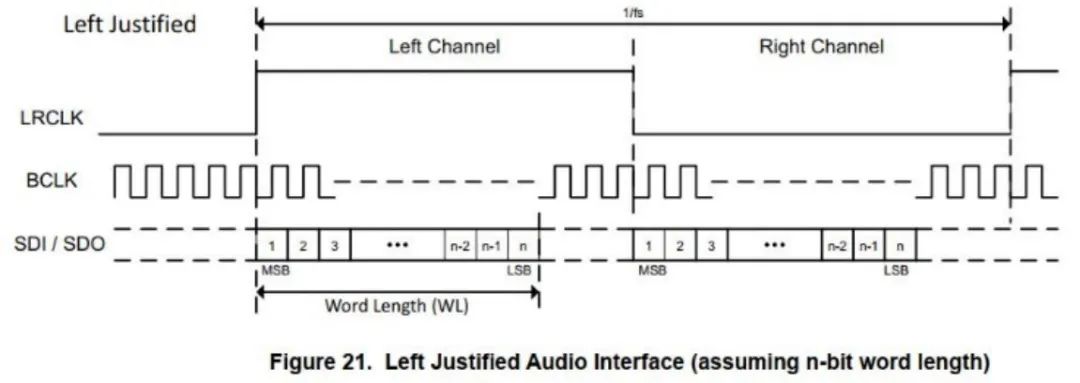

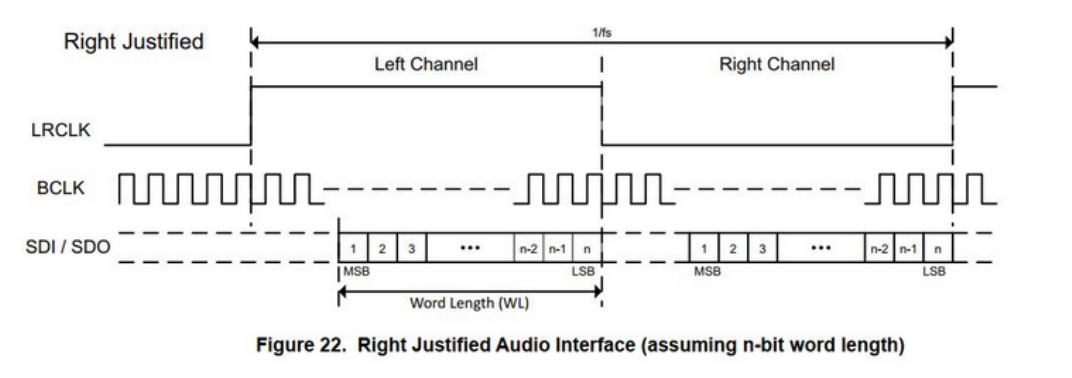

根据SDATA数据相对于LRCK和SCLK的位置不同,分为左对齐-MSB、I2S格式(即飞利浦规定的格式)和右对齐-LSB(也叫日本格式、普通格式)。

对于所有数据格式和通信标准而言,始终会先发送最高有效位(MSB 优先)。发送端和接收端必须使用相同的数据格式,确保发送和接收的数据一致。

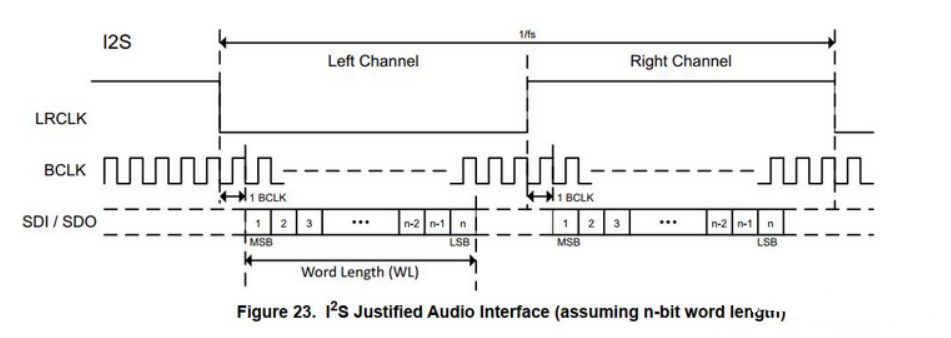

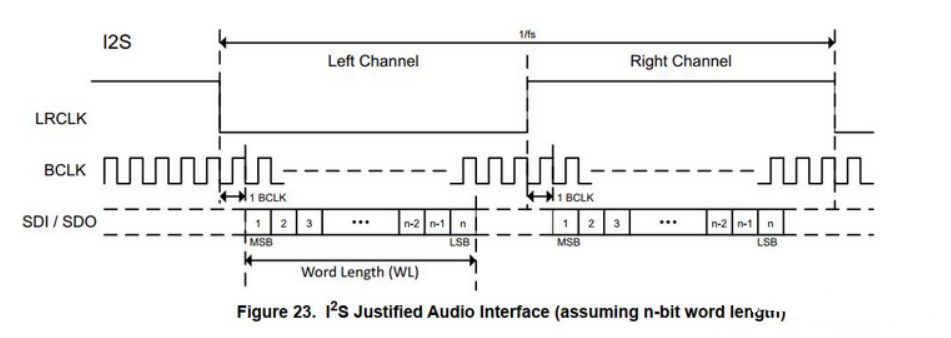

I2S格式

对于这种标准I2S格式的信号,无论有多少位有效数据,数据的最高位总是出现在LRCLK变化(也就是一帧开始)后的第2个BCLK脉冲处。这就使得接收端与发送端的有效位数可以不同。如果接收端能处理的有效位数少于发送端,可以放弃数据帧中多余的低位数据;如果接收端能处理的有效位数多于发送端,可以自行补足剩余的位。这种同步机制使得数字音频设备的互连更加方便,而且不会造成数据错位。

在LRCLK发生翻转的同时开始传输数据。该标准较少使用。注意此时LRCLK为1时,传输的是左声道数据,这刚好与I2S Philips标准相反。左对齐(MSB)标准时序图如下所示:

声音数据LSB传输完成的同时,LRCLK完成第二次翻转(刚好是LSB和LRCLK是右对齐的,所以称为右对齐标准)。注意此时LRCLK为1时,传输的是左声道数据,这刚好与I2S Philips标准相反。右对齐(LSB)标准时序图如下所示:

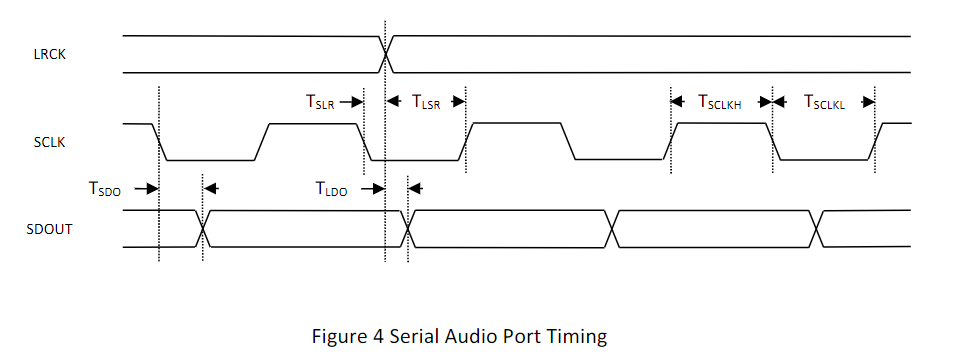

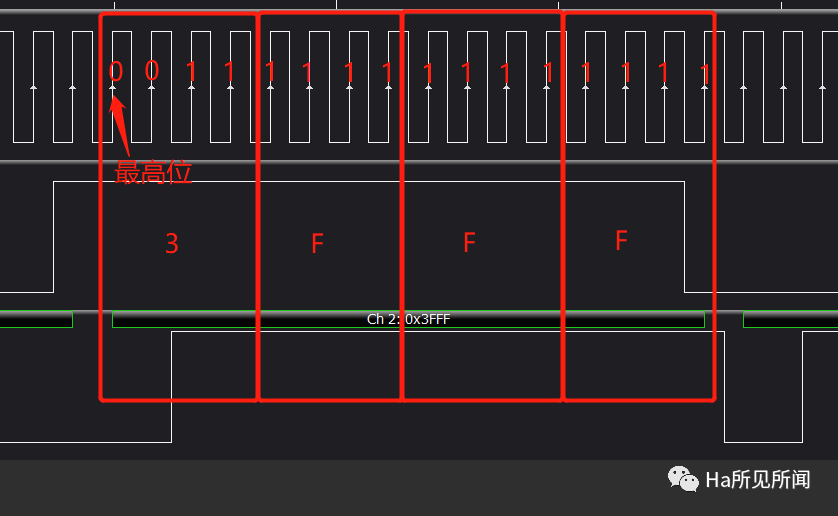

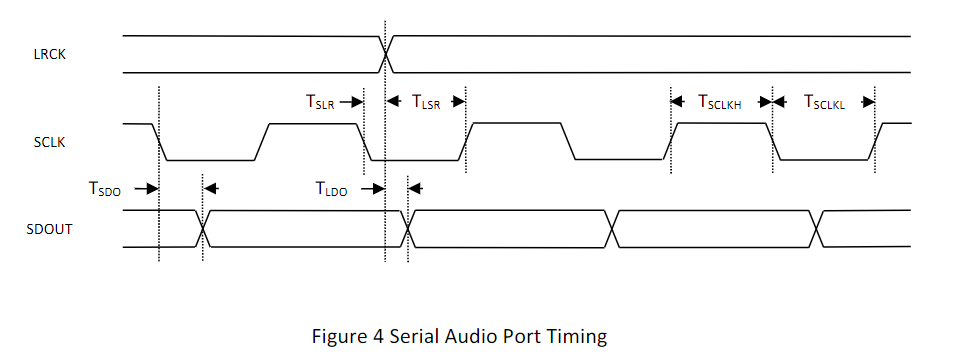

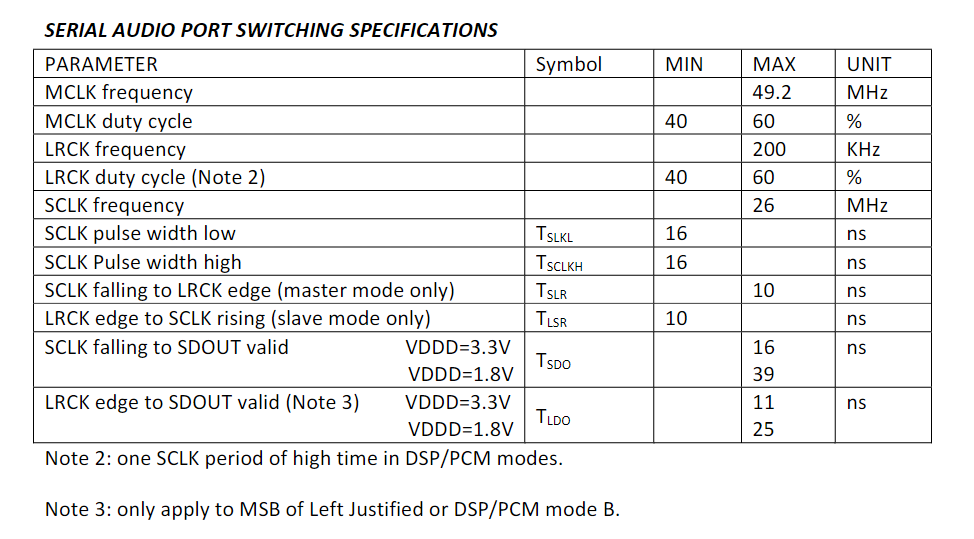

时序

来源:Ha所见所闻

文章来源于网络,版权归原作者所有,如有侵权,请联系删除。

关注【一起学嵌入式】,回复“加群”进技术交流群。

觉得文章不错,点击“分享”、“赞”、“在看” 呗!