第69届国际电子器件大会(IEDM 2023)于2023年12月9号至13号在美国旧金山召开。在本届IEDM上,北京大学集成电路学院共有15篇高水平学术论文(第一作者单位14篇,共同第一作者单位1篇)入选,研究成果覆盖了先进逻辑器件、新型存储器件、感存算融合器件及功率器件等多个领域。按论文第一单位统计,北京大学和IMEC、三星并列本届IEDM大会论文入选数量第一,同时也是录用论文最多的高校。在黄如院士的带领下,北京大学已连续三年成为IEDM录用论文最多的高校,连续十七年在IEDM大会上发表论文。

下面让我们一起探寻北京大学在IEDM的成功源泉!

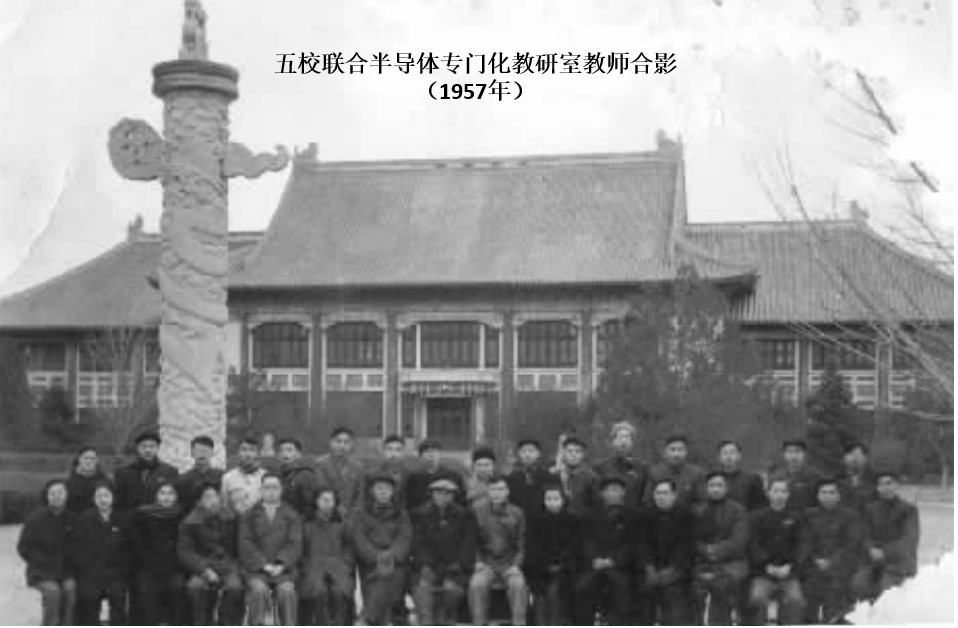

学科建设源远流长,芯火相传

北京大学集成电路学科有着源远流长的学术根基,可以追溯到上世纪50年代由黄昆先生领衔在北京大学创办的“五校联合半导体专门化”,是我国半导体科学技术研究和人才培养的发源地。1956年,周恩来总理主持制定了“十二年科学发展规划”,发展半导体科学技术被列为当时国家新技术四大紧急措施之一。黄昆先生领衔在北京大学创办的“五校联合半导体专门化”,特别强调基础专业知识学习和实践训练,是我国半导体科学技术研究和人才培养的发源地。“五校联合半导体专门化”第一届学生于1958年毕业,恰逢世界第一颗集成电路诞生。

(前排左7为黄昆教授,右7为谢希德教授)

(前排左7为黄昆教授,右7为谢希德教授)

(前排右三为黄昆教授,右四为时任物理系系主任褚圣麟教授,左四为沈克琦教授,二排右2为王阳元院士,三排右5为叶良修教授)

(前排右三为黄昆教授,右四为时任物理系系主任褚圣麟教授,左四为沈克琦教授,二排右2为王阳元院士,三排右5为叶良修教授)

(以上图片来源,北京大学物理学院陈辰嘉教授:忆创办中国第一个五校联合半导体专业)

之后,在王阳元院士和黄如院士的带领下,北京大学于1970年建立了半导体专业,1978年正式建立微电子专业,1985年成立了微电子学研究所,2002年设立了微纳电子学系,2020年设立集成电路科学与工程一级学科,2021年成立了集成电路学院。目前,集成电路学院已建有国家集成电路产教融合创新平台、微纳电子器件与集成技术全国重点实验室、微米纳米加工技术全国重点实验室、微电子器件与电路教育部重点实验室、集成电路高精尖创新中心、集成电路科学与未来技术北京实验室等多个国家、省部级创新研究平台,以及“后摩尔时代微纳电子学科创新引智基地”等国际合作平台,拥有国际一流水平的微纳加工与集成、器件/芯片/微系统设计与测试的前沿研究环境。

北京大学集成电路学院秉承“得人才者得天下,集人心者集大成”的理念,把为国育才、为国创新的使命与担当扛在肩上,致力于集成微纳电子、集成电路设计、设计自动化与计算系统、集成微纳系统、集成电路先进制造技术等五个方向的教学科研工作,进一步深化与集成电路产业多环节龙头企业的合作,建设具有北大特色的“集成电路科学与工程”一级学科,打造国际一流的集成电路人才培养和科技创新高地。

创新培养模式,筑实人才摇篮

进入新世纪,北京大学集成电路学科坚持“产教融合、层次互补、创新拔尖、实践育人”的指导方针,致力于培养堪当民族复兴大任的集成电路领军人才。

2003年,北京大学在全国率先开展了集成电路专业硕士的校企联合培养,与国内龙头制造企业试点校企共建课程、双导师制、企业实践等人才培养新模式,为相关企业累计培养硕士毕业生超300人。2019年,与国内集成电路产业链(制造、设计、EDA、装备)的头部企业合作,共同建设北京大学国家集成电路产教融合创新平台,打造“CMOS制造全流程+集成电路设计”双实践课、企业课等产教融合平台课程体系。积极探索集成电路人才“新工科”的培养模式,培养交叉复合型人才,强化学生综合能力和国际化视野。在“集成电路器件”、“数字集成电路系统设计”、“模拟集成电路设计”等本科生必修课中增加实训环节,培养学生动手实验能力,开设“实践课-暑期课-大师课-企业课”等不同层次产教融合系列课程,实现全方位产教融合,形成实践实训体系,培养学生的对于集成电路产业和前沿工业发展的系统认知。

依托培养模式的创新,一大批优秀人才茁壮成长。北京大学集成电路学科自1980年招收本科生以来,已累计培养学生4000多名,许多毕业生已经成为集成电路领域的佼佼者,多人成为国内外一流高校和头部企业中的中坚力量,为科研创新和产业发展做出了重要贡献,其中2人获IEEE EDS青年成就奖,也是迄今中国内地仅有的获奖者。

坚持原始创新,原创性成果涌现

北京大学集成电路学院面向学科前沿、面向国家重大需求、服务国家重大战略,在集成微纳电子器件领域,不断探索先进集成电路制造技术,发展新原理、新材料与新范式的信息器件,着力于解决集成电路产业“卡脖子”问题。研究内容涉及基础材料、器件理论、制造工艺和系统集成,重点研究原子尺度先进制造工艺、新原理逻辑与存储器件、低维半导体、宽禁带半导体、柔性半导体等新器件及三维集成技术等,取得了一系列具有国际影响力的系统性重大创新成果和技术突破。

在集成电路学科,最受关注的是几大代表性国际学术会议,如集成电路器件领域的IEDM、集成电路设计领域的ISSCC等。IEDM(国际电子器件大会)是集成电路器件领域的顶级会议,在国际半导体技术界享有很高的学术地位和广泛的影响力,被誉为“器件的奥林匹克盛会”。该会议主要报道国际半导体技术方面的最新研究进展,是著名高校、研发机构和产业界领先企业如英特尔、IBM、TSMC等报告其最新研究成果和技术突破的主要平台之一,集成电路领域的许多重大技术突破都是通过该会议正式发布的。

然而,中国大陆二十年前在IEDM鲜有成果报道。在黄如院士的带领下,北京大学从2007年开始突破,至今已连续17年在IEDM上发表了85篇大会论文和6篇特邀论文,其中包括国内首篇CMOS主流器件论文,2010年会议唯一录用的中国大陆论文,在先进逻辑、先进存储、可靠性等方向的国内首篇邀请报告等等,在国际上形成了重大影响力。研究工作引起了包括英特尔、台积电在内的工业界的广泛关注与多次引用,多项成果被连续写入6版国际半导体技术发展路线图。近三年发表在IEDM会议的文章总数(第一作者单位)连续位列全球高校第一,其中2023年入选文章总数并列全球第一,表明北京大学在集成电路器件领域的研究水平持续保持在国际前沿之列。

IEDM 2023会议上,北京大学集成电路学院在先进逻辑器件、新型存储器件、感存算融合器件及功率器件等多个领域发表15篇论文,其中以独立第一作者单位发表14篇,以共同第一作者单位发表1篇。芯思想将为你独家呈现15篇论文的闪光点。

一、先进逻辑器件及可靠性研究

1、首个基于新型隧穿晶体管的极低功耗微控制器芯片

集成电路已进入后摩尔时代,晶体管和电路芯片的功耗问题是制约其未来发展的一大瓶颈,降低功耗、提升性能功耗比正成为国际上后摩尔时代集成电路技术发展的新驱动力。黄芊芊研究员-黄如院士团队致力于从芯片最核心的器件层面解决芯片功耗的瓶颈问题,与东南大学、安徽大学、北方集成电路技术创新中心(北京)有限公司等深度合作,在55nm节点商用逻辑工艺平台上研发了新型超低功耗隧穿场效应晶体管(TFET)与标准CMOS的单片混合集成平台,并基于此平台研制了世界上首个基于隧穿晶体管的极低功耗MCU微控制器芯片。实验制备的新型硅基TFET器件,可以在不影响CMOS器件性能、没有新增新材料的前提下,将传统TFET器件的开态电流提升3个数量级,关态电流比同节点的CMOS器件降低了近2个数量级,实现了业界报道的同类器件最高电流开关比,并可以支持TFET与标准CMOS的混合电路设计。基于该平台研制的TFET-MCU芯片静态电流最小值仅75nA,与相同工艺下的CMOS-MCU芯片相比降低了87.7%,体现了其应用于极低功耗物联网节点的极大潜力。该工作以“A Sub-100nA Ultra-low Leakage MCU Embedding Always-on Domain Hybrid Tunnel FET-CMOS on 300mm Foundry Platform”为题发表。

2、高性能硅基后道兼容单原子层WSe2 p型晶体管器件

二维过渡金属硫族化物(TMDC)半导体材料在原子层薄的体厚度时具有良好的传输特性。化学气相沉积(CVD)广泛应用于大部分TMDC材料的生长,但是高质量的单晶生长一般需要较高的生长温度,无法与硅基后道工艺兼容。针对上述问题,吴燕庆研究员、黄如院士团队采用非原位加热的化学气相沉积法在硅基兼容的超薄SiO2基底上直接生长p型WSe2,成功在低至450 ℃的低温下制备了高质量的单原子层WSe2单晶。采用后退火工艺的方法优化了源漏接触,室温下空穴迁移率为45 cm2/V·s,为同类器件最高水平。基于5 nm SiO2上直接生长的WSe2制备了p型晶体管器件,其开态电流、跨导均为同类器件中最高水平。该工作以“BEOL Compatible High-Performance Monolayer WSe2 pFETs with Record Gm=190 μS/μm and Ion=350 μA/μm by Direct-Growth on SiO2 Substrate at Reduced Temperatures”为题目发表。

3、首次实现堆叠围栅纳米片氧化物半导体器件

以IGZO(铟镓锌氧化物)代表的宽禁带氧化物半导体在三维堆叠存储器与后道兼容逻辑器件中具有重要的应用潜力。吴燕庆研究员、黄如院士团队在国际上首次通过三维堆叠的围栅纳米片结构大幅提高了IGZO晶体管的电学性能,对比传统平面单层沟道晶体管性能提升一倍。整个工艺的热预算不高于300℃,有良好的后道工艺兼容性。在三维堆叠的基础上,通过优化栅介质的厚度使IGZO晶体管的电学性能进一步提升。沟长为50 nm的IGZO NSFET实现了最高1.13 mS/μm的跨导、2.05 mA/μm的开态电流,与低至66 mV/dec的亚阈斜率,综合性能达同类器件最高水平。在实现优异开态性能的同时,IGZO NSFET同时实现了小于10-8 μA/μm(测试精度限制)的极小关态漏电流和大于1011的开关比。该工作以“First Demonstration of Sequential Integration for Stacked Gate-All-Around a-IGZO Nanosheet Transistors with Record Id = 2.05 mA/μm, gm = 1.13 mS/μm and Ultralow SS = 66 mV/dec”为题发表。

4、首次实现高可靠性非晶氧化物半导体顶栅器件

非晶氧化物半导体因其高迁移、低关态漏电和低热预算等特点,近年来在高性能逻辑器件、动态存储器和射频器件等领域受到了广泛的研究。然而受自热效应等器件可靠性的制约,当前的氧化物半导体器件绝大多数为背栅结构,而更利于尺寸缩减和工艺集成的顶栅器件实现难度极大。针对上述问题,吴燕庆研究员、黄如院士团队对基于氧化物半导体ITO的晶体管进行顶栅工艺和衬底散热优化,系统研究了器件的偏压温度不稳定和热载流子退化测试。通过采用高热导率的SiC衬底,大幅提升了器件的稳定性,60 nm沟长ITO顶栅顶栅晶体管在85 oC时跨导为900 mS/mm,开态电流为2.32 mA/mm,分别相对此前同类工作最优值提升了2.5倍和2倍。此外,首次制备了顶栅ITO射频晶体管,500 nm和100 nm沟长器件截止频率(fT)分别为10.2 GHz和48 GHz,实现了基于非晶氧化物半导体的最高射频性能。该工作展示了非晶氧化物半导体在面向三维集成的高速器件和电路领域的应用潜力。该工作以“First demonstration of top-gate indium-tin-oxide RF transistors with record high cut-off frequency of 48 GHz, Id of 2.32 mA/mm and gm of 900 mS/mm on SiC substrate with superior reliability at 85 oC”为题发表。

5、热载流子可靠性的微观机理与TCAD仿真方法

进入FinFET时代以来,新结构和新材料的引入使得CMOS器件即便工作在较低的VDD时,仍然面临严重的热载流子退化(HCD),这是制约先进工艺节点可靠性的关键瓶颈之一。然而,HCD的微观机理研究一直是个谜团。例如,历史上随着工艺节点的微缩,HCD却表现出“起起落落”的现象,机理不清,严重影响PDK建模和TCAD仿真的准确性或适用性以及可预测性。王润声教授-黄如院士团队与中科院半导体所刘岳阳研究员以及上海交通大学等多个单位合作,在HCD的界面缺陷产生机制的研究有了新的突破。首次通过实时的含时密度泛函理论(rt-TDDFT)验证了Si-SiO2界面缺陷生成过程中载流子与Si-H键作用的共振散射机制,发现了真实界面的氢原子共振态能量呈现多个峰的分布特性,导致Si-H键断裂的强度与载流子能量不呈现简单的单调关系。基于上述科学发现,建立了基于共振态全能谱分布的HCD界面缺陷产生模型,以及兼顾效率与准确性的TCAD仿真框架,不仅可以精准实现对HCD退化特性的普适性预测,揭示了随工艺节点“起起落落”的根源,还可以涵盖不同晶面和不同载流子类型的结果,为厘清HCD的微观机理、建立先进节点HCD预测模型提供了重要依据。该工作以“New Insights into the Interface Trap Generation during Hot Carrier Degradation: Impacts of Full-band Electronic Resonance, (100) vs (110), and nMOS vs pMOS”为题发表。

二、新型存储器及可靠性研究

1、面向先进逻辑工艺节点的高密度高可靠阻变存储器

嵌入式非易失性存储器是可移动电子设备等SoC芯片中不可或缺的部分,而28纳米以下工艺节点尚无成熟的嵌入式非易失性存储器解决方案。新型阻变存储器(RRAM)是当前最具潜力的下一代嵌入式非易失性存储器和存算一体芯片技术的候选技术之一。北京大学集成电路学院蔡一茂教授-黄如院士团队首次提出基于无浅沟槽隔离的动态晶体管调控技术与室温自钝化侧壁存储单元的高密度、高可靠RRAM技术,基于上海华力集成电路制造有限公司标准商用40nm CMOS量产平台研制了面向40nm、28nm及以下先进工艺节点逻辑工艺兼容的高密度、高可靠RRAM成套工艺,该技术打破了同节点RRAM存储密度记录,单位密度超过15.43 Mb/mm2,拥有150°C下10年的高温数据保持特性,且具有超过4bit的多值存储特性。研制的RRAM技术在12英寸晶圆和多款不同容量的芯片完成了可靠性测试,展现了该技术在工业级存储应用领域和AI存算一体芯片领域应用的巨大潜力。该工作以“A Logic-Process Compatible RRAM with 15.43 Mb/mm2 Density and 10 years @150°C retention using STI-less Dynamic-Gate and Self-Passivation Sidewall”为题发表。

2、首次实现具有高抗扰动性的无选择管铪基铁电随机存储器

氧化铪基铁电材料具有微缩性好、CMOS工艺兼容等优势,基于铪基铁电材料的铁电存储器因其具备高速、超低功耗、非易失和高密度潜力近年来引起了学术界和业界的广泛关注。然而,氧化铪基铁电材料通常具有多晶多畴的特性,在无选择管的交叉点阵存储器中极易受访问串扰以及多次访问扰动的影响,严重影响存储器正常工作,阻碍了其面向高密度的三维交叉点阵结构的发展。针对上述问题,面向高密度铁电存储应用,北京大学黄芊芊研究员-黄如院士团队提出了超低扰动的氧化铪基3D交叉点阵铁电存储器方案,实现了国际首个无选择管铪基铁电随机存储器,极大降低存储器的误码率的同时,可以将存储密度拓展到4F2/N。通过对氧化铪基铁电存储器扰动问题进行系统性研究与优化,采用界面与应力优化等手段实现了铪基铁电材料的抗扰动性与自发极化强度等国际领先的综合性能,并进一步基于提出的“扰动-恢复”阵列操作脉冲模式解决了多次访问扰动问题,极大提升了无选择管铁电随机存储器操作可靠性。基于上述技术,实验制备的1kbit铪基铁电存储阵列成功实现了阵列级低扰动访问,为实现高密度、高可靠的超低功耗新型非易失存储器奠定了基础。该工作以“First Demonstration of Hafnia-based Selector-Free FeRAM with High Disturb Immunity through Design Technology Co-Optimization”为题发表,并获得2023 IEDM Best Student Paper Award提名。

3、首次实现高耐久性无退火铪基铁电顶栅晶体管

氧化铪基铁电存储器兼具工艺兼容性、可三维集成、高容量、低功耗等优势,有望成为下一代高速存储设备的基本单元。一般而言,获得铁电正交相(o相)需要高温退火,如何在后道兼容的工艺温度下(< 400℃)制备兼具优异铁电性与可靠性的材料是科研界和产业界的共同难题。该问题在制备铁电顶栅晶体管上尤为严峻,因为原子层沉积的高温过程和化学氛围会导致器件的阈值电压、开关态特性发生严重的性能退化。针对上述问题,吴燕庆研究员、黄如院士团队通过将镧元素引入铪锆氧(HZO)体系中(La:HZO),有效降低了铁电o相的形成能,在300 ℃的沉积温度下,没有经过任何退火处理的La:HZO铁电薄膜呈现了更多的铁电o相和更少的m相,相应的金属-铁电介质-金属电容(MFM)表现出30 μC/cm2的两倍剩余极化强度(2Pr)。此外,将La:HZO应用到氧化物半导体氧化铟镓锌(IGZO)顶栅铁电晶体管上,首次实现了无需任何退火工艺的顶栅铁电晶体管。得益于优异的铁电性能和更少的非铁电相,40 nm沟长的顶栅晶体管表现出了在存储窗口(MW)达到3.1V下108的耐久性以及存储窗口为1.9 V下1010的耐久性。该工作以“First Demonstration of Annealing-Free Top Gate La:HZO-IGZO FeFET with Record Memory Window and Endurance”为题发表。

4、先进动态随机存储器的可靠性研究

随着动态随机存储器(DRAM)微缩至20纳米以下技术节点,基于gate-first工艺的高k/金属栅器件已经被应用于DRAM外围电路中,因而可靠性(特别是SWD电路中的厚栅氧器件)成为了新的挑战。王润声教授-黄如院士团队与上海交通大学纪志罡教授团队、中科院半导体所邓惠雄研究员以及北京超弦存储器研究院等单位合作,系统地研究了DRAM外围电路器件的负偏压温度不稳定性(NBTI)和关态应力退化(OSD)两大关键可靠性问题,首次基于先进的表征分析技术揭示了引起NBTI和OSD退化的陷阱类型,发现SiON层NBTI缺陷的是氢桥和羟基构型,高k层NTBI缺陷的是氮间隙构型,该结论有助于进一步有针对性地优化工艺。同时,基于不同陷阱类型建立了准确的老化预测集约模型,可以预测不同偏压域的NBTI和OSD的长期寿命。此外,还探究了上述可靠性机制引起SWD电路老化对DRAM保持时间的影响,为高性能和高可靠DRAM设计提供了指导。该工作以“Comprehensive Study of NBTI and Off-State Reliability in Sub-20 nm DRAM Technology: Trap Identification, Compact Aging Model, and Impact on Retention Degradation”为题发表。

5、基于铁电晶体管阵列的强稳健性物理不可克隆函数

物理不可克隆函数(PUF)作为硬件安全原语,利用器件制备的工艺涨落或工作过程中的物理随机机制作为不可预测的硬件指纹,被广泛应用于设备的身份验证和各类通讯安全协议中。相较于传统CMOS PUF,基于新型非易失存储器的PUF兼备低硬件、功耗代价和可重构能力,但也面临可靠性较差、安全性较低的问题,影响其实际应用。针对此方面的挑战,唐克超研究员、黄如院士课题组首次提出了基于1T铁电晶体管(FeFET)阵列的可重构强稳健性PUF。该FeFET PUF利用铁电子回滞(minor loop)中间极化状态的高随机性作为熵源,结合汉明距离比较和窗口比较器的CRP生成方案,为PUF引入了非线性的异或操作以增强其抗机器学习的安全性,同时保持了低误码率(BER)。通过对所述的协同优化方案进行阵列级实验验证和测试,本工作的FeFET PUF在100°C下的误码率仅有1.7%,且在机器学习攻击下的猜测准确率相较于其它NVM PUF降低了20%,同时展现出了较高的可靠性和安全性优势。本工作对强稳健性、可重构性和低面积、功耗开销的PUF设计和边缘端设备安全的硬件实现有重要意义。该工作以“A Novel FeFET Array-Based PUF: Co-optimization of Entropy Source and CRP Generation for Enhanced Robustness in IoT Security”为题发表。

三、感存算融合器件研究

1、超高灵敏感内卷积视觉传感器件

视网膜仿生传感器件以并行方式采集和处理视觉信息,减少冗余数据传输和功耗,近年来受到极大关注。具有高灵敏光电响应的视网膜仿生传感器件,能够高精度采集复杂场景,尤其是暗光环境的信息,进而有效提取其高分辨率时空特征,通过感内卷积运算,完成边缘端智能检测识别任务。目前,视网膜仿生传感器件主要通过光/电场调控的正负性双极光电响应执行感内卷积运算。有效的光/电场调控需要较薄的光电传感层,然而,较薄的光电传感层受限于低吸光系数,导致现有双极光电传感器件的光电转换效率较低,限制其在弱光环境的应用。因此,需要探索新型光电传感材料和器件结构,以期实现高灵敏、可调节、正负双极光响应视觉传感器件。北京大学贺明研究员-黄如院士团队设计构建可重构钙钛矿/铋氧硒有机-无机异质结光电晶体管器件,调控异质结界面载流子输运,实现超高灵敏的正负双极光响应,双极光响应度达到107 A/W,能够有效执行弱光环境下感内卷积运算,可工作弱光强度低至0.1 𝜇W/cm2,对于提高传感器内边缘检测识别任务效率,完成复杂场景预处理功能具有重要意义。该工作以“Ultrasensitive Retinomorphic Dim-Light Vision with In-Sensor Convolutional Processing Based on Reconfigurable Perovskite-Bi2O2Se Heterotransistors”为题发表。

2、面向机器视觉校正的RRAM多核混合域多项式加速存内计算芯片

随着自动驾驶、无人机测绘等计算机视觉应用中图像像素的不断提高,端侧机器视觉应用中光学畸变校正对芯片算力和能效提出了更高的要求。采用霍纳(Horner)法则(即秦九韶算法)可以有效提升Brown-Conrady模型等多项式畸变矫正算法的计算效率,但基于传统CMOS一阶运算单元实现该法则中的高阶运算面临算力和硬件开销挑战。蔡一茂教授、黄如院士团队首次提出基于阻变存储器的混合域三元乘法加速计算策略,高效匹配了霍纳多项式加速算法。通过充分利用1T1R阻变存储器阵列中的信号多输入端口,结合时域数据流设计和差分权重映射方案,实现了高精度模拟域三元乘法操作运算。团队与上海集成电路研发中心合作首次基于商用标准40nm CMOS平台研制了基于阻变存储器的多核高阶矩阵-向量计算芯片系统,基于该多项式加速原型芯片实现了镜头畸变校准,校准算力达到158M pixels/s,能效达到3.81G pixels/W,校准效果达到专业软件相同校准水平,展现出基于阻变存储器的存内计算在光学畸变矫正系统的应用潜力。该工作以“Hybrid-Domain In-Memory Polynomial Acceleration based on 40nm RRAM Multi-Core Chip for Machine Vision Calibration”为题发表。

四、GaN功率器件研究

随着电动汽车、清洁能源、数据中心等新型电子电气设备的涌现,现代社会对于高效率、小型化的电源管理系统的需要愈发迫切。传统的Si功率半导体器件的性能已经趋近其自身理论极限,宽禁带半导体GaN功率器件理论上可以实现Si功率器件千分之一的导通损耗,实现电源系统体积缩小10倍以上,因此成为近年来全球半导体领域的研究热点。目前,GaN功率器件还面临一些关键的技术挑战:1)GaN功率器件的栅极驱动方式与传统Si功率器件有巨大差异且呈现出阈值电压不稳定性;2)GaN功率半导体的高频优势难以发挥,GaN功率集成电路受限于高压串扰效应迟迟难以实现;3)千伏级超高压GaN功率电子器件,受限于深能级陷阱导致的动态电阻退化,长期未能实现突破。北京大学集成电路学院魏进课题组联合物理学院沈波课题组针对上述重大技术挑战开展了研究工作。

第一项工作展示了一种Si-like增强型GaN功率器件,同时实现了>15V的栅极驱动范围与稳定的阈值电压。如何实现Si-like的GaN功率晶体管就一直是该领域的核心难题。目前主流的p型栅GaN晶体管虽具有较稳定的阈值电压,然而其栅极驱动范围较小;而MIS栅GaN晶体管,虽具有较大的栅极驱动范围,但其阈值电压稳定性较差。北京大学团队提出一种metal/insulator/p-GaN栅GaN晶体管结构,结合了MIS栅与p型栅的优点,并额外引入一个p-GaN电势稳定器用以控制器件开关过程的动态特性。该工作使得电路设计人员可以像使用Si功率器件一样使用GaN功率器件,极大的降低了基于GaN功率器件的电路设计复杂性,有望大幅度拓展GaN功率器件的应用场景。该工作以“Simultaneously Achieving Large Gate Swing and Enhanced Threshold Voltage Stability in Metal/Insulator/p-GaN Gate HEMT” 为题发表。

第二项工作展示了世界上首款体硅衬底650V GaN桥式集成电路芯片。目前,650V体硅衬底GaN分立器件已实现商用化,然而难以实现高频工作。GaN桥式集成电路芯片是推动实现高频开关电源系统的关键技术。然而,基于传统体硅衬底GaN寄生制备的桥式集成电路中,衬底引起的高压串扰效应造成GaN功率器件性能的严重退化。因此,团队提出并制备了一种具有”virtual body”的增强型p型栅GaN晶体管,通过”virtual body”对衬底高压串扰信号进行屏蔽,从而展示了无串扰效应的650V GaN桥式集成电路芯片。该集成平台与目前商业化的p型栅GaN晶体管制备工艺兼容,将推动GaN功率半导体技术从分立器件拓展为集成电路领域。该工作以“650-V GaN-on-Si Power Integration Platform Using Virtual-Body p-GaN Gate HEMT to Screen Substrate-Inudced Crosstalk”为题发表。

第三项工作展示了世界上首款6500V增强型p型栅GaN晶体管,该器件具有极低的动态导通电阻。在此之前,增强型p型栅GaN晶体管已经在650V电压等级的消费类电子领域实现了商业化应用,但在千伏级的工业类电子领域应用却仍然受限,主要是由其高动态导通电阻导致的。为解决该问题,北京大学团队提出并成功制备了一种新型的有源钝化结构器件。所制备器件击穿电压得到大幅度提升,实现了大于6500V的耐压能力。传统GaN高压器件在1200V以上的电压应力下,动态导通电阻与静态导通电阻的比值往往大于2;而团队制备的新型器件在4500V电压应力下,该比值仅为1.02。该工作攻克了制约GaN功率器件近30年的动态电阻难题,打破了GaN功率器件不适用与千伏级工业电子应用的固有观念。该技术将为新能源汽车、轨道交通、电力传输、分布式储能等应用设备提供高效率、轻量化、小型化的能源管理系统。该工作以“6500-V E-mode Active-Passivation p-GaN Gate HEMT with Ultralow Dynamic RON” 为题发表。

结语

北京大学一直是我国集成电路学科建设和科技创新改革的排头兵。从黄昆先生,到王阳元院士,到黄如院士,再到而今的一批青年骨干教师与学生,芯火相传。一代又一代北大集成电路人,不忘初心、披荆斩棘、砥砺前行,在微观纳米尺度上巧夺天工、不懈求索,为我国关键核心技术攻关及高水平科技自立自强持续贡献力量。