注:本文copy链接如下,正好最近在研究serdes的接口电路,所以基于此篇论文对serdes一些关键概念和模块做相关的解读。

一种28Gbps高速SERDES发射器 (journalmc.com)

一、引言

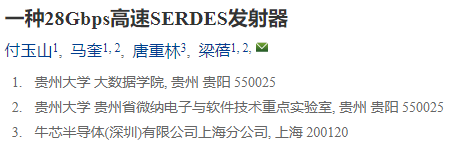

信息时代,庞大的数据流需要高质量、高速的传输,对传输技术提出了越来越高的要求,serdes的出现就是为了解决这个问题,serdes是一种时分多路复用(TDM)、点对点(P2P)的高速串行通信技术。

serdes一般包括三个组成部分:

(1)发送端(TX/transmitter);

(2)接收端(RX/receiver)

(3)公用的锁相环(PLL)

发射端将低速的并行信号转换成了高速的串行信号,然后经过编码、加重等操作处理后发出。

本文介绍了一种采用3-tap结构的基于SST驱动的发射器,分析了基于时钟占空比校准的原因以及原理,设计了一种阻抗调谐与去加重解耦的驱动切片单元,简化了驱动器的控制逻辑,发射器的典型速率为28Gbps,工作电压为0.9V/1.8V,预加重最大为-8dB,去加重为-12dB,整个TX的抖动大约为0.3UI。

二、发射器电路的设计背景和架构

2.1、发射器的设计背景

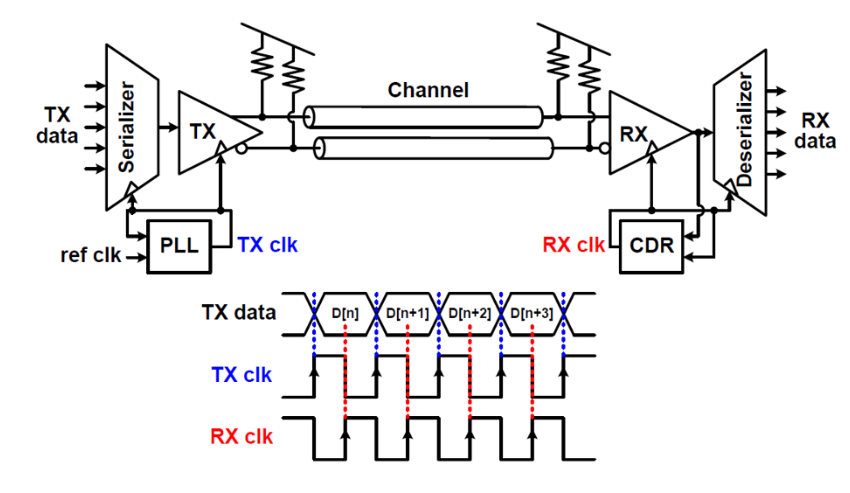

本文介绍的28Gbps发射器设计,主要应用于收发器的发送端,一个完整的发送端如下图所示,左侧是TX PCS(物理编码子层),主要包含了8b/10b编码、通道绑定、PRBS扰码产生、POR control等;TX PMA(物理媒介适配层),包含了高速串并转换、预/后加重、时钟占空比校准、驱动等模拟为主的电路,还有PLL产生时钟、T-coil带宽扩展与ESD保护模块,PCS层接FPGA的数据并传送到PMA层,并对其实现控制。

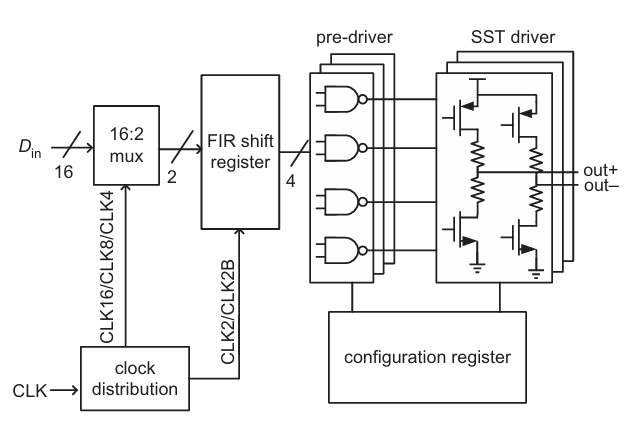

2.2、发射器的架构

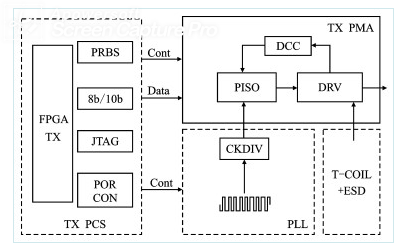

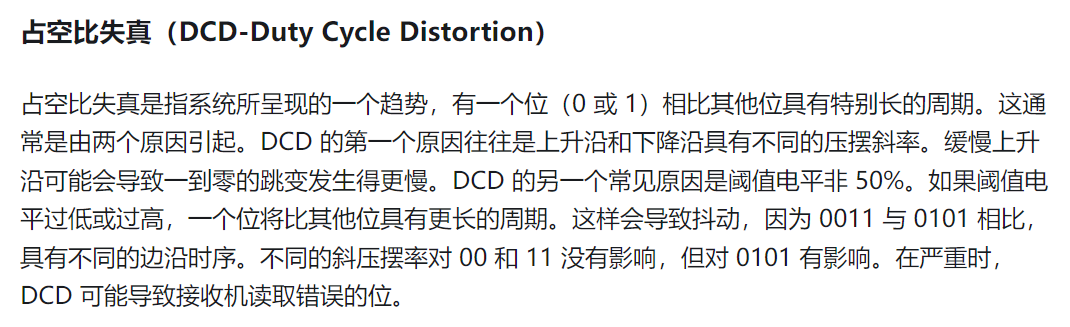

发射器就是将PCS传递而来的并行低速的数据转换为串行的高速数据,并发送出去,下图显示了一个完整的发射器的架构,从数据通路PCS传递而来的20-bit数据首先进入PISO模块,先转换为4-bit,再转化为2bit,即奇偶序列,然后经过3tap,输出提前1UI的pre_e/o,正常的main_e/o以及延后1UI的post_e/o,此是下一步加重的数据准备,下一步的pre_drive中主要实现加重,加重的系数由数字部分实现,具体的程度一般由协议限制规定,预驱动输出半速率的包含加重均衡信息的奇偶串行数据给驱动级,驱动级将加重信息实现,并实现全速率的差分输出,差分输出端接了一个T-coil电感模型,以拓宽发射器的带宽,并做了ESD保护。

注:电感为什么可以增加带宽,可以参考:《Bandwidth Extension Techniques for CMOS Amplifiers》

从时钟通路分析,发射器所需时钟由共用PLL提供,时钟频率为半速率(14 GHz),时钟首先进入PISO(parallel-in,serial-out),之后数据将附带时钟信息,一直传递到Drive,Drive处判决比较时钟的占空比是否为50%,结果反馈至PISO处,PISO再次调节时钟占空比,以此校准时钟信号的占空比。

三、时钟占空比校准电路的原理和结构

3.1、DCC的基本结构

本设计中时钟信号的频率为14 GHz,即采用的是半速时钟结构,设计中时钟信号的占空比必须为标准的50%.因为时钟速率为数据速率的一半,故Drive block中时钟上升沿采奇序列数据,下降沿采偶序列数据.由于采样的速率很高,单个采样周期只有35.7 ps,在如此短的时间内要保证:【即建立保持时间需要满足如下条件】

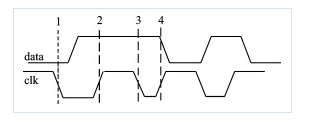

如果占空比失真,就会造成采样失败或是重复,误码率增大甚至直接乱码如下图所示所示,1,2,3处采样时钟的占空比为50%,所以可以准确采到数据,当占空比失真时,如4处,上升沿提前到来,其Tsu和Th时间数据均为高电平,所以将采到错误的高电平数据,本该采样的1 bit的低电平数据被漏采,输出数据误码率变大。

此外,占空比比失真造成的直接影响就是DCD增大,导致TJ超出预期.协议中对占空比的要求为1.25 ps(28Gbps),所以半速率时钟的发射器需要时钟占空比需控制在46.5%~53.5%.

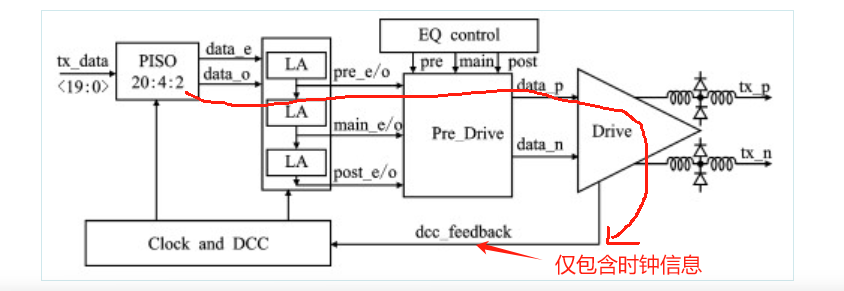

备注:所谓的DCD即占空比失真

3.2、DCC的结构

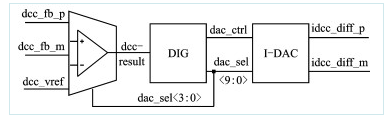

本设计中DCC的基本结构如下图所示:

首先是一个比较器,Drive处反馈的的信号(差分)dcc_fb,与基准电压进行比较,由dac_sel控制三输入中两两比较的次序.dcc_fb是从PISO处与数据链平行的时钟信号,经过相同的block,最后由Drivec处驱动输出的反馈信号。

与tx_p/n(数据输出信号)不同的是,dcc_fb仅包含时钟信息.基准点电压为Vp/2, 可由电阻分压得到.比较的结果传给数字部分,数字端对得到结果做出判断,输出增大或减小占空比的多位控制信号,最后由经I-DAC转化为电流信号,反馈给PISO中分频部分。

四、驱动级的选择和设计

4.1、电流模逻辑(CML)驱动级

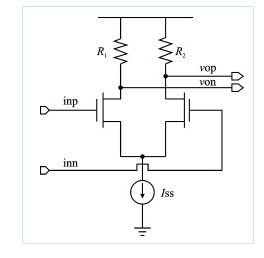

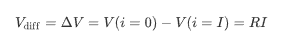

CML速率最高可达10 Gbps以上,是现在应用最广泛的驱动结构.如下图所示,一个差分的CML的主要结构由电流源,M1,M2开关管组成,还需要上拉电阻, 因为NMOS晶体管只能有效的驱动下降沿,通过上拉电阻提高对上升沿的驱动能力,为了输出端的阻抗匹配,降低信道反射,一般情况下,取R1=R2=50Ω.尾部的电压控制电流源用于改变用于驱动负载的电流量[9].

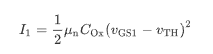

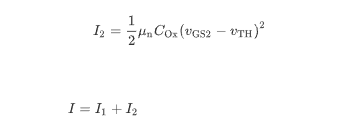

CML工作时,M1,M2交替开断,当M1打开,M2关断时,尾电流流过左边忽略支路,忽略沟道长度调制效应:

反之,M1关断,M2打开:

将上面三式联立,可得:

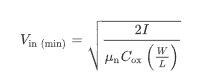

求解完上述方程式后,以等于电流源的电流导通晶体管时的最小电压为:

电压的摆幅即为:

由上述推理可知CML逻辑的电压摆幅是电阻负载和尾电流的乘积. 因此,可以通过减小电压摆幅来提高电路速度,这也将有助于降低噪声容限,但是电压摆幅越大其功耗就越大。

4.2、源串联终端(SST)驱动级

源串联终端(source-series-terminated, SST),是一种电压模式的驱动级结构。

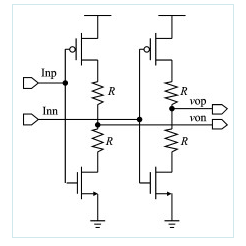

不同于CML结构,SST是电压驱动型的结构,基本的拓扑结构如下图所示,分为上拉和下拉分支,由PMOS和NMOS开关晶体管与串联终端电阻R构成,两分支均与传输线阻抗匹配(通常为50 Ω,差分为100 Ω).当drive为高电平时,P管导通,上拉部分工作,当为低电平时N管导通,下拉部分工作,其输出摆幅为:

输出摆幅受电源电压影响,与电流无关.SST结构控制简单,可以灵活的适配多种不同的协议.理论上,在相同摆幅下,SST驱动级的功耗只有CML驱动级的1/4,SST摆幅最大可到1 V以上,CML若达到较高的摆幅,功耗太大.所以本设计选择了SST结构.

注:

SST的典型结构如下,SST-Driver由于受限于电源电压,差分摆幅只能做到VDD,所以在SST结构的接口中,通常设计为预加重;

常见的驱动级如下图,主抽头main控制的L片slice由数据序列d[K]来驱动,post控制的M片切片单元由数据序列d[k]的1 bit延迟并取反的d[k-1]来驱动,这种拓扑结构的问题在于,发射机阻抗调谐与加重设置混在一起,均由M与L的数量决定,不能实现均衡与阻抗调谐的自由控制.例如,如果K需要增加10个启用的限幅单元以满足新的传输线阻抗,那么则需要增加L=7个限幅单元,并且必须增加M=3个限幅单元以维持所需的8dB信道均衡.在此示例中,如果增量不是10的倍数,则不能保持所选择的均衡设置

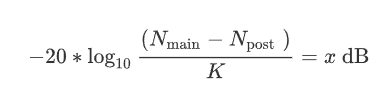

下图所示的设计可以避免此缺点,是将一个SST结构,平均拆分为多个SST结构组成的条带单元,如图中一个条带单元由3个SST驱动结构组成(此处以3个为例,可由多个SST驱动构成,数目越多,均衡分辨率越高),那么权重的步长就为Vp/(23-1),其中Vp代表电压摆幅.最大的权重由main驱动,中间的权重由post驱动,最小的权重由pre驱动,那么条带单元的post由式(9)可得约为x≈10.88 dB,同理可得pre约为7.36 dB.pre与post的实际权重由PCIE协议决定。

这种拓扑的优点是,加重的程度与实际使能的条带单元数K无关,加重的程度由单个条带单元内的SST结构的权重配比实现.而K的数量仅仅由实际阻抗的大小来决定. 因此,阻抗调谐和加重控制相互解耦,这大大简化了SST驱动级的控制逻辑.

本设计由于将一个SST驱动级拆分成了三份,这就需要前级的均衡控制更加精细,增加了一定的控制位数,电路设计的工作量增加,一定程度上增加了电路的规模.

设计的发射器电路基于中芯国际14 nm的FinFET工艺的PDK,输入20 bit的PRBS7扰码,运用cosim(VCS+XA)联合仿真平台.仿真结果眼图如图所示,整体开眼情况良好,无毛刺,占空比无失真,眼高约为0.7 V,眼宽接近35 ps,TJ约为2.5 p,小于0.1 UI.

5.2 发射器的实际测试结果

对本设计介绍的28 Gbps速率的SERDES流片并进行测试,采用力科示波器所得眼图如图所示,从测试结果可以看出,发射器在28 Gbps速率下,眼图开眼较好,实测TJ约为0.301UI,略超出设计指标,原因一是搭建测试环境时,经过了若干的接口及连接线,二是SERDES是以芯片形式焊接在PCB板上,没有集成在SOC内,这两部分贡献了部分RJ;三是所用参考时钟源并没有做专门处理,贡献了部分DJ;这三方面对Jitter的贡献,导致了TJ略大.

下图显示了在5种corner下,pre-cursor的测统计结果,(横坐标为设计code控制字,纵坐标为加重程度)数据显示在5种不同的corner下,其在设计的code下的变化趋势是一致的,其中最小的情况出现在TT corner下,code=0时,约为-0.1 db,设计值为0 dB,最大的情况出现SS corner低压高温时,在满量程code=28(2b’011100)下,为-8.85 dB.

下图是post-cursor的测试结果,5个corner下随code值变化,去加重程度呈线性变化,最小的情况出现在TTcorner下,约为-0.16 dB,最大同样出现在SScorner低压高温时,在满量程code=35(2b'100011)下,为-12.7 dB.

从测试结果分析,pre-pursor的与post-pursor虽略大于设计值,但均成线性变化,pre的最小步进单位约为0.3 dB,post的最小单位约为0.35 dB,基本达到设计要求.

介绍了SERDES发射器电路的基本原理,着重说明了采用的具体架构,分析了设计DCC的必要原因以及实现方式;重点介绍了驱动级的两种常用结构,优化设计了一种均衡与阻抗匹配解耦的SST驱动单元电路设计.本文介绍的发射器电路在某28Gbps SERDES电路中流片和测试.测试结果显示,本文介绍的发射器电路的眼图和加重均衡等基本达到设计指标,满足PCIE 4.0标准。