RZ/G2L串口简介

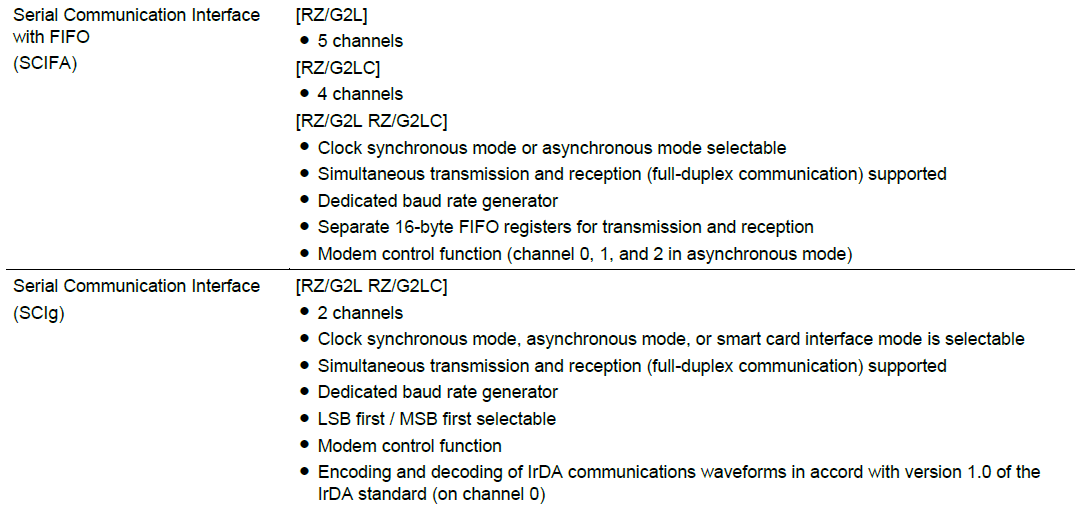

瑞萨RZ/G2L的串口简称SCI,全称Serial Communication Interface。

RZ/G2L有两种串口,一种带FIFO叫SCIFA,另一种不带FIFO叫SCIg。

所以,RZ/G2L有5路SCIFA和2路SCIg总共7路的串口。

RZ/G2L串口驱动

包含驱动代码和设备树两部分:

内核中的驱动文件sh-sci.c

该源码文件路径:drivers/tty/serial/sh-sci.c,该驱动代码包含SCIFA和SCIg两种型号的完整驱动代码。

编译内核的时候需进行以下配置

egrep -rin "CONFIG_SERIAL_SH_SCI" .out/.config2180:CONFIG_SERIAL_SH_SCI=y2181:CONFIG_SERIAL_SH_SCI_NR_UARTS=182182:CONFIG_SERIAL_SH_SCI_CONSOLE=y2183:CONFIG_SERIAL_SH_SCI_EARLYCON=y2184:CONFIG_SERIAL_SH_SCI_DMA=y

该配置能够确保sh-sci.c的驱动代码能够被编译包含到Image中。

github上提供的内核源码的defconfig中默认已包含SCI驱动代码的编译。

SCI串口的设备树节点在r9a07g044.dtsi中定义,分别定义了scif0~4, sci0~1共7路。

scif0: serial@1004b800 {compatible = "renesas,scif-r9a07g044";reg = <0 0x1004b800 0 0x400>;interrupts =380 IRQ_TYPE_LEVEL_HIGH>,382 IRQ_TYPE_LEVEL_HIGH>,383 IRQ_TYPE_LEVEL_HIGH>,381 IRQ_TYPE_LEVEL_HIGH>,384 IRQ_TYPE_LEVEL_HIGH>,384 IRQ_TYPE_LEVEL_HIGH>;interrupt-names = "eri", "rxi", "txi","bri", "dri", "tei";clocks = <&cpg CPG_MOD R9A07G044_SCIF0_CLK_PCK>;clock-names = "fck";dmas = <&dmac 0x4e79>, <&dmac 0x4e7a>;dma-names = "tx", "rx";power-domains = <&cpg>;resets = <&cpg R9A07G044_SCIF0_RST_SYSTEM_N>;status = "disabled";};scif1: serial@1004bc00 {compatible = "renesas,scif-r9a07g044";reg = <0 0x1004bc00 0 0x400>;interrupts =385 IRQ_TYPE_LEVEL_HIGH>,387 IRQ_TYPE_LEVEL_HIGH>,388 IRQ_TYPE_LEVEL_HIGH>,386 IRQ_TYPE_LEVEL_HIGH>,389 IRQ_TYPE_LEVEL_HIGH>,389 IRQ_TYPE_LEVEL_HIGH>;interrupt-names = "eri", "rxi", "txi","bri", "dri", "tei";clocks = <&cpg CPG_MOD R9A07G044_SCIF1_CLK_PCK>;clock-names = "fck";dmas = <&dmac 0x4e7d>, <&dmac 0x4e7e>;dma-names = "tx", "rx";power-domains = <&cpg>;resets = <&cpg R9A07G044_SCIF1_RST_SYSTEM_N>;status = "disabled";};scif2: serial@1004c000 {compatible = "renesas,scif-r9a07g044";reg = <0 0x1004c000 0 0x400>;interrupts =390 IRQ_TYPE_LEVEL_HIGH>,392 IRQ_TYPE_LEVEL_HIGH>,393 IRQ_TYPE_LEVEL_HIGH>,391 IRQ_TYPE_LEVEL_HIGH>,394 IRQ_TYPE_LEVEL_HIGH>,394 IRQ_TYPE_LEVEL_HIGH>;interrupt-names = "eri", "rxi", "txi","bri", "dri", "tei";clocks = <&cpg CPG_MOD R9A07G044_SCIF2_CLK_PCK>;clock-names = "fck";dmas = <&dmac 0x4e81>, <&dmac 0x4e82>;dma-names = "tx", "rx";power-domains = <&cpg>;resets = <&cpg R9A07G044_SCIF2_RST_SYSTEM_N>;status = "disabled";};scif3: serial@1004c400 {compatible = "renesas,scif-r9a07g044";reg = <0 0x1004c400 0 0x400>;interrupts =395 IRQ_TYPE_LEVEL_HIGH>,397 IRQ_TYPE_LEVEL_HIGH>,398 IRQ_TYPE_LEVEL_HIGH>,396 IRQ_TYPE_LEVEL_HIGH>,399 IRQ_TYPE_LEVEL_HIGH>,399 IRQ_TYPE_LEVEL_HIGH>;interrupt-names = "eri", "rxi", "txi","bri", "dri", "tei";clocks = <&cpg CPG_MOD R9A07G044_SCIF3_CLK_PCK>;clock-names = "fck";dmas = <&dmac 0x4e85>, <&dmac 0x4e86>;dma-names = "tx", "rx";power-domains = <&cpg>;resets = <&cpg R9A07G044_SCIF3_RST_SYSTEM_N>;status = "disabled";};scif4: serial@1004c800 {compatible = "renesas,scif-r9a07g044";reg = <0 0x1004c800 0 0x400>;interrupts =400 IRQ_TYPE_LEVEL_HIGH>,402 IRQ_TYPE_LEVEL_HIGH>,403 IRQ_TYPE_LEVEL_HIGH>,401 IRQ_TYPE_LEVEL_HIGH>,404 IRQ_TYPE_LEVEL_HIGH>,404 IRQ_TYPE_LEVEL_HIGH>;interrupt-names = "eri", "rxi", "txi","bri", "dri", "tei";clocks = <&cpg CPG_MOD R9A07G044_SCIF4_CLK_PCK>;clock-names = "fck";dmas = <&dmac 0x4e89>, <&dmac 0x4e8a>;dma-names = "tx", "rx";power-domains = <&cpg>;resets = <&cpg R9A07G044_SCIF4_RST_SYSTEM_N>;status = "disabled";};sci0: serial@1004d000 {compatible = "renesas,r9a07g044-sci", "renesas,rz-sci";reg = <0 0x1004d000 0 0x400>;interrupts =405 IRQ_TYPE_LEVEL_HIGH>,406 IRQ_TYPE_EDGE_RISING>,407 IRQ_TYPE_EDGE_RISING>,408 IRQ_TYPE_LEVEL_HIGH>;interrupt-names = "eri", "rxi", "txi", "tei";clocks = <&cpg CPG_MOD R9A07G044_SCI0_CLKP>;clock-names = "fck";power-domains = <&cpg>;resets = <&cpg R9A07G044_SCI0_RST>;status = "disabled";};sci1: serial@1004d400 {compatible = "renesas,r9a07g044-sci", "renesas,rz-sci";reg = <0 0x1004d400 0 0x400>;interrupts =409 IRQ_TYPE_LEVEL_HIGH>,410 IRQ_TYPE_EDGE_RISING>,411 IRQ_TYPE_EDGE_RISING>,412 IRQ_TYPE_LEVEL_HIGH>;interrupt-names = "eri", "rxi", "txi", "tei";clocks = <&cpg CPG_MOD R9A07G044_SCI1_CLKP>;clock-names = "fck";power-domains = <&cpg>;resets = <&cpg R9A07G044_SCI1_RST>;status = "disabled";};

设备树文件路径

arch/arm64/boot/dts/renesas/r9a07g044.dtsi

根据项目需要,使能需要使用的设备节点,如欲使用SCIFA2:

&scif2 {pinctrl-0 = <&scif2_pins>;pinctrl-names = "default";uart-has-rtscts;status = "okay";};

注意需通过scif2_pins正确处理IO口复用问题。如果不使用DMA需要将设备节点中的dmas和dma-names删除。

编译内核:

export ARCH=arm64export CROSS_COMPILE=aarch64-none-elf-export PATH=$PATH:/opt/arm/gcc-arm-10.2-2020.11-x86_64-aarch64-none-elf/binmake defconfig O=.out && make -j8 O=.out

使用当前编译生成的内核Image和dtb

.out/arch/arm64/boot/Image.out/arch/arm64/boot/dts/renesas/r9a07g044l2-smarc.dtb

启动板子后就能在系统路径下生成/dev/ttySC2节点。

Linux应用层使用RZ/G2L的串口SCI

RZ/G2L的串口设备节点在Linux应用层遵循POSIX标准,使用方法和PC端的Ubuntu系统并无差别。

RZ/G2L除了支持市面上常用的串口波特率如9600/115200/921600等,实际上除POSIX系统定义的波特率都支持外,RZ/G2L能够支持的最大串口波特率是12.5Mbps,下一篇我们将介绍如何在内核驱动代码中实现RZ/G2L的最大波特率12.5Mbps。

如需了解更详细的使用方法请参考如下网站:

1

瑞萨官网

https://www.renesas.cn/cn/zh/products/microcontrollers-microprocessors/rz-mpus/rzg2l-getting-started

2

RZ产品WIKI网站

https://renesas.info/wiki/Main_Page

您可复制下方网址到浏览器中打开进入瑞萨中文论坛查看:

https://community-ja.renesas.com/zh/forums-groups/mcu-mpu/

未完待续

推荐阅读

RZ/G2L构建Linux开发环境

RZ/G2L添加新的内核模块

RZ/G2L多核异构通信方案介绍