LMK0482X系列是德州仪器推出的高性能时钟调节芯片系列,该芯片目前有三种,分别为LMK04821、LMK04826以及LMK04828,该系列芯片都支持最新的JESD204B协议。本次调试主要以LMK04821为例,对调试过程中出现的一些问题进行总结说明。

其性能描述如下:

<1>. 7对可作为JESD204B的SYSREF时钟;

<2>. 最大输出频率可以达到3.1GHz;

<3>. 输出差分时钟的电平标准可编程选择:LVPECL、LVDS、HSDS、以及LCPECL;

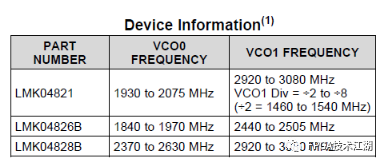

LMK0482X系列的这三款芯片不同之处在于支持不同的VCO,如下图图1所示:

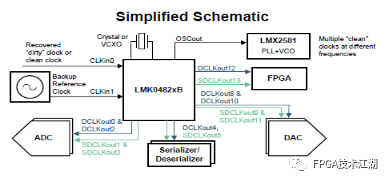

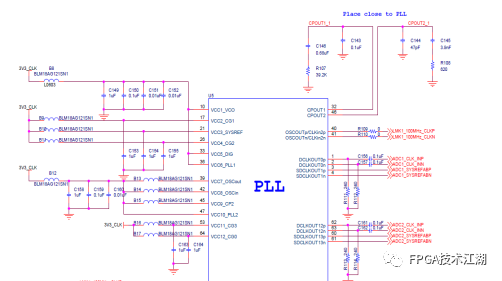

LMK04821芯片的应用示意图如下图图2所示:

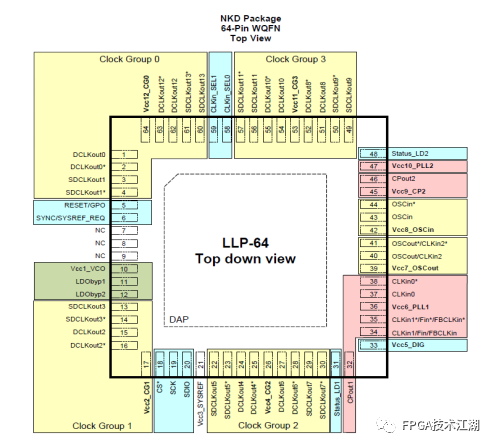

LMK0482X的管脚分布定义图如下图3所示,熟知每个管脚的功能很重要,逐一介绍:

图3

PIN1、2:第0路Device CLK差分输出;

PIN3、4:第1路SYSREF/Device CLK差分输出;

PIN5: 该芯片的复位输入或者是通用GPIO;

PIN6: 该芯片的时钟同步输入端口或者是连续SYSREF CLK请求输入端口;

PIN7、8、9:没用,悬空即可;

PIN10: 电源输入;

PIN11:LDO旁路电容,外接10uf到地;

PIN12:LDO旁路电容,外接0.1uf到地;

PIN13、14:第3路SYSREF/Device CLK差分输出;

PIN15、16:第2路Device CLK差分输出;

PIN17:电源输入;

PIN18:芯片的SPI配置CS信号;

PIN19:芯片的SPI配置SCK信号;

PIN20:芯片的SPI配置SDIO信号;

PIN21:电源输入;

PIN22、23:第5路SYSREF/Device CLK差分输出;

PIN24、25:第4路Device CLK差分输出;

PIN26:电源输入;

PIN27、28:第6路Device CLK差分输出;

PIN29、30:第7路SYSREF/Device CLK差分输出;

PIN31:可编程的状态监测I/O管脚;

PIN32:PLL1的电荷泵输出;

PIN33:电源输入;

PIN34、35:PLL1的参考时钟输入1、零延迟模式下的外部反馈时钟输入、外部VCO输入;

PIN36:电源输入;

PIN37、38:PLL1的参考时钟输入0;

PIN39:电源输入;

PIN40、41:反馈到PLL1,参考输入到PLL2。AC耦合;

PIN42:电源输入;

PIN43、44:PLL2的参考时钟输入、PLL1的反馈时钟输入;

PIN45:电源输入;

PIN46:PLL2的电荷泵输出;

PIN47:电源输入;

PIN48:可编程的状态监测I/O管脚;

PIN49、50:第9路SYSREF/Device CLK差分输出;

PIN51、52:第8路Device CLK差分输出;

PIN53:电源输入;

PIN54、55:第10路Device CLK差分输出;

PIN56、57:第11路SYSREF/Device CLK差分输出;

PIN58:可编程的状态监测I/O管脚;

PIN59:可编程的状态监测I/O管脚;

PIN60、61:第13路SYSREF/Device CLK差分输出;

PIN62、63:第12路Device CLK差分输出;

PIN64:电源输入;

DAP : 散热盘,接地;

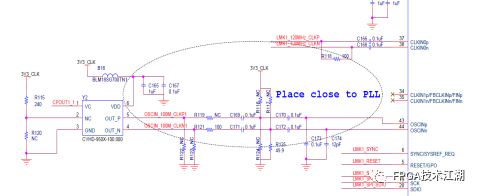

2.1.1 芯片供电是否正常,是否符合器工作的条件,该步骤直接决定芯片能否正常工作,测试点参考下图;

2.1.2 芯片的参考时钟输入是否正常,借助示波器进行检查,CLKin0端的时钟由外部信号源提供,OSCin端的时钟由板上晶振提供,测量进入AD之前时钟是否正常;

LMK04821的配置采用SPI方式,其配置规则通过阅读数据手册提取关键的知识点,如下:

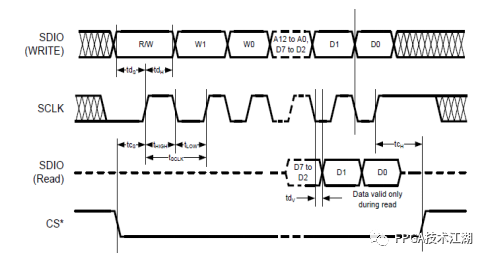

2.2.1 写操作时,CS信号为低电平时,SDIO的数据在SCK上升沿写进芯片,写数据格式为1bit的读写控制位+2bit的0+13bit地址+8bit数据。

2.2.2 读操作时,先写入1bit的读写控制位+2bit的0+13bit地址,然后在接下来SCK的上升沿获取8bit数据;

时序图如下图6所示:

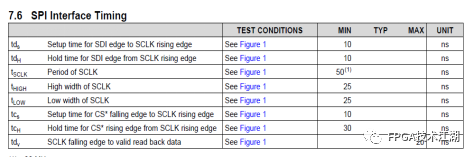

2.2.3 进行SPI时序编写时,务必按照图七的时序要求,除此之外,在FPGA内设计SPI代码时一定要可读可写,这样一来在FPGA配置寄存器时就能够知道每个寄存器内部配置的值是否正确,这一步是控制整个芯片工作时,FPGA要完成的第一步工作。

2.2.4 LMK04821的双PLL级联系统的介绍:

该系列芯片功能非常灵活,一般JESD204B系统的双PLL级联应用最为经典,但是对于传统的应用来说,同样适用。需要注意的是Device CLK不提供单端输出,只有OSCout管脚可以提供LVCMOS单端输出。另外,除了双PLL应用模式,亦可以配置单PLL或者时钟分发模式。

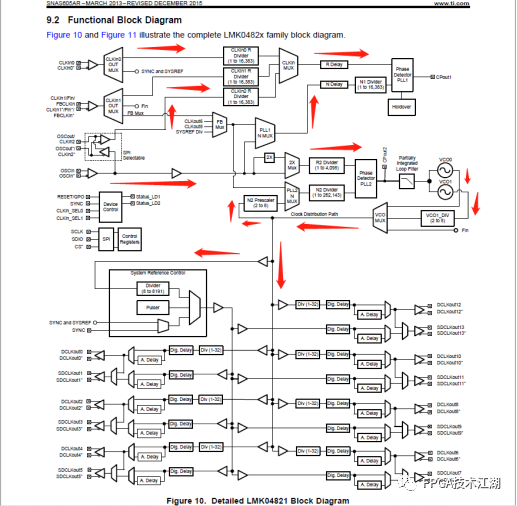

2.2.5 功能框图

2.2.6 寄存配置顺序

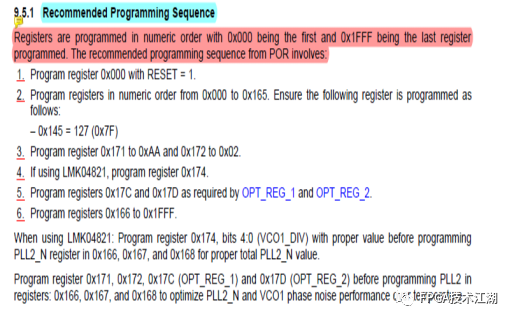

在进行LMK04821寄存器配置的时候,手册里给了一个推荐的顺序,如下图图9所示:

图9

在辅助软件TICS Pro中,生成的寄存器顺序也是严格按照手册中进行配置的。

但是在实际运用中,按照该寄存器配置顺序,时钟输出端并没有正确的时钟输出。实际运用中,将寄存器顺序按照如下顺序进行配置:

1、0X000配置两次,先进行复位,然后0X000再配置00,无操作;

2、然后紧接着从0X100~0X145;

3、0X171~0X17D;

4、0X146~0X16E;

5、0X143(90)、0X149(00)、0X143(两次B0、90)、0X144(FF)、0X143(两次10、11)、0X139(03)、0X002(00);固定数值;尽量不要改变,具体为什么要这样进行配置,对应数据手册进行查阅即可。

注意:在实际应用中,目前为止该寄存器顺序是唯一能够正确产生时钟的顺序,可以参考软件给的寄存器数据,尽量不要改变配置寄存器的顺序。部分寄存器在设计中没有进行配置,比如一些只读寄存器,IC信息相关的寄存器,reback相关的寄存器都没有进行配置,实际操作中无伤大雅,可以不用配置。但是在SPI配置寄存器时,如果要检验寄存器读写是否成功时,可以将这些寄存器进行读操作,确保SPI操作正常。

2.2.7 寄存器对应数据

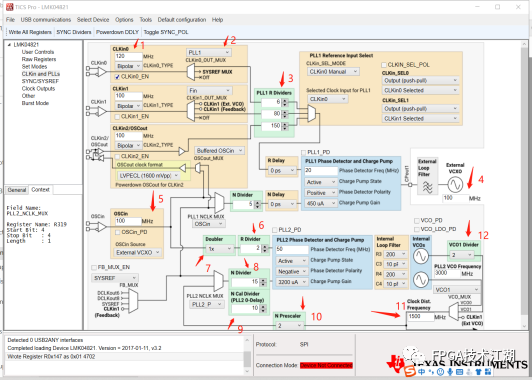

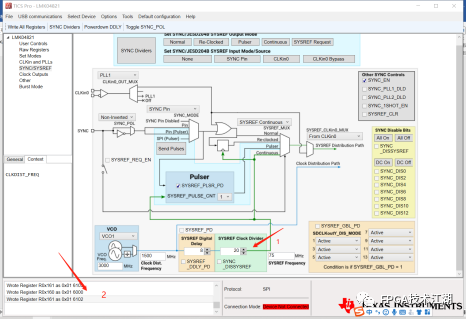

在此之前,确定寄存器配置顺序之后,利用辅助软件TICS Pro软件产生对应的参数,按照6中所示的寄存器顺序进行写操作。软件使用中重要参数的产生以及对应在软件中如何设置见下图图10;

一定要熟练掌握软件运用,明确在产生想要的时钟时,如何进行软件操作,得到相应的系数,软件中每个点如何进行配合;参数之间是如何对应的,建议配合数据手册进行对比,能够事半功倍。

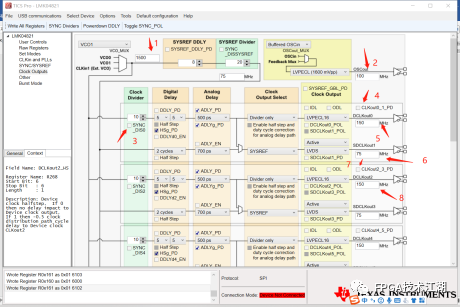

除此之外,时钟输出设置如下图图11所示:

注意:在设定寄存器参数时,操作软件时,会在左下方窗口标记2处显示对应的寄存器以及数值,便于我们很迅速的在数据手册中查到该数值进行了哪些配置;

软件配置时,最重要的几个参数以及对应的寄存器如下:

注意;有些参数需要多个寄存器共同配合使用;另外的寄存器在软件配置过程中会生成,按照具体的设计要求进行软件操作配置,导出参数之后,在对应的寄存器中进行更改即可。

在对LMK04821芯片进行正确配置之后,时钟能够正常输出想要的时钟频率,利用示波器进行测量,都能够直接观测到时钟有输出;程序中更改不同的分频系数,也能够在输出端得到相应的时钟输出。

考虑到系统中要求时钟同源的问题,在对CLKin0参考输入时钟、DCLK、SCLK通过示波器进行起始相位对比观测,发现通过倍频分频后,时钟起始相位存在大概1/4个周期偏差,多次测试,每次都有细微的偏差。

其中,DCLK与SCLK如果输出频率相同时,相位差通过观察,有细微偏差,考虑到示波器使用过程中,探头不稳定原因,暂定相位偏差为0;后期有更好的测试方法时,再进行确认。

阿Q的第一篇项目开发经验分享就到这里结束了,万事开头难,今天已经开启了第一篇,后续有时间还会继续给各位大侠带来更多的项目开发经验分享。各位大侠,有缘再见,祝一切安好!

END

往期精选

FPGA技术江湖广发江湖帖

无广告纯净模式,给技术交流一片净土,从初学小白到行业精英业界大佬等,从军工领域到民用企业等,从通信、图像处理到人工智能等各个方向应有尽有,QQ微信双选,FPGA技术江湖打造最纯净最专业的技术交流学习平台。

FPGA技术江湖微信交流群

加群主微信,备注姓名+学校/公司+专业/岗位进群

FPGA技术江湖QQ交流群

备注姓名+学校/公司+专业/岗位进群