SoC 原型验证环境说明

最近招聘的时候,有很多校招生在询问,原型验证主要的工作内容是什么?使用的语言又是什么?主要操作的平台是什么?未来的职业发展又是什么样子的?。。。。

这里呢,笔者就原型验证平台先做一个简要的说明,至于其它问题,后续有时间了再慢慢撰写;

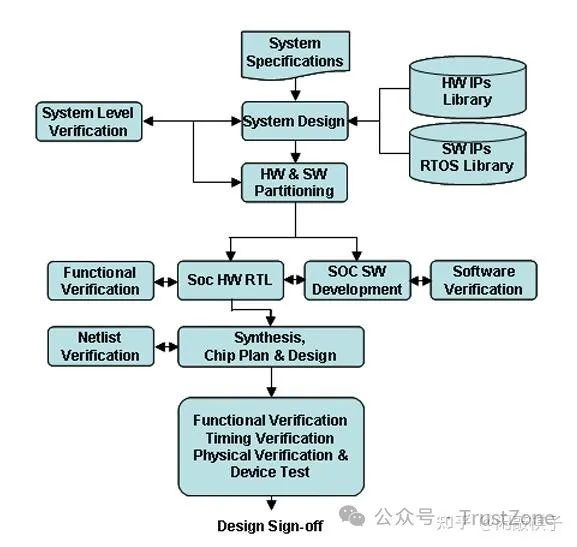

在说相关验证平台的时候,这里简单对验证流程做一个简要的说明,后面有机会再展开描述:

System Design后,Design会交付代码给到DV 验证团队(design verification/System Level Verification),DV验证完成后交付RTL给到原型团队(或者平台团队)进行硬件验证平台的版本迭代,而这里说的验证版本,即是原型同学需要验证的标的~,即基于某个RTL综合的FPGA/Emulation版本进行SOC的原型验证;

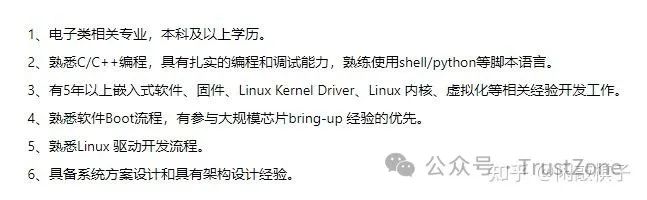

软件平台指代的是平时我们工作的时候,主要使用的一些相关软件、应用工具,比如操作系统,开发语言等等;在说这个之前,大家可以看看原型验证招聘的基本要求:

从上大家已经可以了解到原型验证工程师在平时工作中,会使用到哪些工具:

汇编/C/C++/shell/python , 这个是基本功,原型验证的主要用例开发也是基于汇编以及C来进行的,可能部分自动化平台比如jenkin还会涉及到shell以及python;

Linux/RTOS/Vxworks/AutoSar.... :操作系统应该也是基本功,在工作中,原型的同学会针对各个不同的硬件模块进行驱动开发,而驱动可能运行在linux或者baremater的操作系统上;

当然以上,只是基本要求,事实上目前很多大型SOC的设计公司,要求原型的同学能够自己看懂RTL代码,电路图等等,团队内有时候自嘲说,原型的同学是DV+原型+软件,三位一体,打三分工,拿一分钱。

但是从能力图谱上来说,原型的同学成长的广度是远远高于其他岗位的,因为他能够接触到的知识圈非常丰富(PS,下限也非常低,笔者见过10多年工作经验的还只是会配置寄存器,写写简单驱动~~)

不得不说,从业生涯中,看到过原型的同学转岗做架构师、DV验证、软件开发、软件测试、FAE、流程质量、HR以及项目经理等等的,求职范围非常之大~~~

也有做验证经理、项目经理较多,因为原型验证对于项目的把控能力,风险意识都非常的有经验。

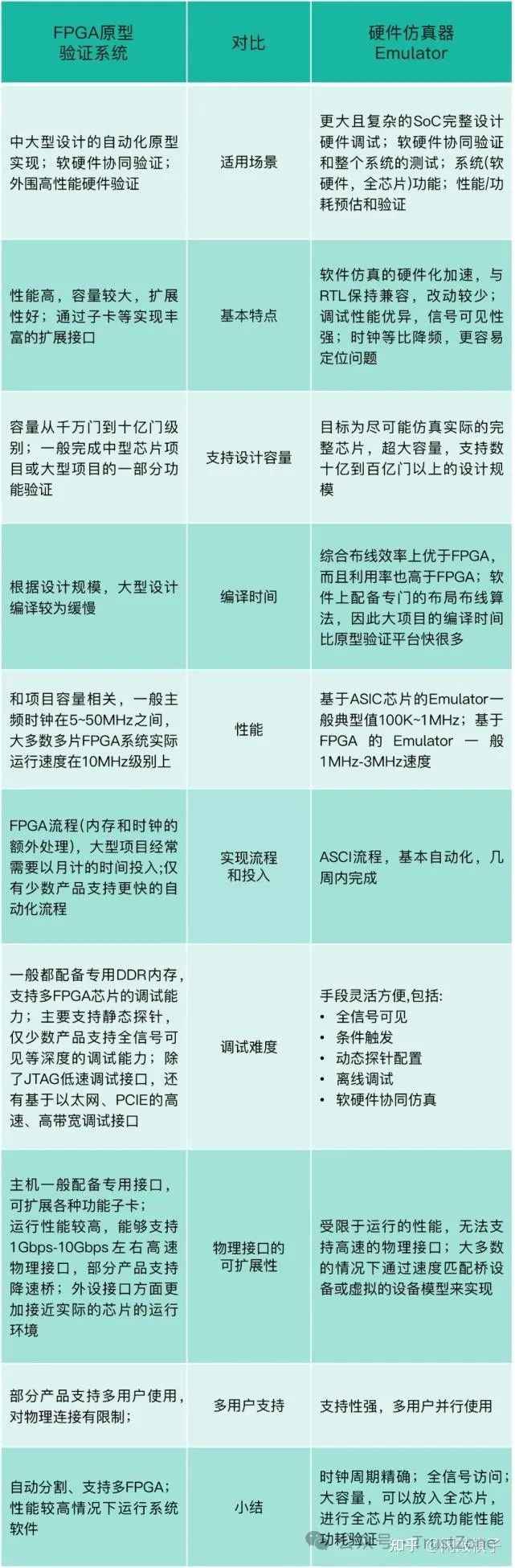

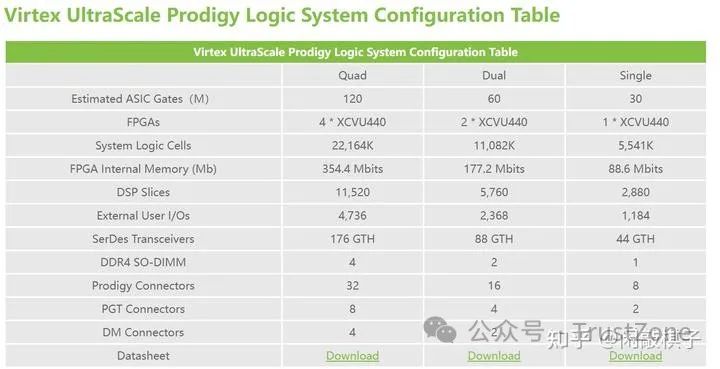

大家在网上看到原型验证岗位的时候,一般前面都会带FPGA关键字,好像原型只有FPGA验证平台一样,事实上,在一些大型公司里面,FPGA只是原型验证平台之一。

原型还有一个重要的验证平台是Emulation,以及某些公司会有功能级别的底软开发平台,比如Qemu/fastmodel等,这里我会简要的对FPGA/Emulation进行一些简单的对比:

总结起来:

总结起来:

PXP上更多的进行全系统的压力验证,性能验证,功耗验证以及FPGA上的问题复现定位;

比如现在的公司,没有这个东西,只能买板卡,自己制造平台。

综合来看,绝大部分的公司最后其实还是会选择 Synopsy HAPS-100,因为项目进度往往是第一考虑的原因,否则很多时候,都在定位平台的问题,为平台买单,当然有实力的公司也会自研,基本上成本只要HAPS的1/5;

Emulation的价格更是死贵死贵的(Cadence 1cluster的价格每个月100-150万美金左右),所以在很多时候,需要24小时都安排相关的测试任务;

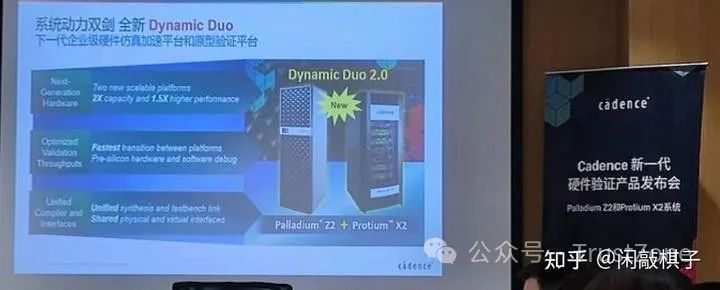

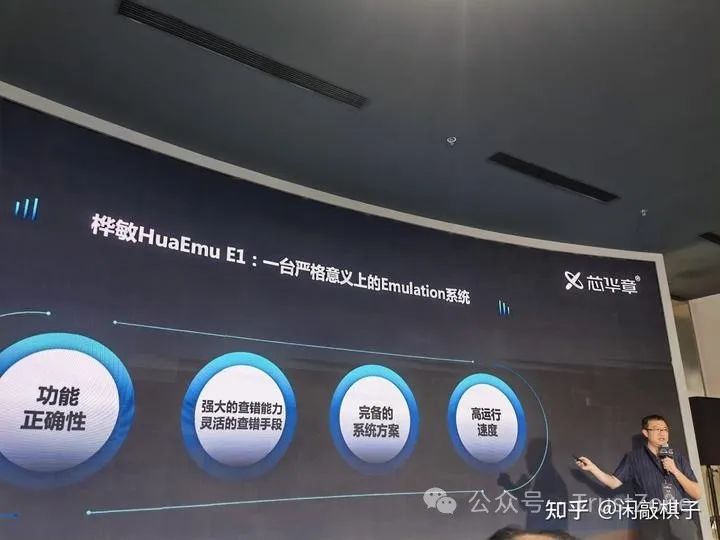

业界目前比较常见的几个Emulation平台:

上图,介绍了Palladium Z2以及Palladium X2,X2更像一个大型的FPGA,可以拥有更高的频率(5M~15MHZ),但是又能支持同比降频,也能类似Z2测试性能,但是定位问题起来略微不太方便,更适合做整体的原型业务的部署测试;

Palladium 在很多企业用的比较广泛,据笔者所知,华为、平头哥、中兴都是用的Palladium 平台;

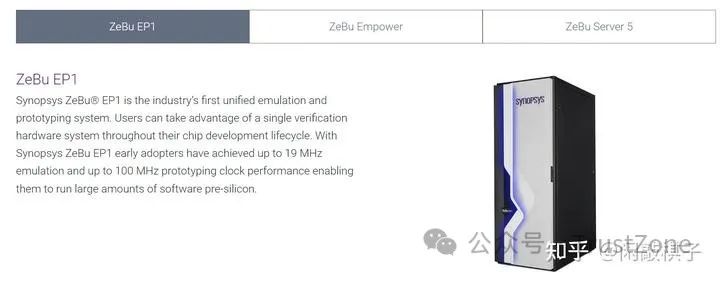

ZeBu更像一个大型的FPGA池化阵列,有点像Palladium X2,性能比Palladium 略高,但是定位问题跟FPGA一样并不太方便,笔者的公司曾经试用过zebu2,但是效果一言难尽,在稳定业务的性能输出上,因为速度问题,比较有优势 ,但是出现问题定位的时候,就极其不太方便;

但是Zebu有一个比较大的优势,对于自家的很多IP的model兼容性非常好,可以在design上面轻松接入非常丰富的S家的IP,对整个SOC的验证是相对方便的;

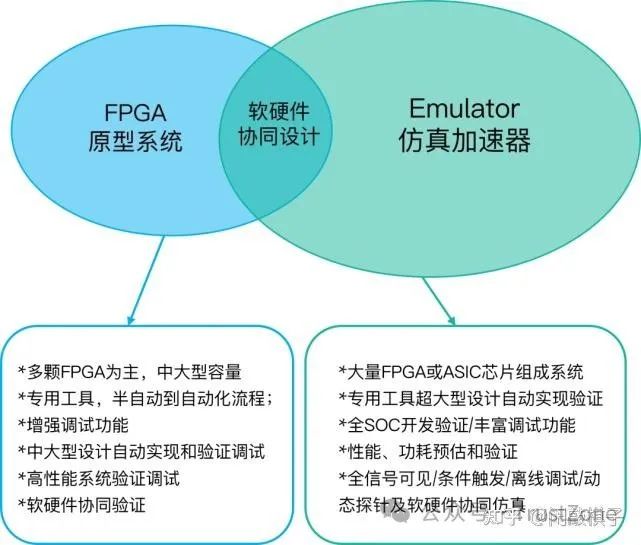

总体来说,Emulation+FPGA 配合上原型的验证特点,是构建原型完备的验证方法学的基础,当然在不同的公司对于Emulation+FPGA 的开发程度不一样,

比如笔者所在的公司会针对原型验证的完备性,是必须在相关工具、方法、脚本处理上做非常多的工作,工欲善其事必先利其器,以达到验证闭环、加快验证效率的目的。