随着摩尔定律的逐步放缓,芯片制造商正在寻找其他方法来提高处理器的性能,包括架构创新、更大的芯片尺寸、多芯片设计,甚至晶圆级芯片,比如Cerebras的WSE系列AI芯片。

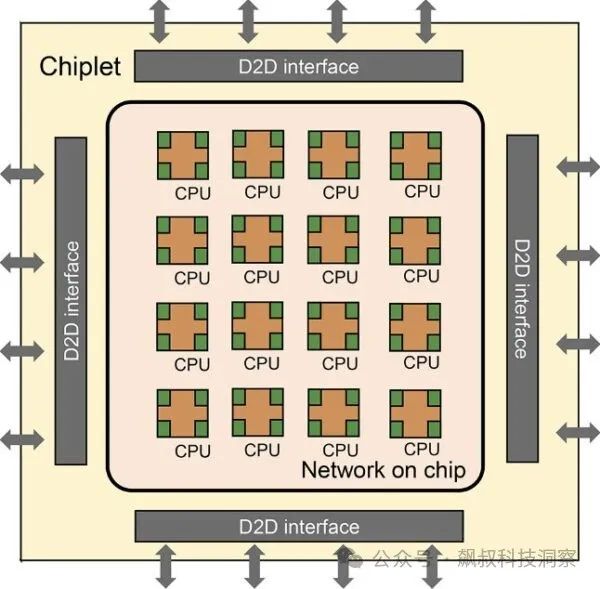

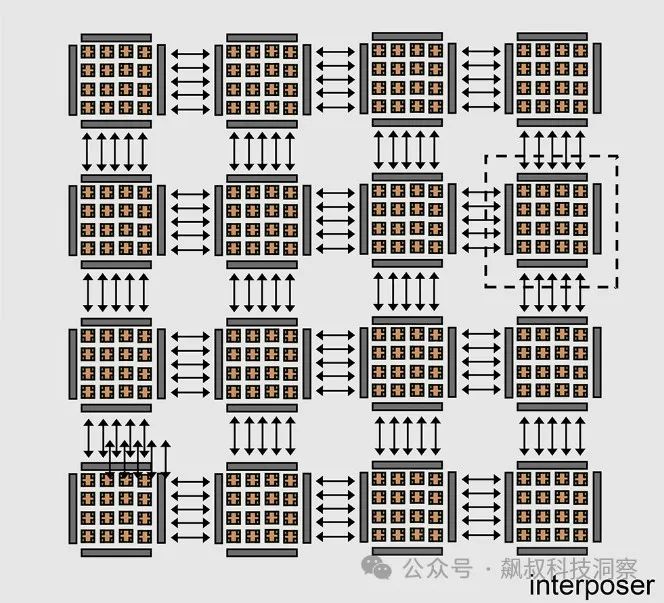

近日,中国科学院计算技术研究所的研究人员在《基础研究》杂志上发表了一篇论文,讨论了光刻和小芯片(Chiplet)的局限性,并提出了一种称之为“大芯片”的架构。论文介绍了一种先进的256核多芯片计算复合体,名为“Zhejiang”。中国科学院计算技术研究所还计划将这款基于RISC-V架构的256核多芯片扩展到1600核,以创造整个晶圆大小的芯片,作为一个计算设备。据悉,“Zhejiang”由16个小芯片组成,每个小芯片有16个RISC-V内核。研究人员表示,该设计能够在单个分立器件中扩展至100个小芯片,我们过去称之为插槽,但对我们来说听起来更像是系统板。目前尚不清楚这100个小芯片将如何配置,也不清楚这些小芯片将实现什么样的内存架构(阵列中将有1600个内核)。以下是Zhejiang RISC-V小芯片的框图:以下是如何使用中介层将16个小芯片连接在一起形成具有共享内存的256核计算复合体,从而实现芯片间(D2D)互连:据中科院研究人员介绍,“Zhejiang”将使用22nm工艺制造。中科院研究人员表示,大芯片计算引擎将由超过1万亿个晶体管组成,占据数千平方毫米的总面积,采用小芯片封装或计算和存储块的晶圆级集成。对于百亿亿级HPC和AI工作负载,报道认为中科院很可能正在考虑HBM堆叠DRAM或其他一些替代双泵浦主内存,例如英特尔和SK海力士开发的MCR内存。RISC-V内核可能会有大量本地SRAM进行计算,这可能会消除对HBM内存的需求,并允许使用MCR双泵浦技术加速DDR5内存。飙叔感谢您花时间关注与分享,感谢在我的人生道路中多了这么多志同道合的朋友,一起关注国产光刻机、国产芯片、国产半导体艰难突破之路;一起分享华为海思、华为鸿蒙及华为手机等华为产业为代表的中国ICT产业崛起的点点滴滴;从此生活变得不再孤单,不再无聊!

|

勾搭飙叔,请扫码

|