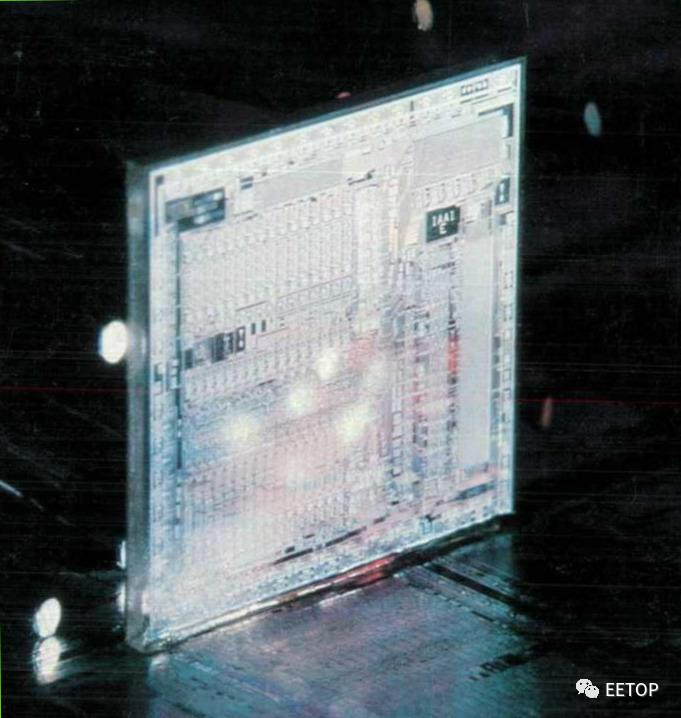

调查得出的结论是,该芯片不是硅基板,而是形成在蓝宝石基底上,顶部有硅和金属布线。因此,芯片是透明的,正如您可以从下图中通过芯片看到的金色“X”看到的那样。

它的功能比您想象的要平凡得多:它是软盘控制器上的支持组件。

它位于 HP 接口总线 (HP-IB) 和Z80 处理器之间的一个不起眼的软盘驱动器控制器 PCB 中。

根据调查,“它拥有处理总线协议并缓冲接口总线和设备微处理器之间的数据” Shirriff 解释说,这款芯片当时曾用于多种 HP 产品中。

在维修8英寸HP软盘驱动器时,我们发现问题出在接口芯片损坏上。由于芯片坏了,我把它拆开并拍照。该芯片非常不寻常:该芯片不是硅基板,而是形成在蓝宝石基底上,顶部有硅和金属布线。因此,芯片是透明的,正如您可以从下图中通过芯片看到的金色“X”看到的那样。

通过检查显微镜看到的 PHI 芯片。单击此图像(或任何其他图像)以获得更大的版本。

该芯片是 1977 年定制的 HP 芯片,提供 HP 接口总线 (HP-IB) 和软盘驱动器控制器中的 Z80 处理器之间的接口。HP 将该接口总线设计为一种低成本总线,用于连接测试设备、计算机和外围设备。该芯片名为 PHI(处理器到 HP-IB接口),用于多种 HP 产品中。它处理接口总线和设备微处理器之间的总线协议和缓冲数据。1 在本文中,我将深入了解该“蓝宝石硅”芯片,检查其金属栅极 CMOS 电路,并解释其工作原理。

蓝宝石衬底硅芯片

蓝宝石硅芯片(Silicon-on-sapphire,SOS)可能听起来有些未来主义,但 Shirriff 的博客强调,这种方式制造的 IC 自 1963 年或更早以来就已存在。蓝宝石硅 IC 的一个著名示例是研究木星及其卫星的伽利略太空探测器上使用的 RCA 1802 处理器。

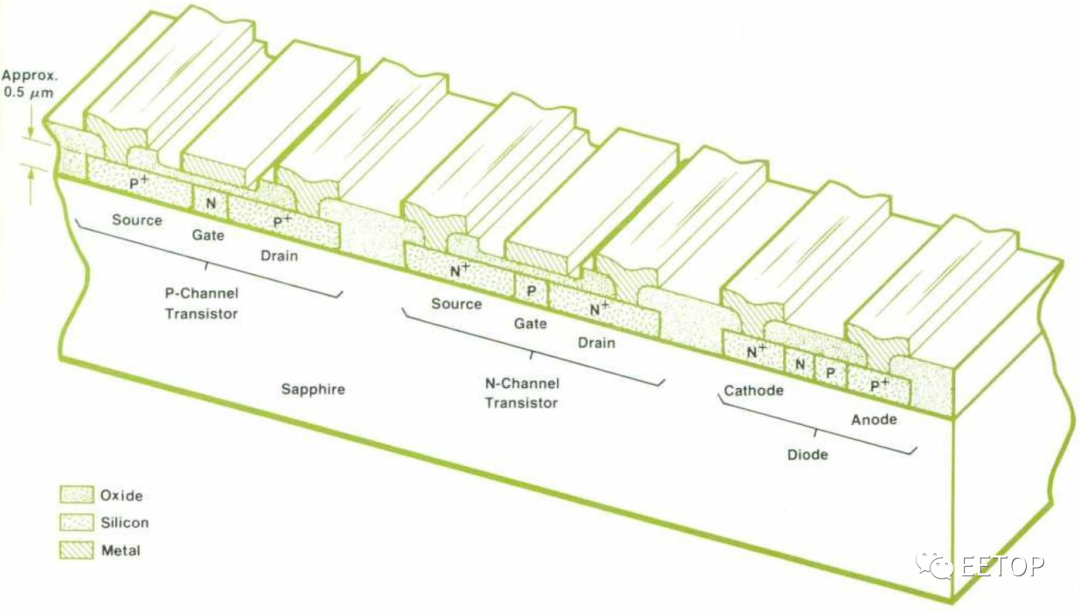

大多数集成电路形成在硅晶片上。另一方面,蓝宝石基地的硅芯片则从蓝宝石衬底开始。在蓝宝石基板上构建一层薄薄的硅以形成电路。硅是N型的,并且在需要时通过离子注入将其转化为P型。在顶部创建金属布线层,形成布线以及金属栅极晶体管。下图显示了电路的横截面。

HP Journal的横截面,1977 年 4 月

蓝宝石衬底硅芯片的重要一点是硅区域彼此分离。由于蓝宝石基板是绝缘体,因此与常规集成电路不同,晶体管是完全隔离的。这减少了晶体管之间的电容,从而提高了性能。绝缘还可以防止杂散电流,防止闩锁和辐射。

HP MC2 裸片,1977年

蓝宝石衬底硅芯片的历史可以追溯到 1963 年Autonetics 的研究,这是一家创新但现已被遗忘的航空电子公司,该公司为民兵洲际弹道导弹等生产制导计算机。RCA 在 20 世纪 60 年代和 1970 年代开发了蓝宝石硅集成电路,例如CDP1821蓝宝石硅 1K RAM。HP 从 1977 年开始在多种芯片中使用蓝宝石硅,例如MC2 Micro-CPU芯片。惠普还在HP 3000 Amigo (1978)中的三芯片 CPU 中使用了 SOS ,但该系统在商业上失败了。蓝宝石硅的普及在 20 世纪 80 年代初达到顶峰,HP 转向用于HP-41C 等计算器的体硅集成电路。蓝宝石硅仍然用于各种产品,例如 LED 和 RF 应用,但现在主要是一种利基技术。

PHI 芯片内部

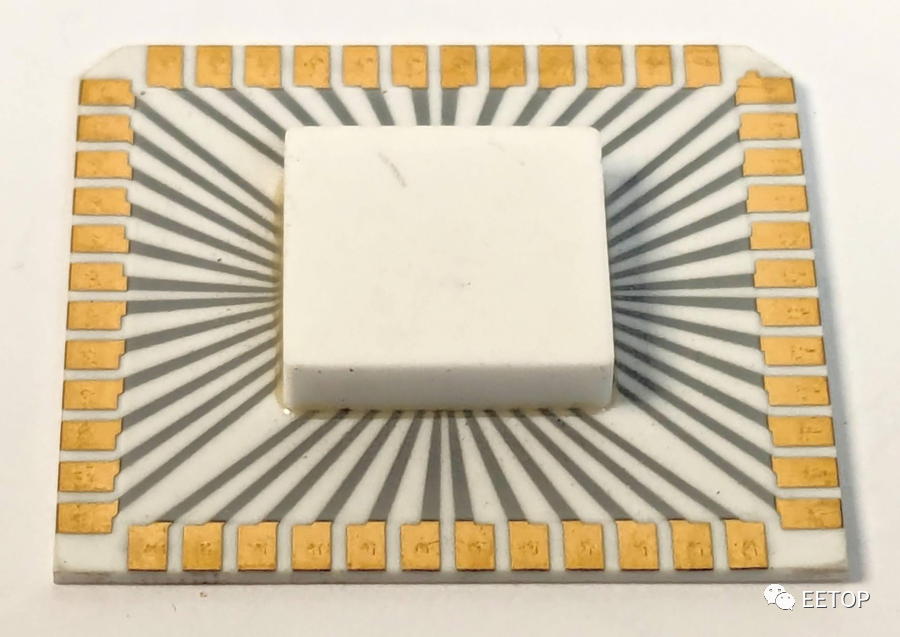

HP 对 PHI 芯片使用了一种不寻常的封装。该芯片安装在陶瓷基板上,并由陶瓷盖保护。该封装有 48 个压入插座的金手指。芯片通过两个金属弹簧夹固定在插座中。

PHI 芯片的封装

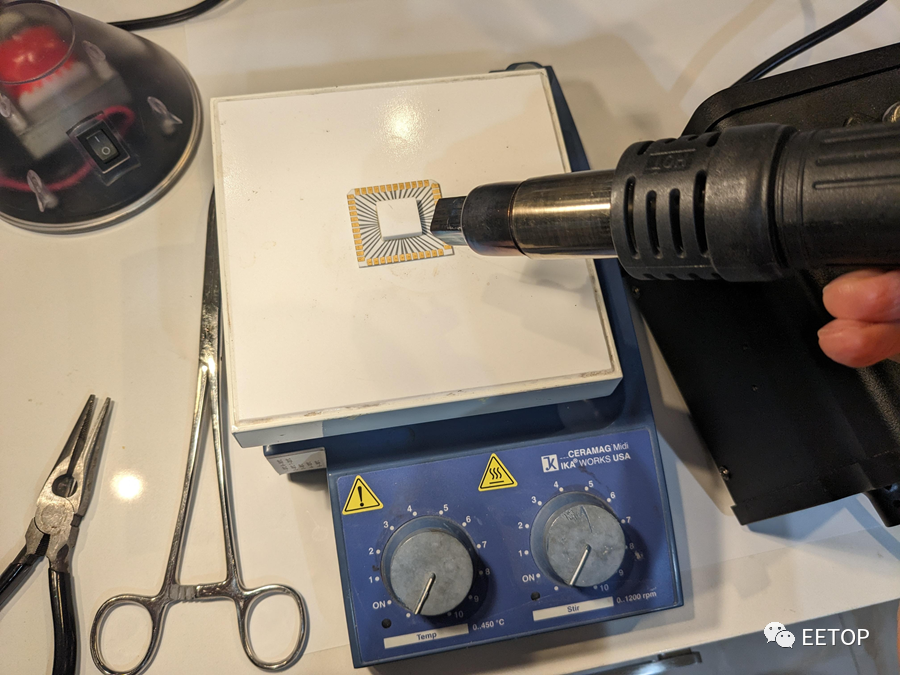

拆开芯片很简单,但比我预期的更戏剧化。芯片的盖子上贴有粘合剂,可以通过加热软化。热空气不够,所以我们使用了电热板。拆解过程中,使用一把X-Acto 刀戳它来测试粘合剂,导致盖子突然飞离,发出一声响亮的“砰”的一声,刀片飞到空中。我很高兴戴着安全眼镜。

用加热板和热空气对芯片进行脱盖。

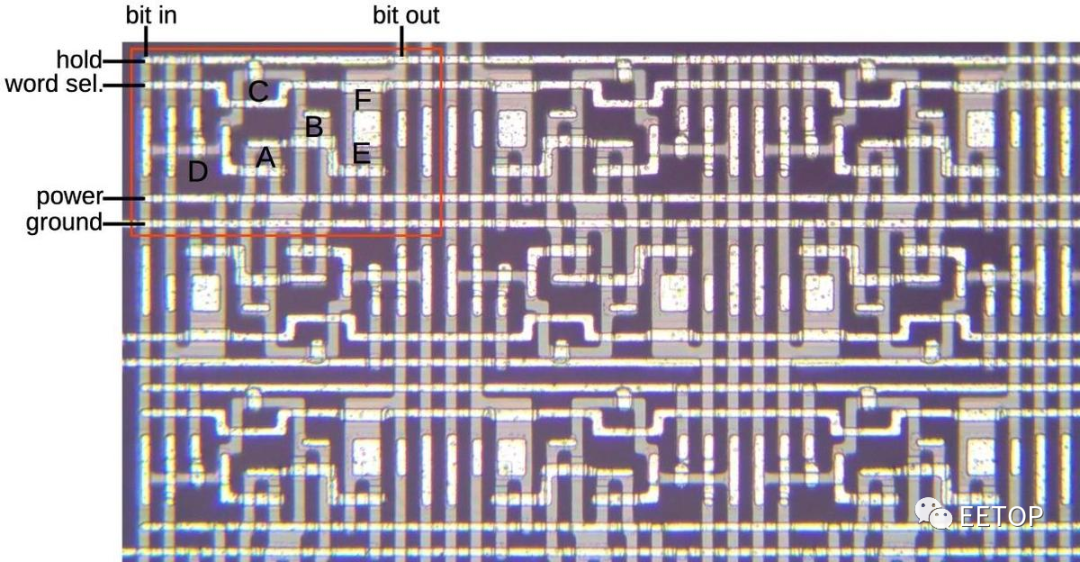

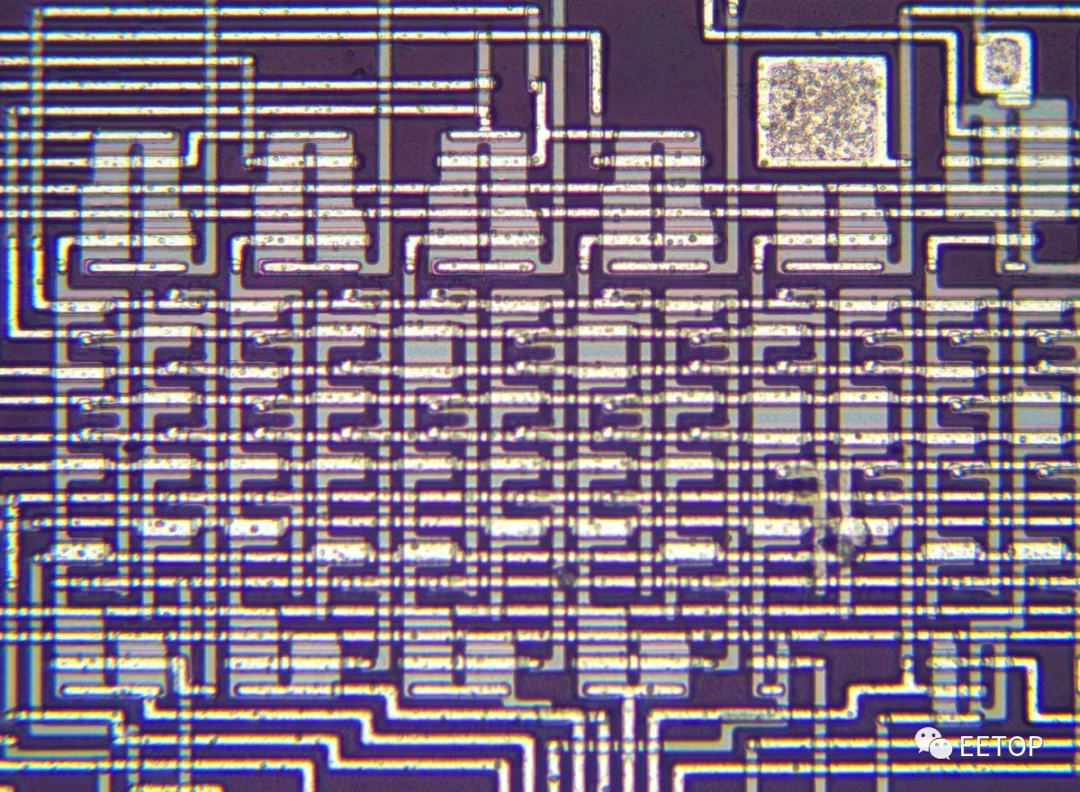

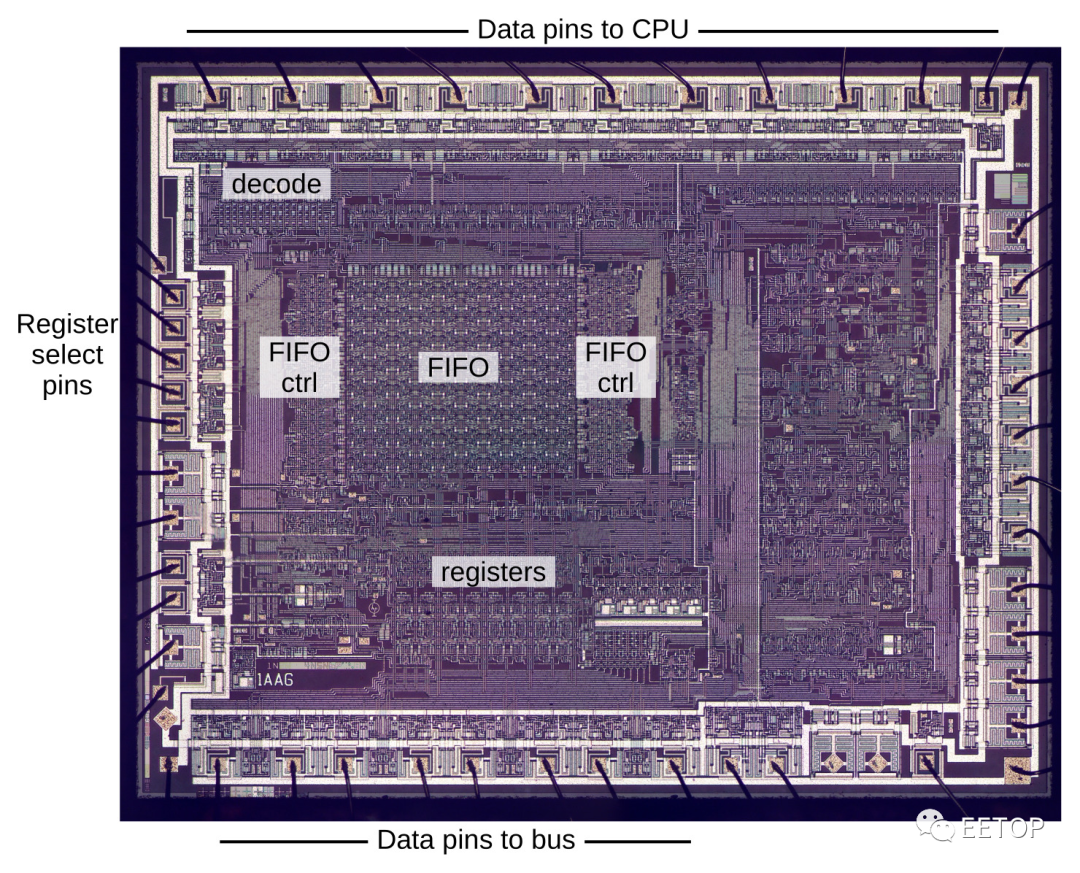

打开芯片后,我创建了下面的高分辨率芯片照片。金属层清晰可见,呈白色线条,而硅呈灰色,蓝宝石呈紫色。在芯片边缘周围,键合线将芯片的 48 个外部连接连接到芯片。在中心偏左上方,一个大的规则矩形电路块提供 160 位存储:这是两个 8 字 FIFO 缓冲区,在接口总线和连接的微处理器之间传递 10 位字。边缘周围的厚金属迹线为芯片提供+12伏、+5伏和接地电压。

PHI 芯片的裸片显微照片

逻辑门

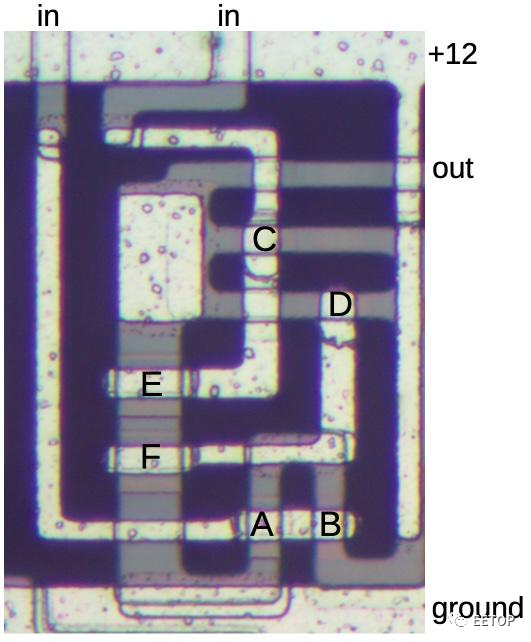

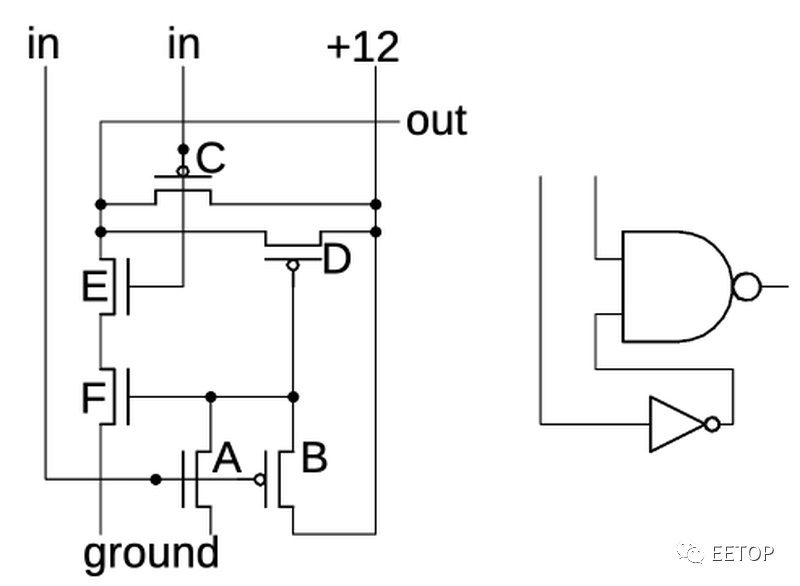

由于蓝宝石硅实现以及金属栅极晶体管的使用,该芯片上的电路具有不寻常的外观,但基本上电路是标准 CMOS。下图显示了一个实现反相器和 NAND 门的块。蓝宝石基板呈深紫色。最重要的是,粗灰色线是硅。顶部的白色金属连接晶体管。当金属穿过硅时(用字母表示),也可以形成晶体管的栅极。不方便的是,接触硅的金属、跨越硅的金属以及形成晶体管的金属在该芯片中都显得非常相似。这使得确定接线更加困难。

该图显示了芯片上的反相器和 NAND 门。

下面的示意图显示了门的实现方式,与上面的照片相匹配。顶部和底部的金属线分别提供电源轨和接地轨。反相器由NMOS晶体管A和PMOS晶体管B组成;输出进入晶体管 D 和 F。NAND 门由 NMOS 晶体管 E 和 F 以及 PMOS 晶体管 C 和 D 组成。NAND 门的组件在金属方块处连接,然后输出通过硅离开在右侧。请注意,只有当一个信号位于硅层中且一个信号位于金属层中时,信号才能交叉。由于只有两层布线,PHI 芯片中的信号必须经常蜿蜒以避免交叉,浪费了大量空间。(这种布线比 20 世纪 70 年代也具有多晶硅层的典型芯片受到更多限制,总共提供了三个布线层。)

该示意图显示了反相器和 NAND 门的实现方式

PHI 芯片有两个先进先出缓冲器 (FIFO),占芯片的很大一部分。每个 FIFO 保存 8 个字,每字 10 位,其中一个 FIFO 保存从总线读取的数据,另一个 FIFO 保存向总线写入的数据。这些缓冲器有助于使总线速度与微处理器速度相匹配,确保数据传输尽可能快。

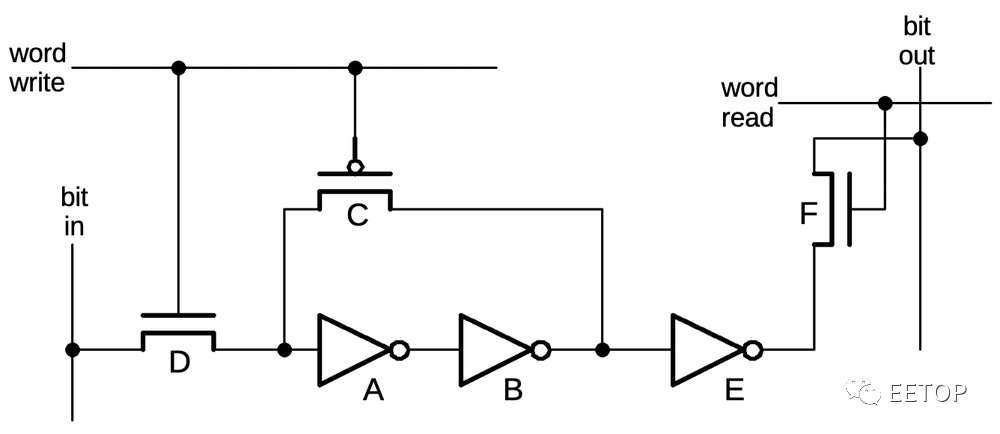

FIFO 的每一位基本上都是一个静态 RAM 单元,如下图所示。反相器 A 和 B 形成一个环路,用于保持一个比特。通过晶体管 C 提供反馈,使反相器环路保持稳定。要写入一个字,需要通过垂直位输入线输入 10 位。水平字写入信号被激活,以选择要更新的字。这将禁用晶体管 C 并开启晶体管 D,使新比特流入反相器环路。要读取一个字,水平字读取线会被激活,并打开传递晶体管 F。这样,单元中的位就会流入垂直位输出线,并由反相器 E 缓冲。两个FIFO具有单独的行,因此可以独立读取和写入。

FIFO 的一个单元

下图显示了裸片上出现的 9 个 FIFO 单元。红色框表示一个单元,其组件已标记为与原理图相匹配。单元在垂直和水平方向上镜像以增加布局密度。

裸片上的九个 FIFO 单元

地址译码器

另一个有趣的电路是根据地址线选择特定寄存器的译码器。PHI 芯片有八个寄存器,由三个地址线选择。译码器获取地址线并生成 16 条控制线(或多或少),一根用于从每个寄存器读取,一根用于写入每个寄存器。

地址译码器的照片

译码器具有规则的矩阵结构,可有效实现。行线是成对的,每个地址位输入及其补码都有一行。每一列对应一个输出,晶体管的排列使得当给定适当的输入时该列将被激活。顶部和底部是逆变器。它们锁存传入的地址位、生成补码并缓冲输出。

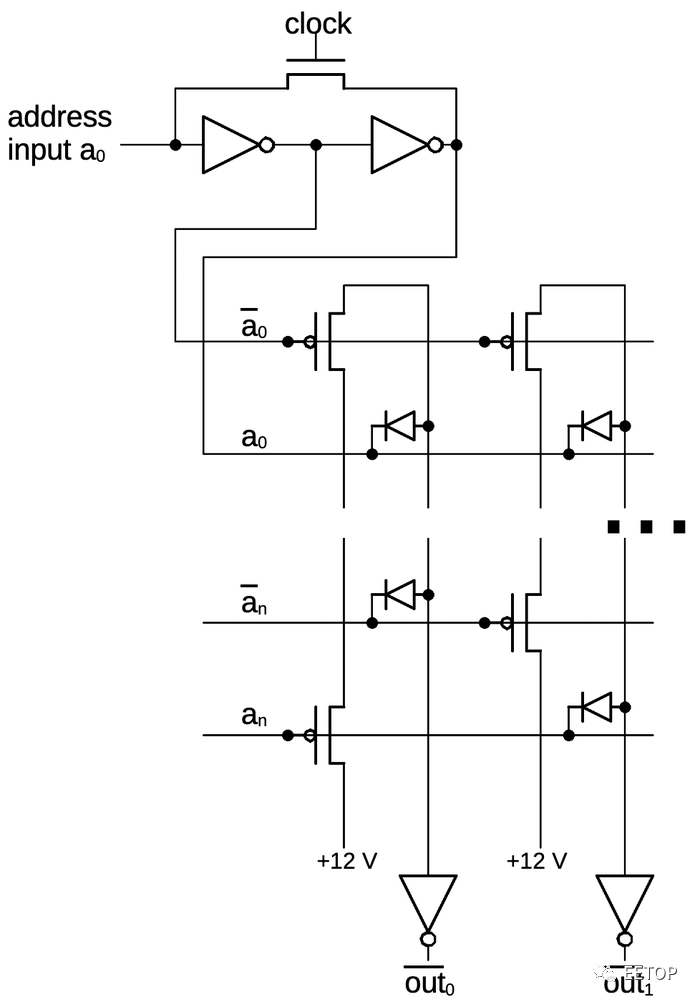

解码器示意图

上图显示了译码器的工作原理。(我将其简化为两个输入和两个输出。)在顶部,地址线穿过由两个反相器和一个传输晶体管组成的锁存器。地址线及其补码构成两条行线;其他行线类似。每列的一条行线上有一个晶体管,另一条行线上有一个二极管,用于选择该列的地址。例如,假设0为 1,n为 0。这与第一列匹配,因为晶体管线为低电平,二极管线为高电平。该列中的 PMOS 晶体管将全部导通,从而将反相器的输入拉高。然而,如果任何输入“错误”,相应的晶体管将关闭,从而阻断 +12 伏电压。此外,输出将通过相应的二极管拉低。因此,只有当所有输入匹配时,每列才会被拉高,否则将被拉低。每列输出控制芯片的一个寄存器,允许访问该寄存器。

HP-IB总线和PHI芯片

惠普接口总线 (HP-IB) 于 20 世纪 70 年代初设计,作为一种低成本总线,用于连接各种设备,包括仪器系统(例如数字电压表或频率计数器)、存储器和计算机。该总线于 1975 年成为 IEEE 标准,称为IEEE-488 总线。2 总线是 8 位并行,设备之间通过握手,因此慢速设备可以控制速度。

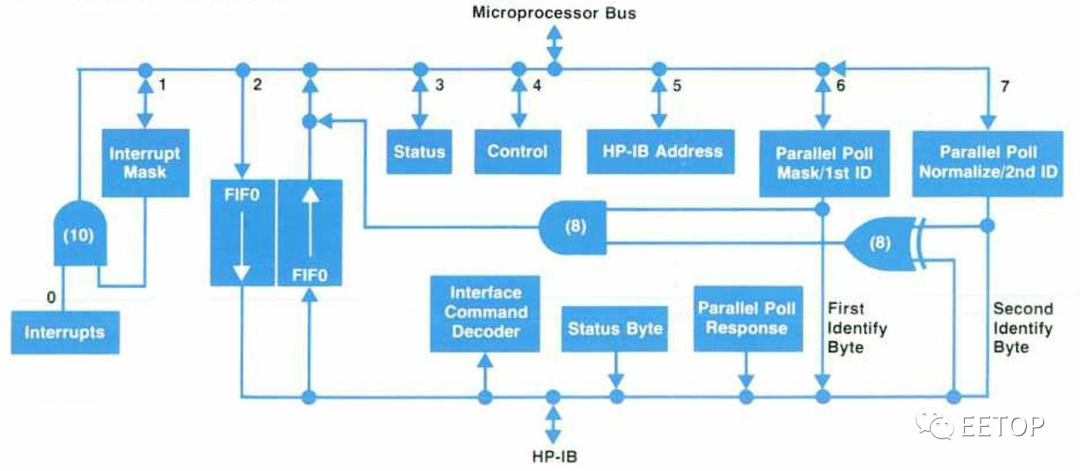

1977年,HP开发了一款芯片,称为PHI(Processor to HP-IB Interface),用于实现总线协议并提供微处理器接口。该芯片不仅简化了总线控制器的构造,而且确保设备一致地执行协议。下面的框图显示了 PHI 芯片的组件。它不是一个特别复杂的芯片,但也不是微不足道的。我估计它有几千个晶体管。

框图来自HP Journal,1989 年 7 月

下面的芯片照片显示了 PHI 芯片的一些功能块。微处理器连接到顶部引脚,而接口总线连接到下部引脚。

PHI 芯片带有一些标记的功能块

结论

PHI 芯片顶部,部件号为 1AA6-6004。我不确定顶部的椭圆形印记是什么,也许是一只乌龟?

PHI 芯片作为“未来技术”的一个例子很有趣,但并没有完全成功。惠普在蓝宝石硅芯片上投入了大量精力,期望这将成为一项重要的技术:密集、快速和低功耗。然而,事实证明,普通硅芯片是获胜的技术,而蓝宝石硅芯片则被降级到利基市场。

将惠普的蓝宝石硅芯片与当时的普通硅芯片进行比较,可以看出一些优点和缺点。HP 的 MC 2 16位处理器(1977 年)采用蓝宝石硅技术,拥有10,000 个晶体管,运行频率为 8 兆赫,功耗为 350 毫瓦。相比之下,Intel 8086 (1978) 也是一款 16 位处理器,但在常规硅上实现并使用 NMOS 而不是 CMOS。8086 有29,000 个晶体管,运行频率为 5 兆赫(最初),功耗高达 2.5 瓦。芯片的尺寸几乎相同:惠普处理器为34 mm 2 ,英特尔处理器为33 mm 2。这说明 CMOS 的功耗比 NMOS 低得多,这也是 CMOS 现在成为主导技术的原因之一。对于其他因素,蓝宝石硅具有一定的速度优势,但密度不那么高。蓝宝石硅的主要问题是产量低且成本高。硅和蓝宝石之间的晶体不相容性使得制造变得困难;HP 的良率仅为 9%,这意味着 91% 的Die出现故障。

PHI 芯片的时期也很有趣,因为接口总线正在从简单的总线过渡到具有复杂协议的高性能总线。早期的总线可以用简单的集成电路来实现,但随着协议变得更加复杂,定制接口芯片变得必要。(MOS 6522 多功能接口适配器芯片(1977 年)是另一个例子,在 20 世纪 80 年代的许多家用计算机中使用。)但这些接口仍然足够简单,接口芯片不需要微控制器,而是使用简单的状态机。

PHI 芯片上的 HP 徽标

来源:EETOP编译自righto