在邮寄易碎物品时,使用合适的包装材料尤为重要,因为它确保包裹能够完好无损地到达目的地。泡沫塑料、气泡膜和坚固的盒子都可以有效地保护包裹内的物品。同样地,封装是半导体制造工艺的关键环节,可以保护芯片免受物理性或化学性损坏。然而,半导体封装的作用并不止于此。

本文是半导体后端(Back-End)工艺系列的第二篇文章,我们将详述封装技术的不同等级、作用和演变过程。

01

半导体封装工艺的四个等级

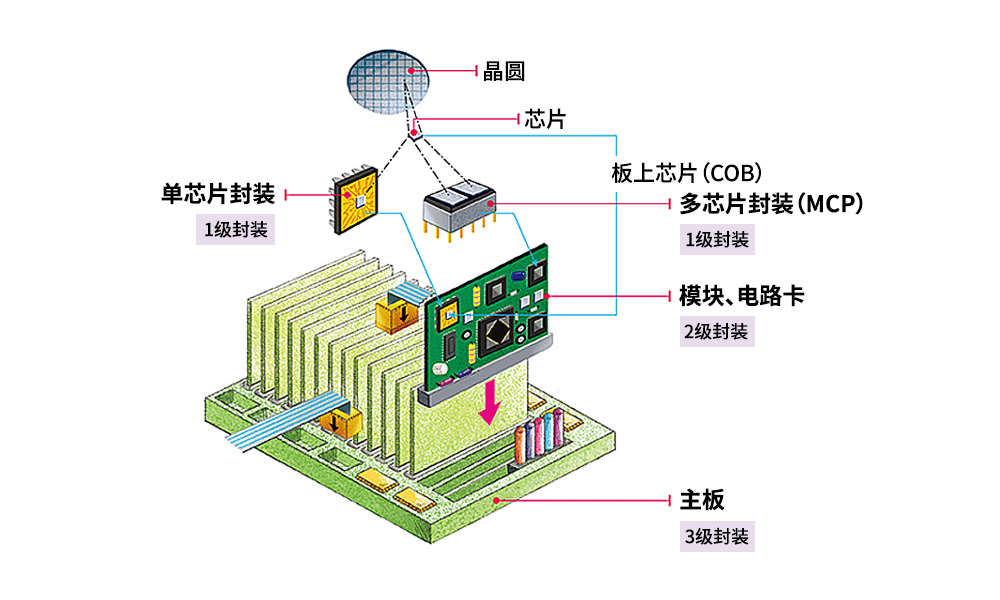

电子封装技术与器件的硬件结构有关。这些硬件结构包括有源元件1(如半导体)和无源元件2(如电阻器和电容器3)。因此,电子封装技术涵盖的范围较广,可分为0级封装到3级封装等四个不同等级。图1展示了半导体封装工艺的整个流程。首先是0级封装,负责将晶圆切割出来;其次是1级封装,本质上是芯片级封装;接着是2级封装,负责将芯片安装到模块或电路卡上;最后是3级封装,将附带芯片和模块的电路卡安装到系统板上。从广义上讲,整个工艺通常被称为“封装”或“装配”。然而,在半导体行业,半导体封装一般仅涉及晶圆切割和芯片级封装工艺。

1有源元件:一种需要外部电源才能实现其特定功能的器件,就像半导体存储器或逻辑半导体。

2无源元件:一种不具备放大或转换电能等主动功能的器件。

3电容器(Capacitor):一种储存电荷并提供电容量的元件。

▲图1:半导体的封装等级(信息来源:“电子封装原理 (Principle of Electronic Packaging)”,第5页)

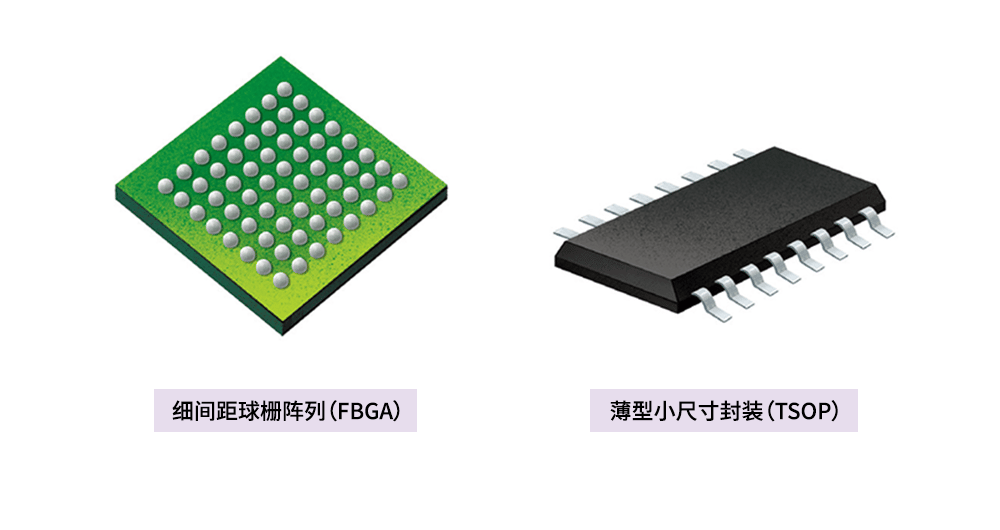

封装通常采用细间距球栅阵列(FBGA)或薄型小尺寸封装(TSOP)的形式,如图2所示。FBGA封装中的锡4球和TSOP封装中的引线5分别充当引脚,使封装的芯片能够与外部组件之间实现电气和机械连接。

4锡(Solder):一种低熔点金属,支持电气和机械键合。

5引线(Lead):从电路或元件终端向外引出的导线,用于连接至电路板。

▲图2:半导体封装示例(来源:ⓒ HANOL出版社)

02

半导体封装的作用

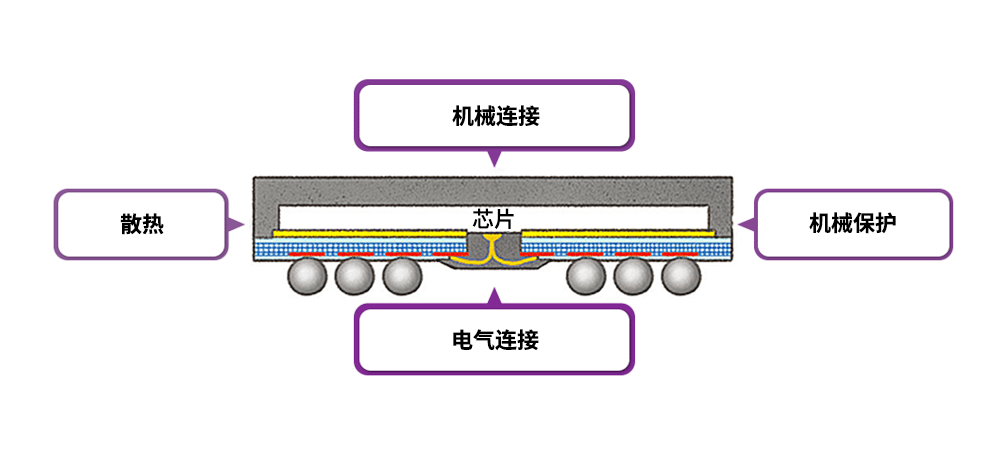

图3展示了半导体封装的四个主要作用,包括机械保护、电气连接、机械连接和散热。其中,半导体封装的主要作用是通过将芯片和器件密封在环氧树脂模塑料(EMC)等封装材料中,保护它们免受物理性和化学性损坏。尽管半导体芯片由数百个晶圆工艺制成,用于实现各种功能,但主要材质是硅。硅像玻璃一样,非常易碎。而通过众多晶圆工艺形成的结构同样容易受到物理性和化学性损坏。因此,封装材料对于保护芯片至关重要。

▲图3:半导体封装的作用(来源:ⓒ HANOL出版社)

此外,半导体封装可以实现从芯片到系统之间的电气和机械连接。封装通过芯片和系统之间的电气连接来为芯片供电,同时为芯片提供信号的输入和输出通路。在机械连接方面,需将芯片可靠地连接至系统,以确保使用时芯片和系统之间连接良好。

同时,封装需将半导体芯片和器件产生的热量迅速散发出去。在半导体产品工作过程中,电流通过电阻时会产生热量。如图3所示,半导体封装将芯片完全地包裹了起来。如果半导体封装无法有效散热,则芯片可能会过热,导致内部晶体管升温过快而无法工作。因此,对于半导体封装技术而言,有效散热至关重要。随着半导体产品的速度日益加快,功能日益增多,封装的冷却功能也变得越来越重要。

03

半导体封装的发展趋势

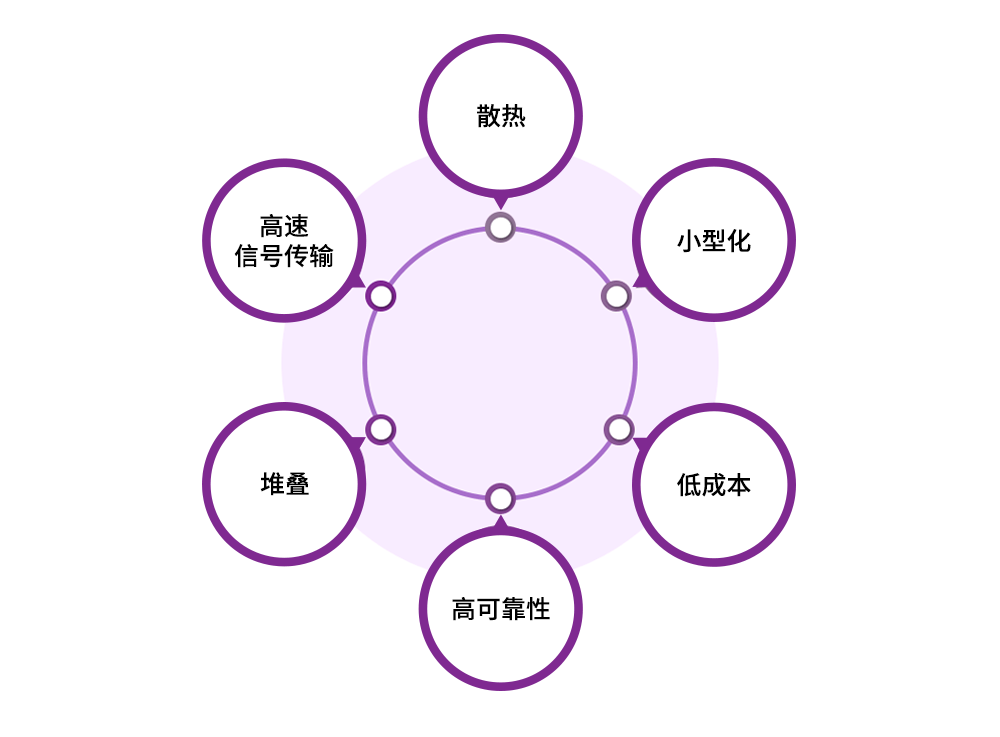

图4概述了近年来半导体封装技术的六大发展趋势。分析这些趋势有助于我们了解封装技术如何不断演变并发挥作用。

首先,由于散热已经成为封装工艺的一个重要因素,因此人们开发出了热传导6性能较好的材料和可有效散热的封装结构。

6热传导:指在不涉及物质转移的情况下,热量从温度较高的部位传递到相邻温度较低部位的过程。

可支持高速电信号传输的封装技术也成为了一种重要发展趋势,因为封装会限制半导体产品的速度。例如,将一个速度达每秒20千兆 (Gbps) 的半导体芯片或器件连接至仅支持每秒2千兆(Gbps) 的半导体封装装置时,系统感知到的半导体速度将为每秒2千兆 (Gbps)。由于连接至系统的电气通路是在封装中创建,因此无论芯片的速度有多快,半导体产品的速度都会极大地受到封装的影响。这意味着,在提高芯片速度的同时,还需要提升半导体封装技术,从而提高传输速度。这尤其适用于人工智能技术和5G无线通信技术。鉴于此,倒片封装7和硅通孔(TSV)8等封装技术应运而生,为高速电信号传输提供支持。

7倒片封装(Flip Chip):一种通过将凸点朝下安装于基板上,将芯片与基板连接的互连技术。

8硅通孔(TSV):一种可完全穿过硅裸片或晶圆实现硅片堆叠的垂直互连通道。

▲图4:半导体封装技术的发展趋势(来源:ⓒ HANOL出版社)

另一个发展趋势是三维半导体堆叠技术,它促进了半导体封装领域的变革性发展。过去,一个封装外壳内仅包含一个芯片,而如今可采用多芯片封装(MCP)和系统级封装(SiP)9等技术,在一个封装外壳内堆叠多个芯片。

9系统级封装(SiP):一种将多个器件整合在单个封装体内构成一个系统的封装技术。

封装技术还呈现半导体器件小型化的发展趋势,即缩小产品尺寸。随着半导体产品逐渐被用于移动甚至可穿戴产品,小型化成为客户的一项重要需求。为了满足这一需求,许多旨在减小封装尺寸的技术随之而诞生。

此外,半导体产品正越来越多地应用于各种环境中。除了健身房、办公室或住宅等日常环境,热带雨林、极地地区、深海甚至太空等环境中也能见到半导体的身影。由于封装的基本作用是保护半导体芯片和器件,因此需要开发高度可靠的封装技术,确保半导体产品在此类极端环境下也能正常工作。

最后,由于半导体封装是最终产品,封装技术不仅要实现预期功能,还要具有较低的制造成本。

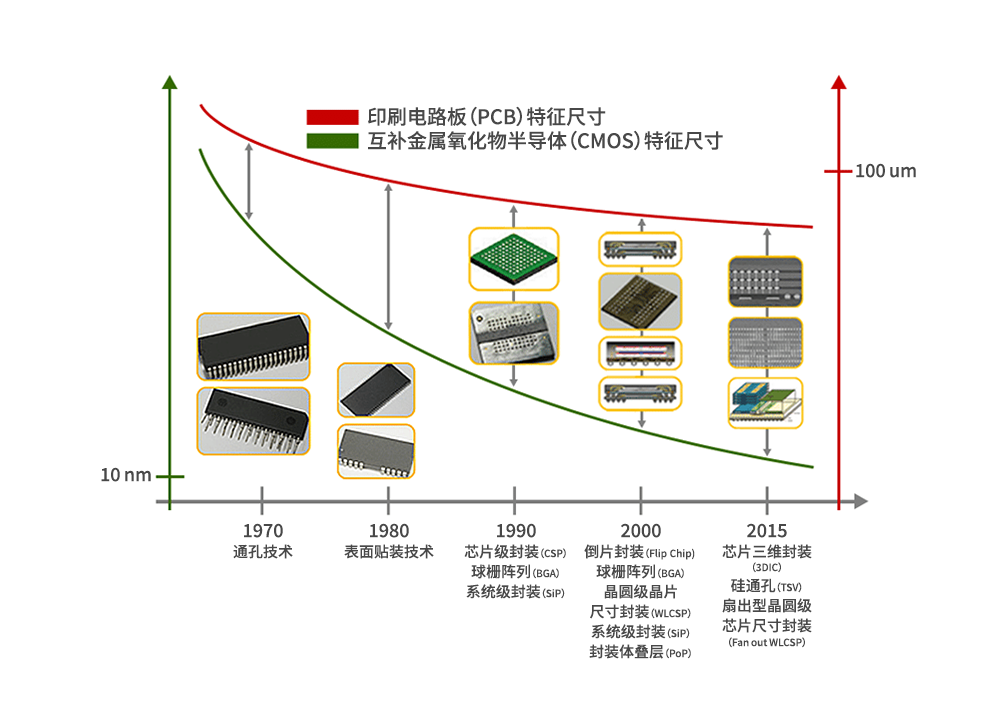

除了上述旨在推进封装技术特定作用的发展趋势,促使封装技术发生演变的另一个驱动力是整个半导体行业的发展。在图5中,红色线条表示自20世纪70年代以来装配过程中安装的印刷电路板(PCB)10的特征尺寸变化情况,绿色线条则表示晶圆上CMOS晶体管的特征尺寸变化情况。缩小特征尺寸有助在印刷电路板和晶圆上绘制更小的图案。

10印刷电路板(PCB):由电路组成的半导体板,且元件焊接在电路板表面。这些电路板通常用于电子设备中。

▲图5:随着时间的推移,晶圆和 印刷电路板特征尺寸的变化情况(来源:ⓒ HANOL出版社)

20世纪70年代,印刷电路板与晶圆的特征尺寸差异较小。如今,晶圆正在步入量产阶段,同时特征尺寸小于10纳米(nm)的CMOS晶体管也在开发中,而印刷电路板的特征尺寸依然在100微米(um)的范围。两者特征尺寸的差距在过去几十年里显著扩大。

由于主板以面板的形式制造,且受到成本节约策略等因素的影响,印刷电路板的特征尺寸变化不大。然而,随着光刻技术的进步,CMOS晶体管的特征尺寸大幅缩小,这使得CMOS晶体管的尺寸与印刷电路板的尺寸差距逐渐拉大。但问题在于,半导体封装技术需要对从晶圆上切割下来的芯片进行个性化定制,并将其安装到印刷电路板上,因此就需要弥补印刷电路板和晶圆之间的尺寸差距。过去,两者在特征尺寸上的差异并不明显,因而可以使用双列直插式封装(DIP)11或锯齿型单列式封装(ZIP)12等通孔技术,将半导体封装引线插入印刷电路板插座内。然而,随着两者特征尺寸差异不断扩大,就需要使用薄型小尺寸封装(TSOP)等表面贴装技术(SMT)13将引线固定在主板表面。随后,球栅阵列(BGA)、倒片封装、扇出型晶圆级芯片尺寸封装(WLCSP)14及硅通孔(TSV)等封装技术相继问世,以弥补晶圆和主板之间不断扩大的尺寸差异。

11双列直插式封装(DIP):一种电气连接引脚排列成两行的封装技术。

12锯齿型单列式封装(ZIP):一种引脚排列成锯齿型的封装技术,是双列直插式封装的替代技术,可用于增加安装密度。

13表面贴装技术(SMT):一种通过焊接将芯片安装到系统板表面的封装方法。

14晶圆级晶片尺寸封装(WLCSP):一种在晶圆级封装集成电路的技术,是倒片封装技术的一个变体。扇出型晶圆级芯片尺寸封装(WLCSP)的特点在于连接超出(“扇出”)芯片表面。

04

通过测试确保半导体封装的有效性

可以通过两种方法来开发半导体封装并确保其有效性。第一种方法是利用现有封装技术来创建适用于新开发半导体芯片的封装,然后对封装进行评估。第二种方法是开发一种新的半导体封装技术,将其应用于现有芯片上,并评估新封装技术的有效性。

一般来说,新芯片的开发和新封装技术的应用不会同时进行。原因在于,如果芯片和封装均未经过测试,那么一旦在封装完成后出现问题,就很难确定问题的原因。鉴于此,业界会使用已知缺陷较少的现有量产芯片来测试新的封装技术,以单独验证封装技术。在封装技术得到验证后,才会将其应用于新芯片的开发,进而再生产半导体产品。

图6展示了针对新芯片的封装技术开发流程。通常,在制造半导体产品时,芯片设计和封装设计开发会同时进行,以便对它们的特性进行整体优化。鉴于此,封装部门会在芯片设计之前首先考虑芯片是否可封装。在可行性研究期间,首先对封装设计进行粗略测试,以对电气评估、热评估和结构评估进行分析,从而避免在实际量产阶段出现问题。在这种情况下,半导体封装设计是指基板或引线框架的布线设计,因为这是将芯片安装到主板的媒介。

封装部门会根据封装的临时设计和分析结果,向芯片设计人员提供有关封装可行性的反馈。只有完成了封装可行性研究,芯片设计才算完成。接下来是晶圆制造。在晶圆制造过程中,封装部门会同步设计封装生产所需的基板或引线框架,并由后段制造公司继续完成生产。与此同时,封装工艺会提前准备到位,在完成晶圆测试并将其交付到封装部门时,立即开始封装生产。

▲图6:半导体封装技术的开发流程(来源:ⓒ HANOL出版社)

半导体产品必须进行封装,以检测和验证其物理特性。同时,可通过可靠性测试等评估方法对设计和流程进行检验。如果特性和可靠性不理想,则需要确定原因,并在解决问题之后,再次重复封装流程。最终,直到达成预期特性和可靠性标准时,封装开发工作才算完成。

05

对半导体封装作用的展望

在研究封装技术在保护和连接半导体的各种元件方面发挥的作用时,了解封装流程中所用的材料和方法同样至关重要。下一篇文章将探讨常规封装与晶圆级封装之间的差异,以及不同封装方法如何影响封装流程的质量和效率。