温馨提示:点击上方蓝字关注“皇华电子元器件IC供应商”,或者添加微信公众号:ameya360,每日收获最新最快最热门的IC芯片资讯。如果您需采购元器件,请发邮箱amall@ameya360.com

内存计算 (CiM:Compute-in-memory) 已成为一种有吸引力的计算范例,可解决深度学习应用传统设计中的内存和电源墙问题。借助 CiM,运行深度学习算法所需的部分计算可以在内存本身中执行,从而避免在内存和处理单元之间移动大量数据。

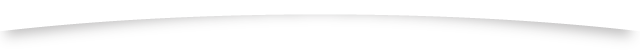

在深度学习算法中,主要运算是权重矩阵和输入向量的矩阵向量乘法。在这些操作中,来自输入向量的激活信号乘以预编程的权重,这些权重存储在存储器元件的阵列中。输出是求和线(或位线)上所有贡献的加权和。

正在研究用于存储权重的不同类型的非易失性存储器技术。最流行的是电阻式存储器,例如电阻式 RAM (RRAM)、相变存储器 (PCM) 和磁性 RAM (MRAM)——存在两种不同电阻状态的存储器。存储元件排列成交叉阵列并将权重存储为电导。

几年前,佐治亚理工学院的研究人员开始探索在模拟 CiM 应用中使用铁电电容器 (FeCAP) 存储重量的可能性。与电阻式存储器相比,FeCAP 具有两大优势。首先,这些电路显著提高了功率效率,其次,由于没有潜行电流流经电路,因此不需要选择器器件。

图 1 原理图展示了 CiM 交叉阵列,其中 FeCAP 用作节能非易失性权重元件来执行矩阵向量乘法运算。

需要非破坏性读取操作

FeCAP 类似于传统电容器,但在两个金属层(电极)之间具有铁电材料,而不是传统的介电材料。铁电材料可以存在两种电极化状态:P+和P-,这两种电极化状态可以通过外部电场反转。当该场被移除时,铁电材料保持其极化状态,从而使 FeCAP 具有非易失性特性。

如今,铪锆氧化物 (HZO) 因其缩放潜力而成为存储器应用的首选铁电材料。然而,读取 HZO 基 FeCAP 偏振态的传统方案具有破坏性。它依赖于铁电材料的极化切换,因此需要在每次读取操作后重新编程极化状态。

因此,数据读取操作的最大数量(读取耐久性)与数据写入操作的最大数量(写入耐久性)相关。因此,读取耐久性无法独立优化。这对于 CiM 应用程序来说是一个问题,因为它需要几乎无限的读取耐久性,而低得多的写入耐久性通常就足够了。

在2023年IEDM会议上,佐治亚理工学院和imec首次提出了将FeCAP的读写耐久性完全解耦的解决方案。该解决方案基于在两个电极的界面中引入不对称性。

这些非对称设计的 FeCAP 器件可读取超过 1011 次,而不会干扰 HZO 铁电体的极化状态。此外,在0V读取电压下获得了创纪录的8.7的电容存储窗口,代表了P+和P-状态下铁电体的相对介电常数之间的差异。这些结果使 FeCAP 成为一种有前途的 CiM 应用技术。

非破坏性读取操作背后的机制

非破坏性读取耐用性 >1011 FeCAP 的能力部分是通过研究读取机制背后的物理原理实现的。对基本原理的基本理解也为进一步改进结果提供了坚实的基础。

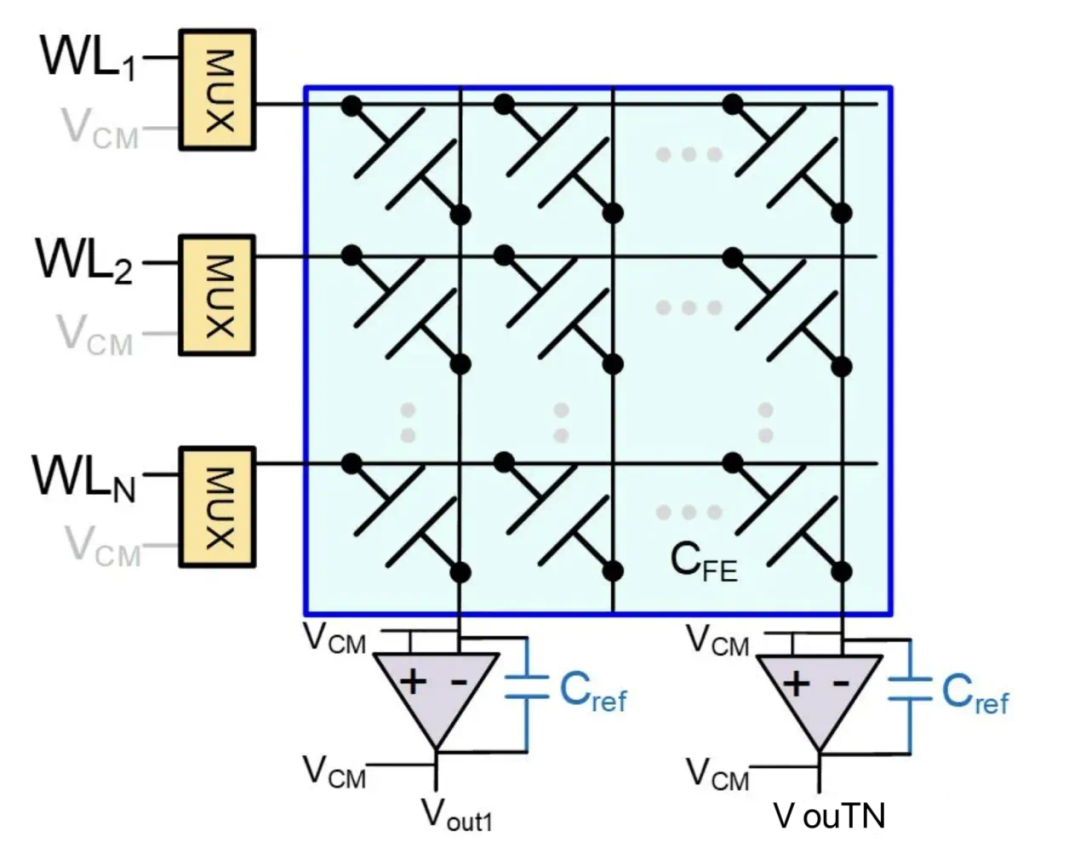

与传统介电材料不同,铁电材料在施加的电场和极化电荷之间具有非线性关系,从而使铁电极化电压(P-V)特性呈现磁滞回线的形式。

图 2 在本工作中使用的 FeCAP 器件的磁滞回线中,蓝色曲线代表器件在“唤醒”和打开存储窗口后的极化行为。

这种现象被用于 FeCAP 的传统读取方案中。实际上,施加电压脉冲以将存储单元翻转到其相反的极化状态。当这种情况发生时,等于 P+ 和 P- 之间的差值的位移电荷被释放并被检测到。这种差异称为剩余极化 (2PR),代表记忆窗口。

为了充分区分 P+ 和 P-,残余极化 2P 在器件的整个使用寿命期间应尽可能高记忆。然而,主要缺点是每次读出后都需要对单元重新编程,使得读取耐久性取决于写入耐久性。

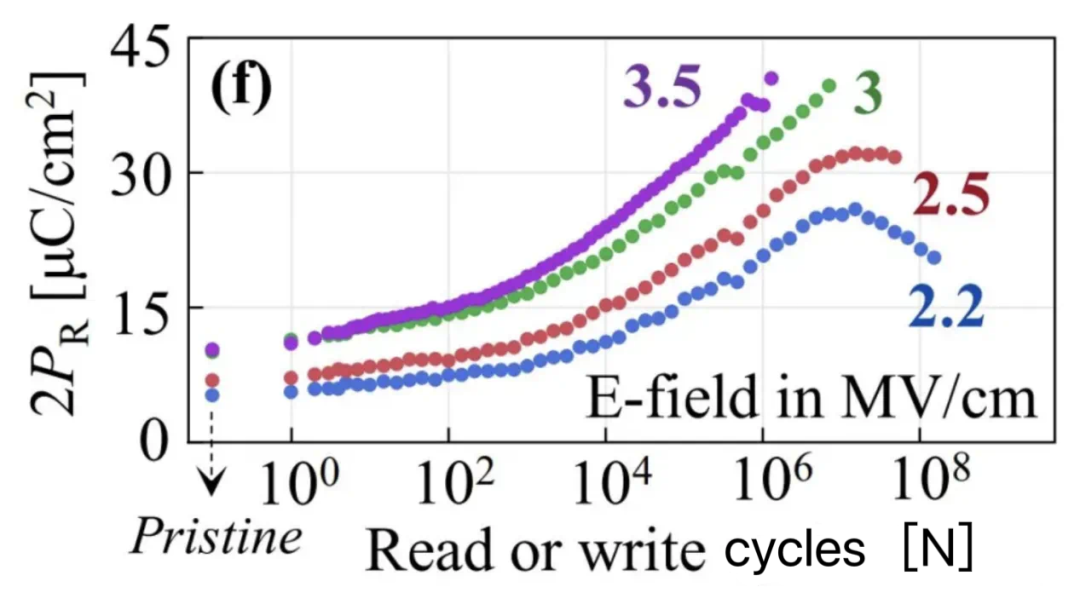

图3 在不同电场下测量的FeCAP器件的传统读写耐久性中,破坏性读取操作依赖于铁电极化极化切换。

佐治亚理工学院和imec 的研究人员采取了不同的方法。他们从不同的内存窗口概念开始。他们没有利用 P+ 和 P- 之间的差异,而是使用电容内存窗口的概念。该电容存储窗口是 FeCAP 处于 P+ 或 P- 状态时的电容状态之间的差异。它可以从 C-V 测量中得出,该测量绘制了铁电材料对施加电场的非线性电容响应或相对介电常数 (eR) .

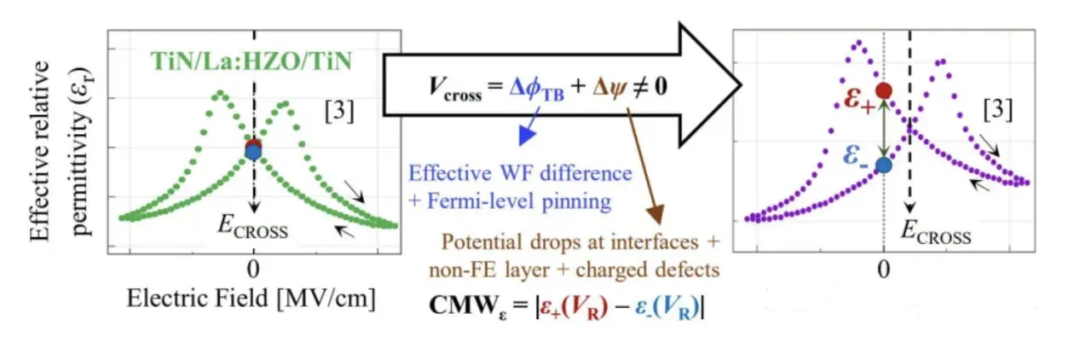

图 4 针对对称 FeCAP(左)绘制了蝴蝶状介电响应,显示了在施加 0MV 电场时正负 C-V 分支的交叉/cm,导致 0 MV/cm 时电容存储窗口 = 0。经过功函数工程后,获得了非对称 FeCAP,其电容存储窗口为 0 MV/cm(右)。

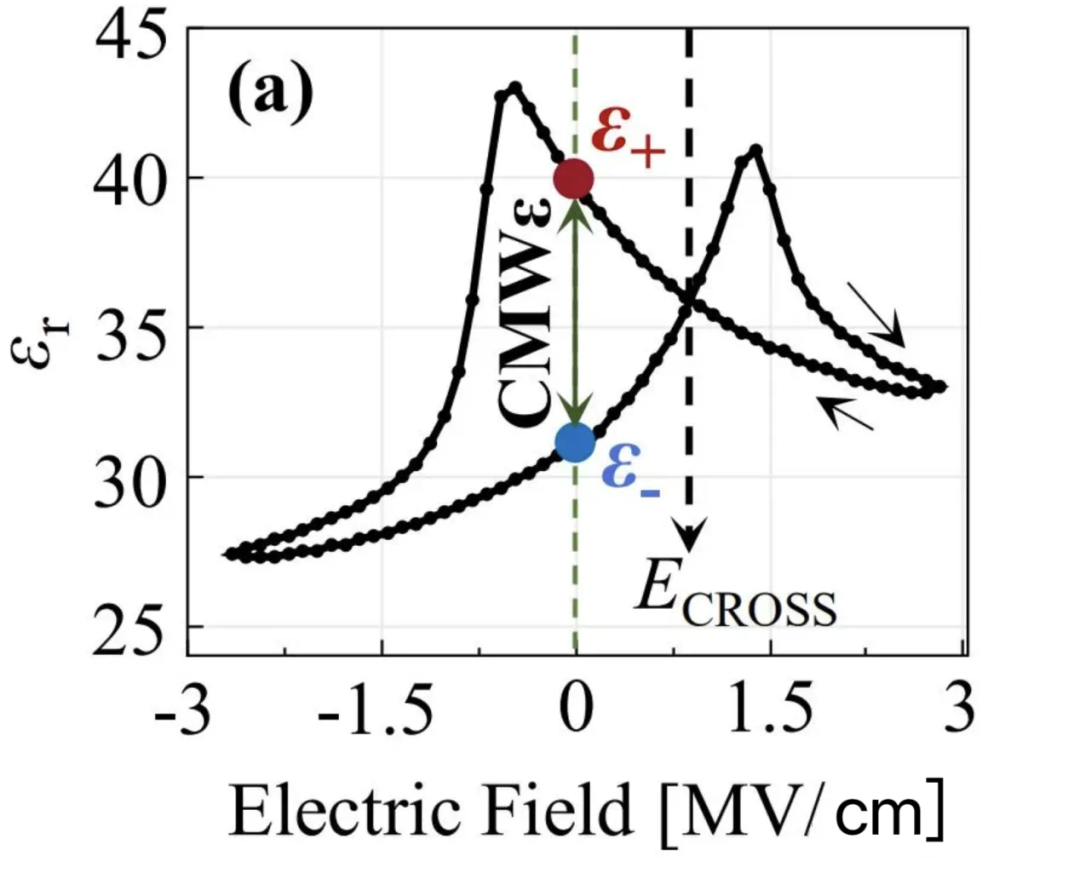

铁电电容器的 C-V 曲线类似于 0 V 附近的对称蝴蝶曲线,如图 4 的左侧部分所示。在 0 V(或零电场)下,蝴蝶曲线的正分支和负分支交叉,导致零电容存储窗口。然而,研究团队找到了一种方法,通过对两个电极施加功函数差异来打开 0 V 的存储窗口(参见图 4 的右侧部分)。经过电极的界面工程和材料堆叠的进一步优化后,在 0 V 下可以获得高达 ~8.7 的电容存储窗口。

图 5 非对称器件的 C-V 响应显示在 0 MV/cm 时具有约 8.7 的大电容存储窗口

然而,应用准静态 C-V 测量来读出 FeCAP 并不是一种电路友好的读取操作。因此,作为最后一步,研究人员表明,可以通过应用基于脉冲的读取方案并读出电荷来检索相同的信息,这在存储器操作中更常用。

通过这种读取方案,他们在 0-V DC 偏压下实现了 >1011 周期的非破坏性读取耐久性,而无需施加极化切换的电场(矫顽场)。该方案允许读取耐久性与写入耐久性完全解耦。

迈向 3D 铁电存储器

目前正在进行研究,以进一步提高 CiM 应用的 FeCAP 的读取耐久性和电容存储窗口。这是通过进一步设计电极的材料堆栈和功函数来实现的。通过在非零直流偏置之上施加交流读取脉冲,还可以进一步扩大电容存储器窗口。然而,在这种情况下,必须注意不要超过矫顽场。

此外,imec 的研究人员正在研究在类 DRAM FeRAM 存储器应用(嵌入式和独立式)中使用 FeCAP 和无损读出方案的可行性。然而,经典主动存储器和 CiM 类型操作之间存在一些显着差异。例如,对于主动存储器应用,除了高读取耐久性之外,还需要比 CiM 操作更高的写入耐久性。

此外,在 CiM 中,在测量结果之前会累加同一位线上所有存储单元的小信号贡献。然而,在经典的存储器应用中,必须可靠地测量每个单独单元的状态。这对每个单独的 FeCAP 的读出信号的幅度提出了更严格的要求,需要更大的存储窗口。imec 团队正在探索 FeRAM 应用的规范以及如何实现它们。

对于这两种应用,预期的趋势是进入三维以进一步增加存储密度。因此,通过可用于基于 HZO 的电容器的原子层沉积工艺,FeCAP 将从平面电容器结构转变为 3D 电容器结构。从长远来看,基于 FeCAP 的存储器可以集成在外围逻辑电路之上。

所提出的工艺技术的两个特征使这成为可能。首先,如前所述,由于不存在潜行电流,因此不需要选择器器件(通常是晶体管)。这使得能够将铁电存储器嵌入逻辑电路的后端(BEOL)中。其次,制造基于 HZO 的 FeCAP(例如低温 ALD 工艺)所需的热预算低于 400°C,使得该技术完全兼容 BEOL。

FeCAP 在 FeRAM 中的潜力

佐治亚理工学院和imec的研究人员首次证明了以非破坏性方式读取FeCAP的可行性,从而完全解耦读写耐久性。可以证明>1011的非破坏性读取耐久性,而写入耐久性约为107 。

读出机制基于电容存储窗口的概念,可以证明该窗口的记录高值为 8.7。这些结果使 FeCAP 有希望成为 CiM 应用的候选者。此外,这些创新为探索 FeCAP 在嵌入式和独立 FeRAM 存储器应用中的潜力奠定了基础。

备注:文章来源于网络,版权归原作者所有,信息仅供参考,不代表此公众号观点,如有侵权请联系删除!

———— /END / ————

重磅!日本电子巨头正式退市!

台积电董事长刘德音将于2024年退休 董事会提议魏哲家接任

传ASML将在未来几个月推出2nm制造设备 英特尔已采购6台

Panasonic专区 | 现货促销,即时库存,下单即发!

关于AMEYA360

AMEYA360商城(www.ameya360.com)上线于2011年,现有超过3500家优质供应商,收录600万种产品型号数据,100多万种元器件库存可供选购,产品覆盖MCU+存储器+电源芯片+IGBT+MOS管+运放+射频蓝牙+传感器+电阻电容电感+连接器等多个领域,平台主营业务涵盖电子元器件现货销售、BOM配单及提供产品配套资料等,为广大客户提供一站式购销服务。