【研究背景】

实现高能量密度的固态钠电池(SSSB)面临的关键挑战包括具有稳定的钠金属阳极、构建稳定的钠-固态电解质(SE)界面,以及制备薄而致密的SE。通常Na -SE界面存在高界面接触电阻、循环形成的空隙、枝晶生长和界面电化学不稳定等问题。Na1+xZr2SixP3-xO12(0 ≤ x ≤ 3)(NASICON)族无机固态电解质具有良好的离子导电性、良好的空气稳定性、成分可调性和优越的机械强度而被广泛研究。然而,NASICON固态电解质由于其相对较差的钠润湿性以及与熔融钠的不稳定性,限制了其在实际应用中的广泛使用。

【内容简介】

本研究成功制备了一种具有多孔-致密-多孔三层和多孔-致密双层3D NASICON架构的固态钠电池(SSSB)。首先对NASICON的成分进行了优化,之后采用原子层沉积(ALD)技术将纳米级ZnO涂层修饰导NASICON的表面,提高了整个3D SE框架对钠的润湿性,同时还充当了保护层,有效阻止NASICON与高温下的熔融钠接触进一步反应。这些设计策略在提高SSSB能量密度的同时,降低了阳极电解质界面的电阻。多孔层的引入不仅提高了固态电池的机械强度,还作为电极材料的3D网络主体,确保在循环期间电极的紧密接触。而薄的致密层则作为隔离层,阻止了活性电极组分的扩散。这些创新设计在改进SSSB性能方面具有潜在应用前景。

【结果和讨论】

NASICON成分优化

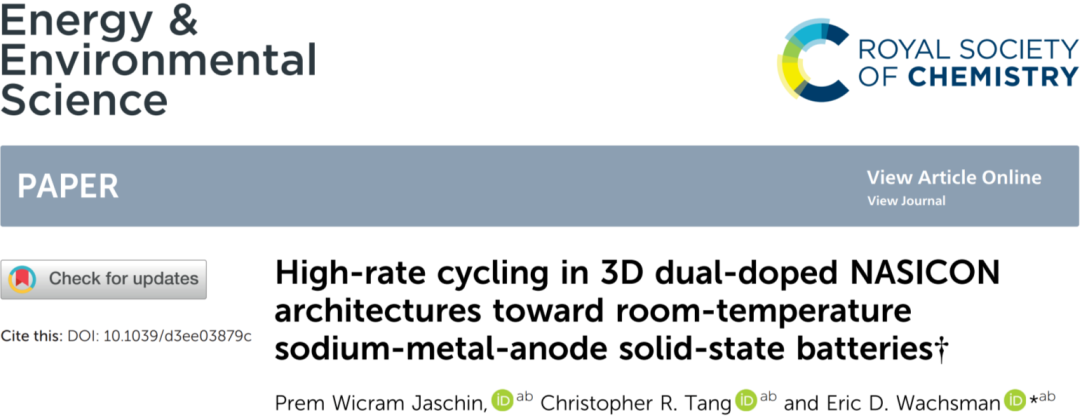

图1 (a)Na3.65Zr1.675Zn0.2Mg0.125Si2PO12的精修X射线衍射图。(B)单斜晶胞晶格参数和(c)菱面体-单斜相分数的变化曲线图,其作为由精修确定的掺杂剂的函数。(d)离子电导率与掺杂剂的关系图。(e) Na3.65Zr1.675Zn0.2Mg0.125Si2PO12的离子电导率随温度变化的Arrhenius图和(f)临界电流密度图(对称电池)。

本研究选用Mg2+和Zn2+对NASICON双掺杂。图1a详细展示了共掺杂的NASICON经过精修后的XRD图谱。双掺杂NASICON的XRD曲线经过拟合,Rp = 5.71%,wRp = 8.96%。图1b呈现了通过精修确定的单斜相的晶胞晶格参数随掺杂剂离子变化的情况。引入二价掺杂剂后,单斜晶胞的a轴和b轴增加,c轴减少,导致晶格体积减小。掺杂剂引起的单斜和菱面体结构的晶胞体积变化与文献报道一致,暗示了与钠离子迁移相关的瓶颈可能在这一过程中得到改善。图1c显示了根据细化过程估算的单斜和菱面体相对占比,其中未掺杂的NASICON呈现出单相单斜结构,而引入Zn2+和Mg2+导致形成单斜和菱面体的混合相。双掺杂NASICON显示更高的菱面体相。EIS测定了样品的离子电导率,图1d展示了未掺杂和掺杂NASICON样品的晶粒、晶界和总离子电导率随掺杂剂变化的情况。未掺杂的NASICON样品的总离子电导率受到低晶界电导率的严重限制。而掺杂Zn2+和Mg2+的总离子电导率分别达到1.1 mS/cm和1.5 mS/cm。双掺杂NASICON的晶粒、晶界和总离子电导率分别为6.3mS/cm、4.4mS/cm和2.7mS/cm。共掺杂的总离子电导率约为未掺杂的十倍。低温阻抗测量显示随着温度降低,样品的阻抗增加。将晶粒、晶界和总离子电导率的Arrhenius图作温度的函数(图1e),确定其各自的钠离子迁移活化能为0.21、0.30和0.29 eV。对称电池Na/SE/Na的临界电流密度(CCD)测量显示,双掺杂NASICON获得了相对较高的临界电流密度(图1f)。

多孔-致密-多孔三层NASICON结构

Mg2+和Zn2+共掺NASICON三层微结构

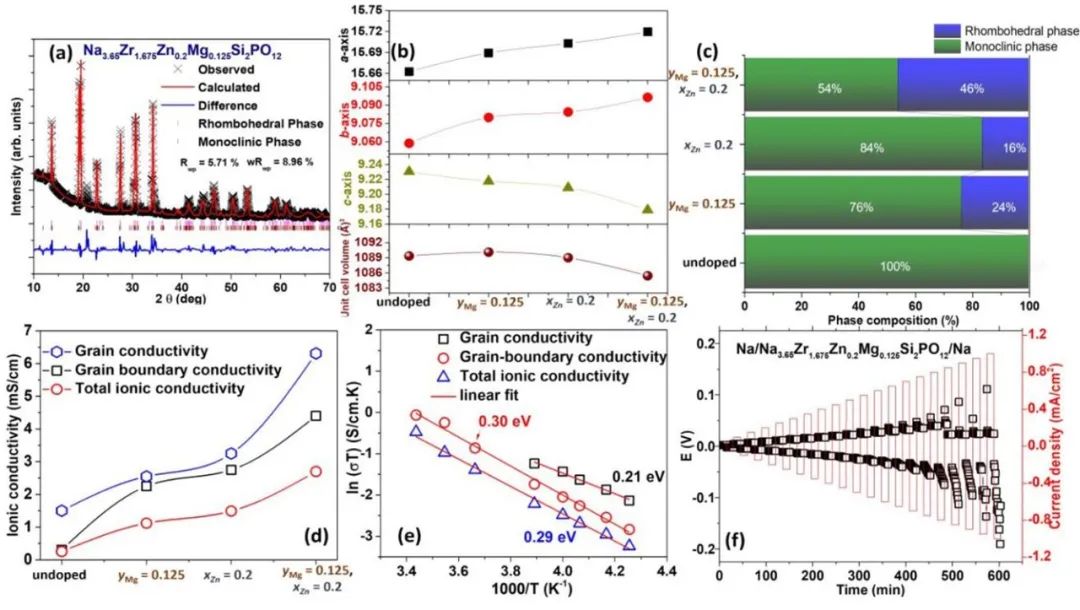

图2 烧结后的双掺杂NASICON三层结构的(a)截面SEM(B)多孔层、(c)致密层和(d)顶面图像。钠渗透的双掺杂NASICON三层的横截面(e)二次电子和(f)背散射电子图像(放大区域)。

采用商用流延法成功制备了具有三层微结构的NASICON材料。图2a展示了烧结后共掺杂的NASICON的典型三层陶瓷的横截面SEM图,其中多孔层厚度为50-60微米,而分隔电极的致密层为25微米。图2a的插图为光学图,三层结构表面平坦,孔径为5-10 µm,孔隙率约为65%(图2b)。多孔致密层界面展现了良好的连通性,在烧结过程中未观察到任何分层,这对于在电极之间建立持续的钠离子流是必要的。致密层中的填充颗粒融合充分,未显示出任何针孔或缺陷的迹象(图2c),这对于防止形成枝晶和短路至关重要。三层的俯视图(图2d)揭示了NASICON的大孔(10 µm)和高孔隙率,为钠金属的渗透提供了必要的条件。

钠金属渗入多孔层

为了构建3D钠金属阳极,将金属钠熔化并注入NASICON孔中。NASICON基底材料对熔融钠的润湿性较差。为了提高润湿性,采用了ALD技术,将纳米级ZnO修饰层修饰在NASICON三层孔的表面。SEM横截面成像证实了NASICON三层孔中存在钠金属(图2e,f)。钠渗透后,三层微孔隙良好、结构完整,多孔层与致密层之间未发生分层或破裂。在熔融钠注入过程中,未发现钠金属穿透致密层。图2f展示了三层横截面的放大区域的背散射电子图像,清晰显示了渗透的多孔NASICON的不同相的对比。暗区和亮区分别与渗透的钠金属和双掺杂NASICON微晶相关。该设计实现了钠金属与固态电解质之间的无缝接触,以确保低界面电阻。

NASICON的恒电流循环测试

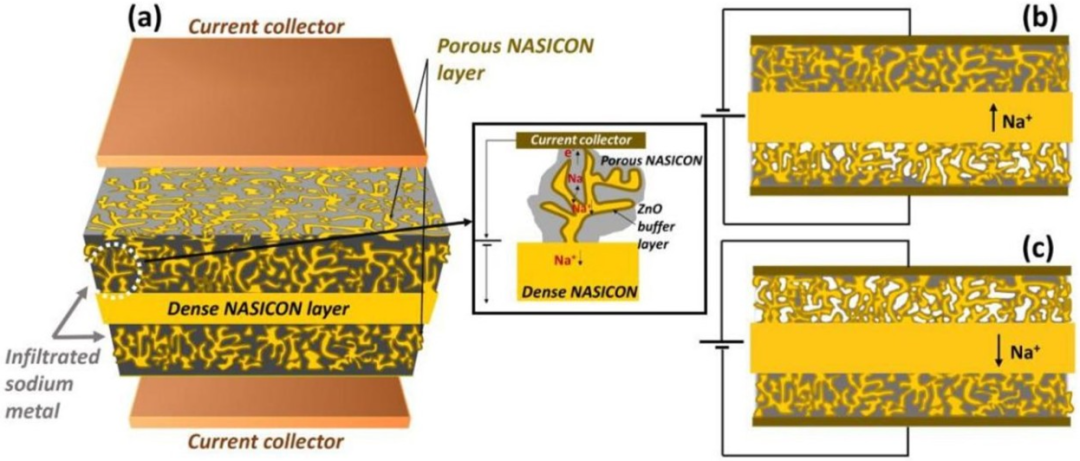

图3 (a)基于三层NASICON对称电池组件的示意图。在(b)和(c)中展示了在外部电流下钠金属穿过三层的孔的剥离和镀覆机理。

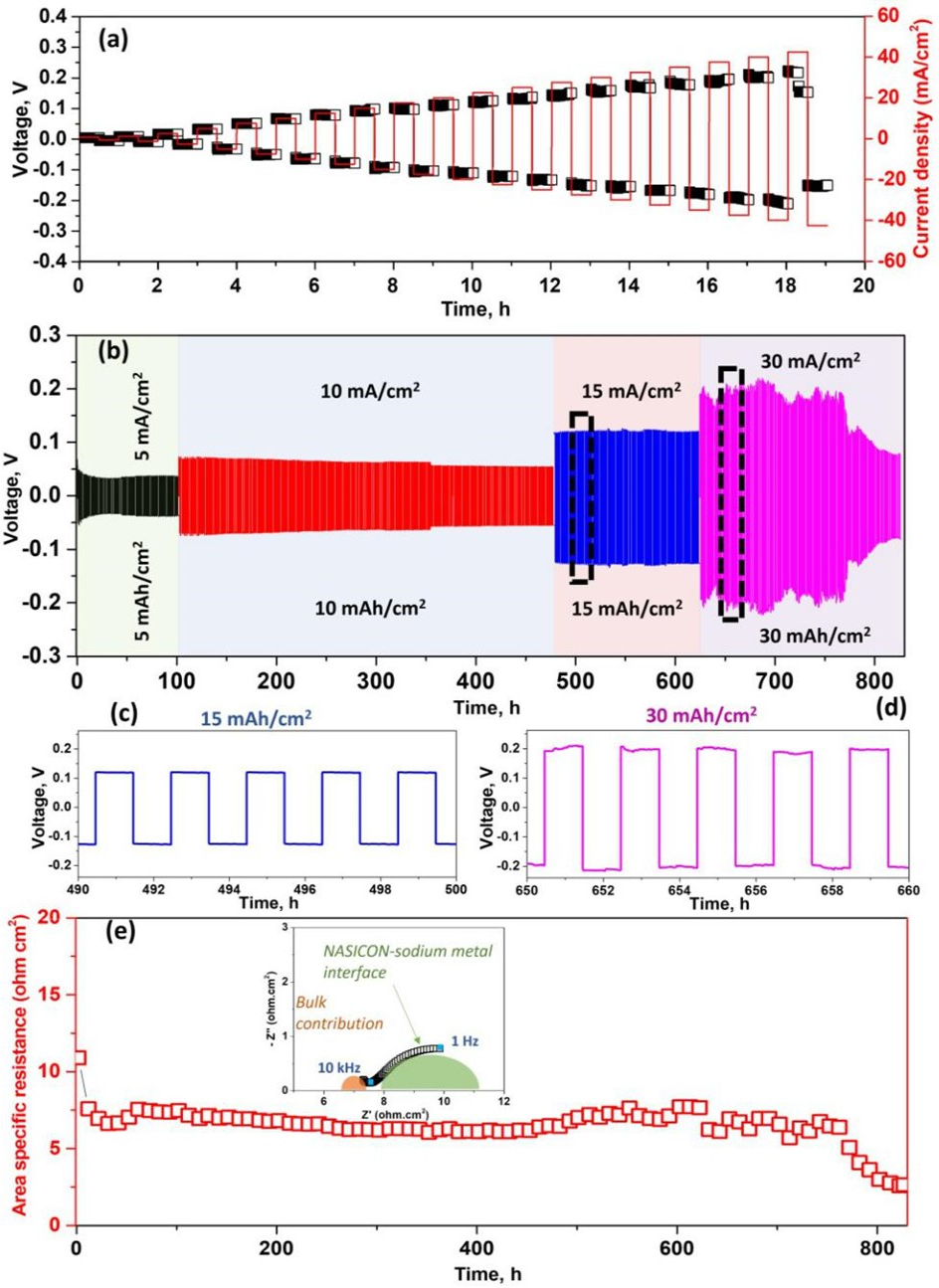

图4 (a)共掺杂的三层NASICON的对称电池对CCD测试的电势响应。(b)在5、10、15和30 mA/cm2的电流密度下测量钠对称电池的室温恒电流循环。在(c)15 mA/cm2和(d)30 mA/cm 2下记录的钠循环的放大电压曲线。(e)在5、10、15和30 mA/cm2下的恒电流循环期间对称电池的面积比电阻的变化。

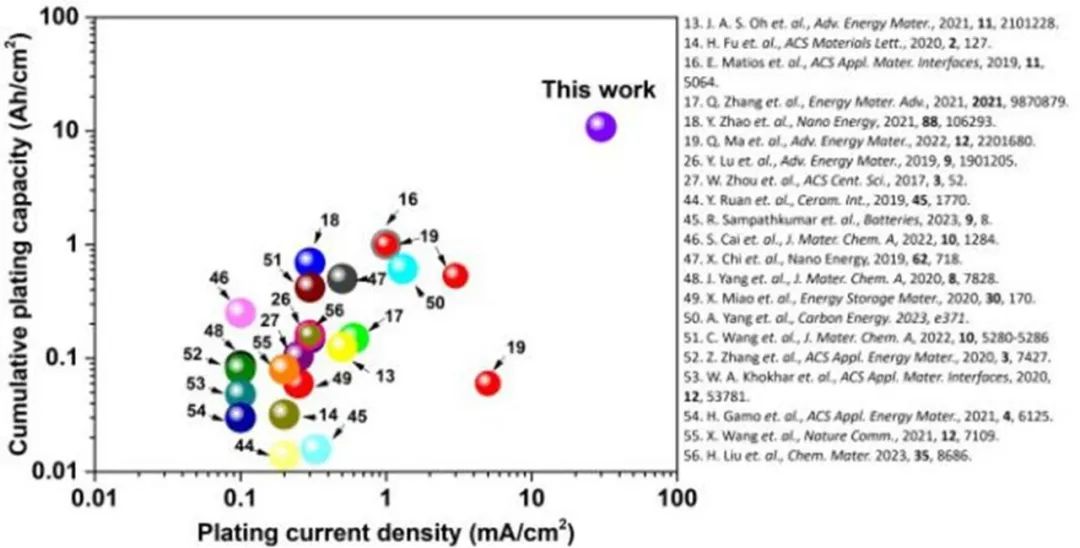

图5 文献中公开的各种无机陶瓷固体电解质的室温钠循环状态的图。

使用共掺杂NASICON组装的对称电池(图3a),以定量评估界面接触的改善,并研究室温下在没有堆叠压力的情况下的钠的剥离和电镀。图3b、c显示了在施加外部电流时离子穿过NASICON的迁移过程。当钠离子被电镀入其中一个多孔框架时,相对的多孔层同时发生剥离,形成空孔。为确保电子在电池中连续流动,在渗透后,附着在孔外的额外钠金属与集流体保持接触。共掺杂的三层结构NASICON对称电池实现了40 mA/cm2的创纪录的高CCD(图4a)。图4b展示了在5-30 mA/cm2电流密度下室温稳定循环。过电位呈稳定下降趋势,这可能与活化过程有关,该过程涉及到电镀钠和多孔NASICON之间接触的改善。电池在10和15 mA/cm2下分别获得68和120 mV的电镀/剥离电位的平台(图4c)。在30 mA/cm2下,观察到轻微噪声电压响应,表明钠-NASICON界面存在局部波动。电池在30 mA/cm2下剥离和电镀146小时后发生短路。在三层结构NASICON的典型渗透过程中,每个多孔层上渗透的钠金属的平均面积重量约为30 mg/cm2。因此,35 mAh/cm2的钠面积容量可在致密层上循环。这一容量仅取决于在熔融渗透期间附着到多孔层的熔融钠的量。在每侧镀覆(或剥离)的钠的累积容量总计为惊人的5.42 Ah/cm2。这是至今为止利用固态电解质实现的最高钠循环容量(图5)。对称电池在进行恒电流循环之前的总电阻(图4e插图)约为11.5 Ω cm2。面积比界面电阻(ASRint)降至3.5 Ω cm2。如此低的界面电阻表明NASICON电解质和钠金属之间的持续接触,足以支持高电流密度下的钠离子迁移。通过电压平台确定的总面积比电阻(ASRcell)如图4e所示。在活化过程中,ASR从11 Ω cm2下降到7.5 Ω cm2,并保持在接近7 Ω cm2的水平,直至发生短路,持续时间为770小时。

全电池验证

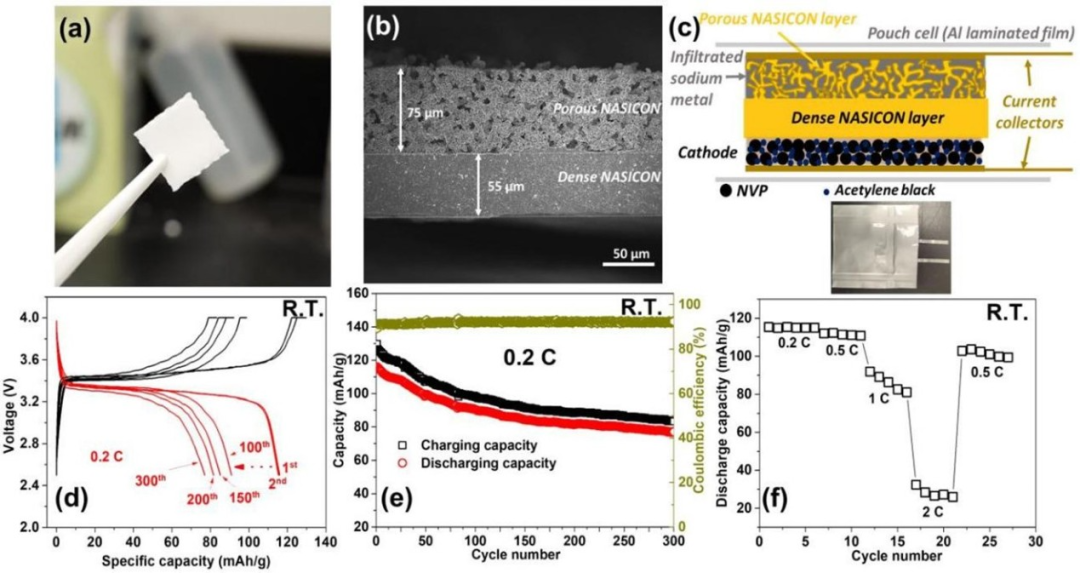

图6 (a)Zn、Mg掺杂的NASICON双层的光学和(B)横截面SEM图像。(c)软包电池的示意图和图片,(d)充放电曲线,(e)循环性能,和(f)在室温下测量的NVP/Zn、Mg掺杂的NASICON/Na设置的倍率性能测试。

图6a展示了1cm2尺寸的共掺杂NASICON双层的光学图像。双层的横截面SEM图像显示在图6b中,多孔层厚度约为75 µm,呈现出互连的孔网络。致密层的厚度约为55 µm,且没有任何孔隙或多孔层的分层现象。组装的电池采用最小量的液态电解质作为阴极电解质,以确保阴极-固态电解质的有效接触。含有钠金属阳极、NVP阴极以及共掺杂NASICON双层的全电池组装在软包电池中。图6c中展示了具有双层固态电解质的全电池的示意图和组装的软包电池的图像。图6d描绘了NVP阴极相对于钠在双掺杂NASICON中的充电-放电曲线,观察到在约3.4 V处的平坦充电和放电平台,表现出极低的极化。在0.2C的室温循环中,实现了116 mAh/g的初放电容量,接近NVP的理论容量(118 mAh/g)。充电-放电曲线在200次循环中保持不变(图6d)。图6e展示了电池在0.2C下的室温循环性能,库仑效率为92%。在0.2C下循环300次后,放电容量仍保持初始容量的66%。此外,在室温下进行倍率性能测试(图6f),在0.2C、0.5C、1C和2C下的室温放电容量分别为115 mAh/g、112 mAh/g、92 mAh/g和32 mAh/g。当电流降低到0.5C时,放电容量恢复到104 mAh/g。

【结论】

成功采用固相法合成了Zn2+和Mg2+共掺杂的Na3Zr2SiPO12。这种双掺杂策略有效提高了高菱面体相的比例(达到46%),形成更宽广的钠传导通道,从而在晶粒内部和晶界实现更高的离子电导率。共掺杂的NASICON体系表现出卓越的总离子电导率,达到2.7 mS/cm,并且相关的迁移势垒显著降低至0.29 eV。成功制备了具有多孔致密-多孔结构的三层NASICON。在NASICON表面经过ZnO包覆后,其润湿性得到显著改善,金属钠有效填充了多孔结构,确立了连续的界面接触,并使界面电阻降至3.5 Ω cm2。对称电池在5、10和15 mA/cm2的电流密度下进行的钠循环表现出稳定的电压滞后,在进行了146小时的钠循环后才发生短路。此外,该电池实现了每侧5.42 Ah/cm2的高累积钠电镀容量。组装的软包电池在0.2 C下表现出116 mAh/g的放电容量,并在经过300次循环后仍然保持66%的初始容量。

Jaschin, P.; Tang, C.; Wachsman, E. High-rate cycling in 3D dual-doped NASICON architectures toward room-temperature sodium-metal-anode solid-state batteries. Energy & Environmental Science 2024, 10.1039/D3EE03879C. DOI: 10.1039/D3EE03879C.

来源:能源学人