了解DDR首先要对其命令时序有所了解,尤其是读写命令。这里简单起见以LPDDR为例分享其读写的关键时序和参数。本文重点在读写时序和参数,其他暂时按下不表。参考《JESD209B.pdf》

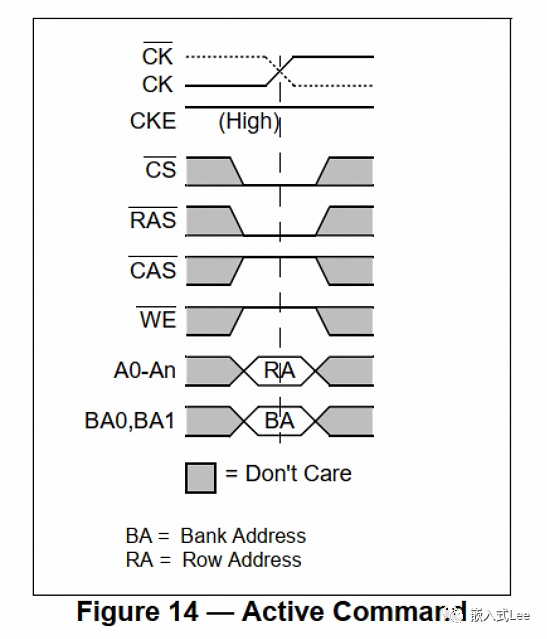

Active命令,激活行个人觉得称为打开行更贴切。

在向LPDDR SDRAM中的bank发出READ或WRITE命令之前,必须打开该bank的一行row。通过ACTIVE命令完成(见下图):BA0和BA1选择bank,地址输入选择要打开的行RA。可以同时有多个bank处于打开(活动)状态。

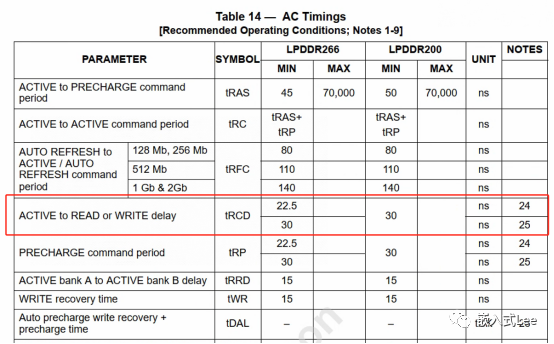

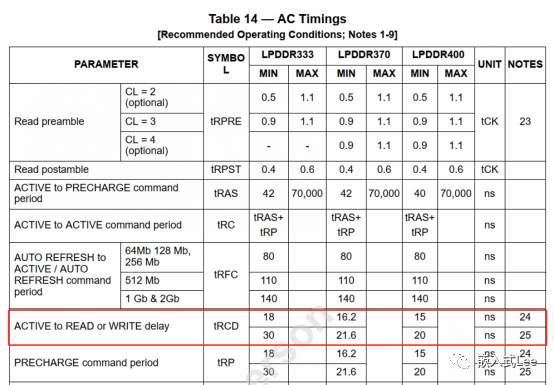

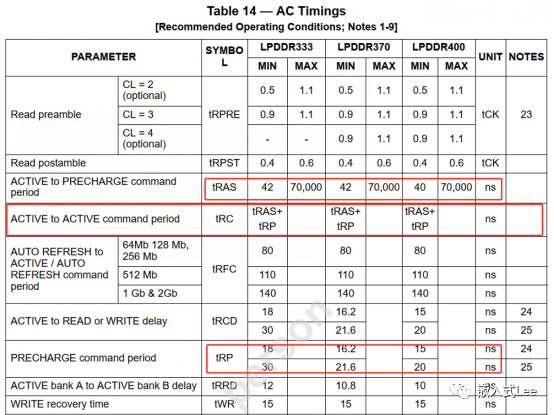

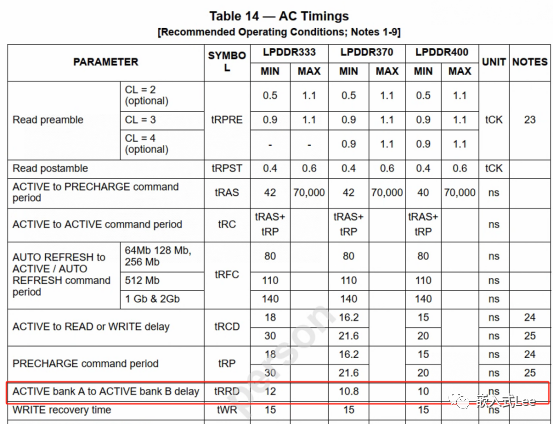

tRCD即打开行后到读写之间的间隔, 行row打开后,就可以在tRCD要求的最小时间后向该行发出READ或WRITE命令。

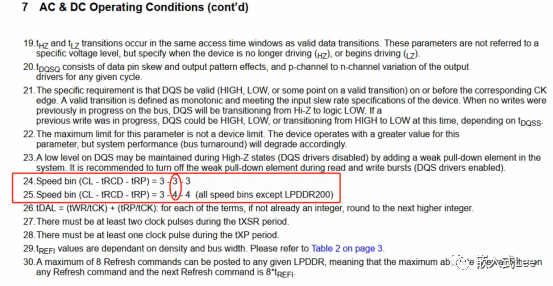

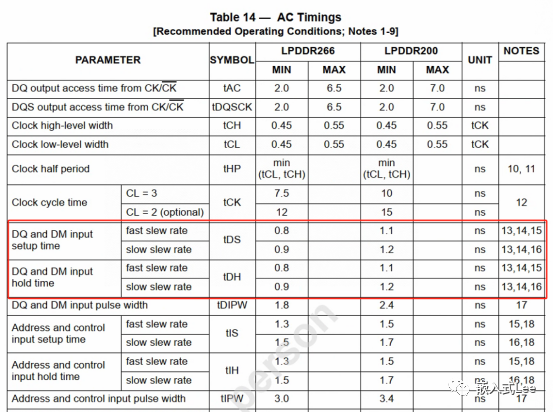

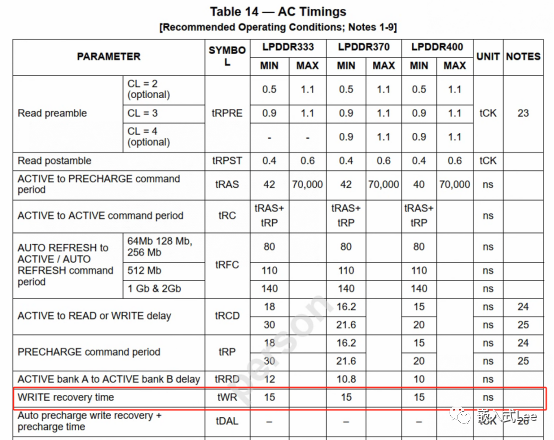

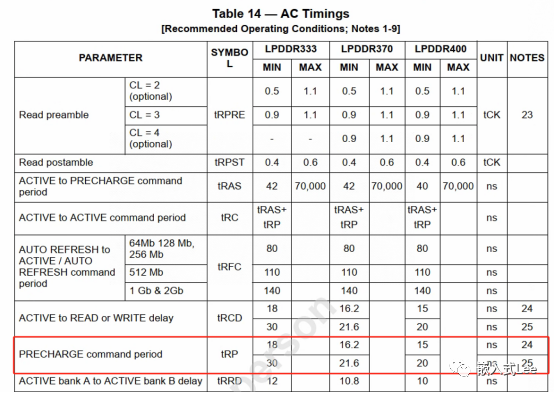

上述定义的是绝对值,实际上以CK单位是多少呢?

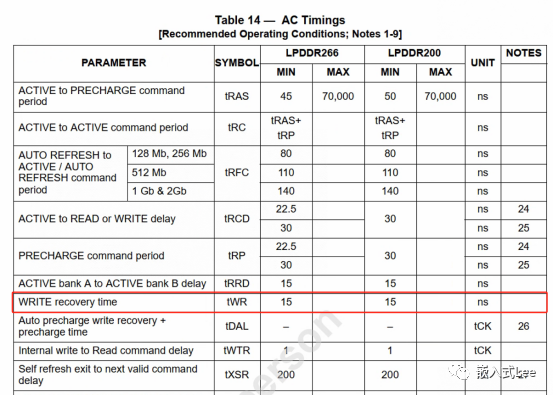

对于NOTE24和NOTE25两行,分别对应的是3和4个CK,其中LPDDR200只有一个等级,对应3个CK。

可以找一个手动计算一下,以LPDDR400为例其频率是200MHz(400是按照DDR计算的),一个时钟周期是1/200uS=5nS,对于15nS时间就是3个CK,20nS就是4个CK, 其他频率的参数计算也是一样。

同一bank,ACTIVE到ACTIVE命令最小间隔。

只有在前一行关闭后,才能向同一bank中的另一行发出后续ACTIVE命令。同一bank上两个ACTIVE命令之间的最小时间间隔由tRC定义,其值为tRAS+tRP的和。注意这里tRAS有最大值限制。

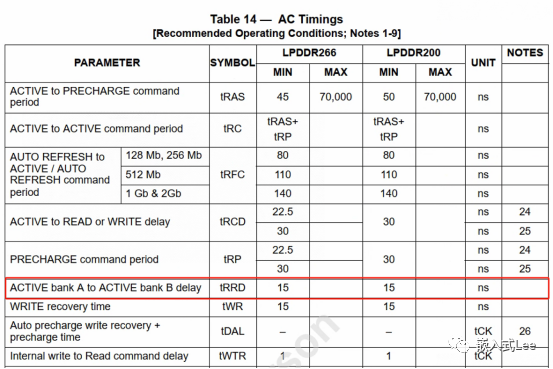

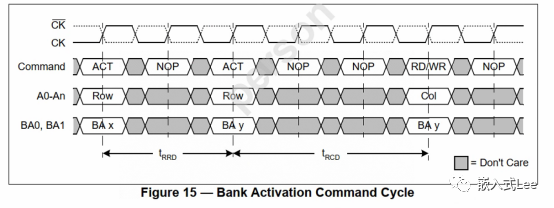

不同BANK之间ACTIVE命令的最小间隔。

当第一个bank被访问时,可以向另一个bank发出后续的ACTIVE命令,这可以减少总的行访问开销(间隔更小,且不需要关闭当前bank的行,不需要重新回来时又要重新打开)。不同bank上两个ACTIVE命令之间的最小时间间隔由tRRD定义。

可以看到tRRD小于tRCD。

下图显示了tRCD和tRRD的示意。

打开的行会保持活动状态,直到向bank发出预充电命令(或带有自动预充电的READ或WRITE命令:A10指定)关闭行。

在打开同一bank中的不同行之前,必须发出预充电命令(或带有自动预充电的READ或WRITE命令:A10指定)关闭行。

总结一下:

lbank相对独立, 但是操作以行为单位,不同bank内的行可以同时操作;

同一bank内行一次只能操作一个,需要预充电(或自动预充电读写)关闭一个行才能打开另外的行操作。

l关闭行用预充电或自动预充电的读写,打开行用Active命令。

ltRCD是一个性能相关参数,他的大小影响访问速率,因为打开行是一个普遍常用的操作。

l做一个不是特别恰当的类比,LPDDR需要先Active打开行,读写,然后关闭行。类似于FLASH的读写,先加载PAGE到缓存,然后随机读写修改PAGE缓存,然后将缓存编程入FLASH。

列地址即对应PAGE内偏移,行地址即对应PAGE地址,操作单位PAGE对应行。

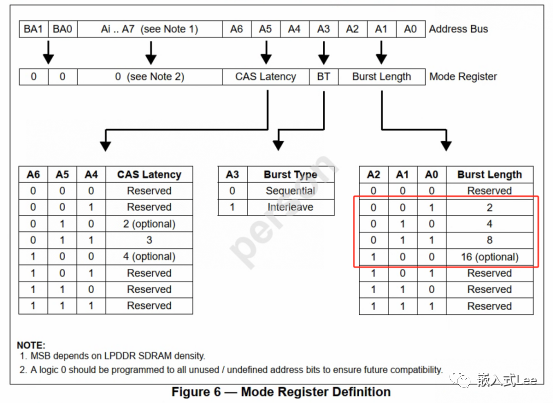

读写都是burst操作,其中burst长度为模式寄存器中指定, burst长则负载率高有效数据占整个传输比例高,但是失败后代价大浪费比较多的时间,burst短则负载效率低,但是失败后代价小。16是可选的,出于以上burst长的优势,有些厂家提供更长的burst选项,此时对连续操作比较多的场景更适用,比如启动时加载启动程序到LPDDR一般是连续的操作,长burst效率更高。

为什么burst都是2,4,8这种偶数呢,参考《https://mp.weixin.qq.com/s/i1U70EpQ1Lt89EpzqCMQFg》

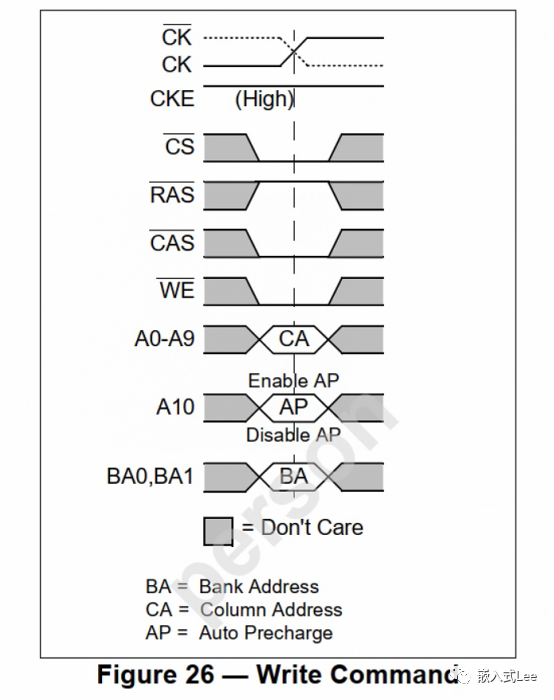

写需要在行打开之后进行,BA0,BA1选择bank, 而地址输入指定列地址。

A10选择是否自动预充,A10=1时,burst操作完后自动预充关闭行,否则不自动预充,行仍然处于打开状态。这两种模式分别针对不同的应用场景,随机读写前者更合适,因为大概率后面不再操作本行则自动关闭,免得后面还要手动预充关闭; 后者适合连续操作,大概率仍然要操作本行先不关闭。

DM信号用于写MASK, 和DQ完全对齐,DM=1则相应的数据将被颗粒忽略不写入,DM=0对应的数据写入。

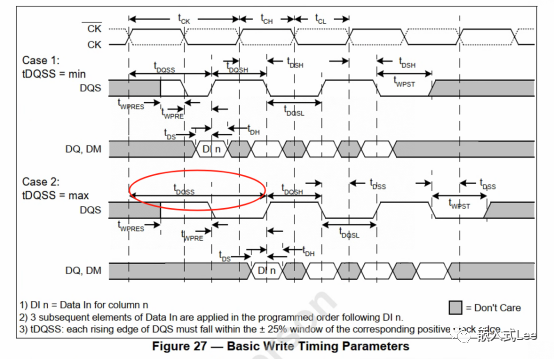

写时DQS由控制器发出,对齐到DQ的中间,使得颗粒能在DQ的中间采样。

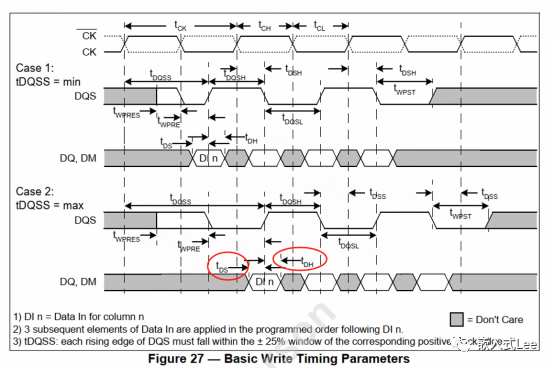

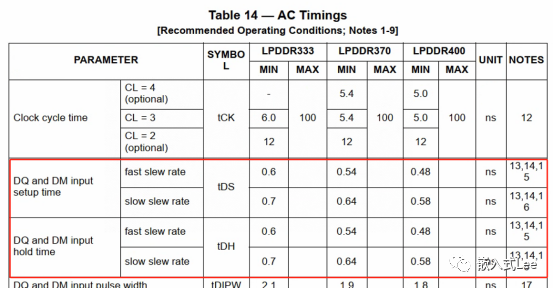

DQ/DM的建立时间和保持时间,即DQ/DM在DQS边沿前多久准备好,边沿后保持多久。

这对发送很重要,决定颗粒能不能正确采样。理论上颗粒在采样时DQS边沿在DQ/DM正中间最好,由于path路径影响,控制器发送端到颗粒采样时相位并不是一样的。控制器发送端此时可以调整DQS延迟,让颗粒接收端采样时刚好DQS在DQ中间,这就是写training。

可以通过不断延迟DQS来写并回读(读此时要保证是OK的即读要先training,而读可以通过读颗粒输出的预设值无需依赖写),在写入回读正确的DQS延迟范围内选择中间的DQS延迟值即为training结果。

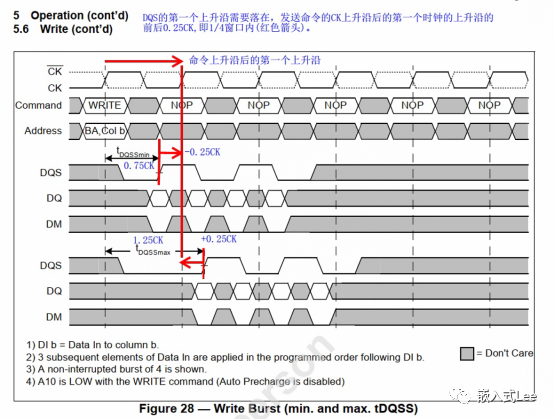

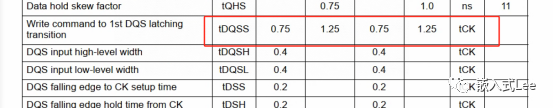

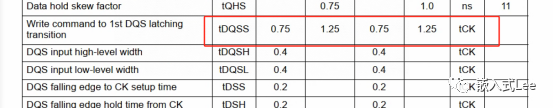

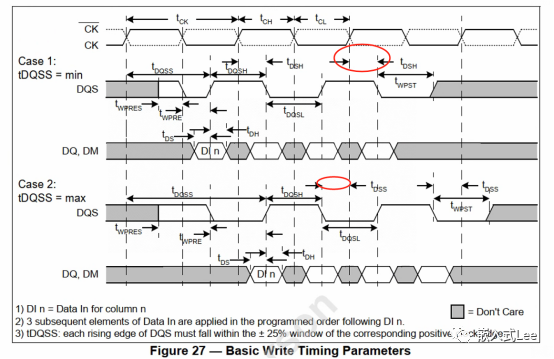

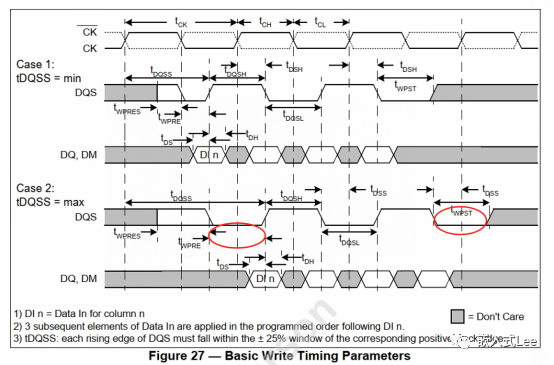

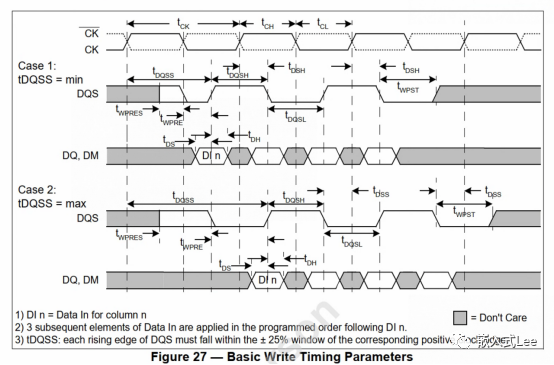

写命令下一个周期即可写数据,tDQSS即写命令对应的CK上升沿与第一个DQS上升沿的间隔。必须在0.75和1.75CK之间,即在后一个CK上升沿的±1/4CK窗口内。

DQS和CK周期是完全一样的。

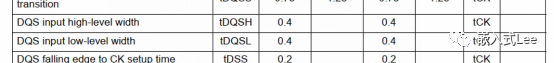

tDSS:CK上升沿前DQS建立时间。

tDSH:CK上升沿后DQS保持时间。

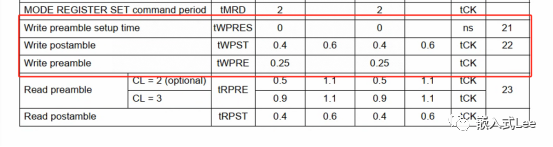

tWPRES:Write preamble的建立时间,即DQS拉低确认为preamble之前保持高多久。

tWPRE:Write preamble保持时间,即第一个上升沿之前的低时间。

tWPST:Write postamble保持时间,即最后一个下降沿之后的低时间。

下面是一个详细的写时序图,我们来对关键参数过程进行理解

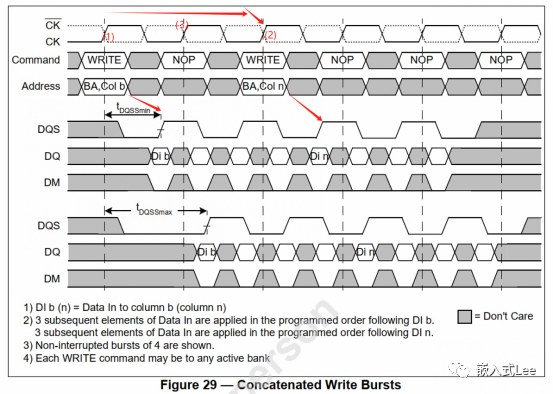

任何WRITE burst的数据可以与随后的WRITE命令连接或截断。在任何一种情况下,都可以保持输入数据的连续流动。新的写入命令可以在先前写入命令之后的时钟的任何正沿上发出。

在完成的burst的最后一个元素或被截断的较长burst的最后所需数据元素之后,应用来自新burst的第一个数据元素。新的写入命令应在第一个写入命令之后X个周期发出,其中X等于元素对中所需数据的数量。

上图演示了burst长度4的连续写

(1)第一次写

(2)2个CK之后第二次写

(3)两次写间隔2CK刚好是burst 4需要的周期数4/2(双边沿),所以连续无间隔。

(4)上下两部分,分别演示了tDQSS最小和最大时的情况。

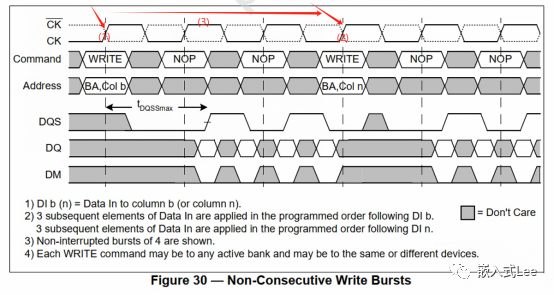

上图演示了burst长度4的非连续写

(1)第一次写

(2)3个CK之后第二次写

(3)两次写间隔3CK,在burst 4传输完还空闲了一个CK。

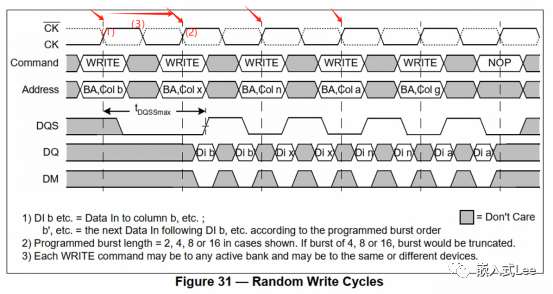

上图演示了随机的持续写

(1)第一次写

(2)1个CK之后第二次写

(3)两次写间隔1CK,只能传输2n数据。如果burst大于2则后面的被截断,重新响应后面新的命令。效果是任意随机的写。这也解释了为什么写无需终止burst命令,连续写就可以实现截断,进行随机写的效果。

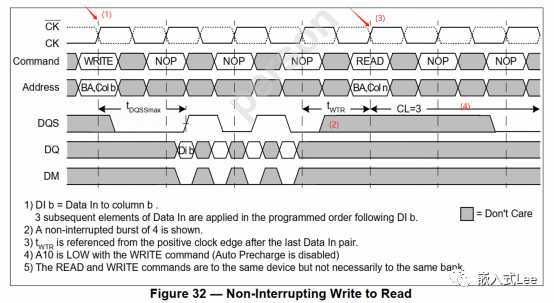

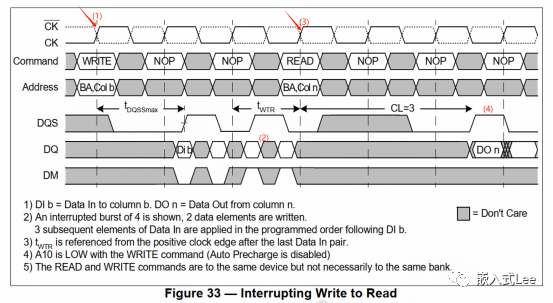

任何burst写入的数据之后可以是后续的读取命令。要在不截断burst写入的情况下执行后续读,应满足tWTR,如图所示。

(1)发送写命令,两个周期完成写入burst 4

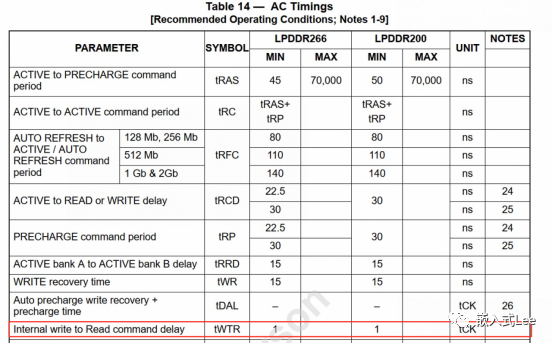

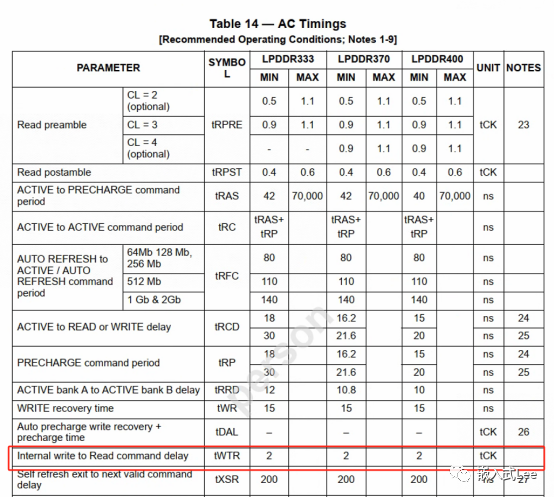

(2)写入完成后的第一个CK边沿开始(注意先要找最后数据的DQS,然后再找该DQS后的CK上升沿),延迟tWTR,图中是一个CK(参数见后图根据频率可能是1或者2CK)。A10=0不使能自动预充。

(3)新的读命令。和写是同一设备可以是不同行。

(4)CL时间之后,颗粒返回数据。(CL的含义见读部分)

如下图所示,任何burst写入的数据都可能被随后的READ命令截断。注意,只有在tWTR周期之前成对数据才会写入内部阵列,并且任何后续数据都必须用DM屏蔽。

(1)写数据命令, 假设burst=4

(2)假设只想写入2个数据,就转为读,则在第一个DQS后,MASK掉后续的DQS数据,即后面的DQ时DM=1,然后tWTR之后读。tWTR的参考是找有效DQS时钟后的CK的上升沿。

(3)读命令

(4)延迟CL之后颗粒返回数据。

如果没有使能A10=1自动写预充,则WRITE burst之后可以是同一bank的预充电命令。

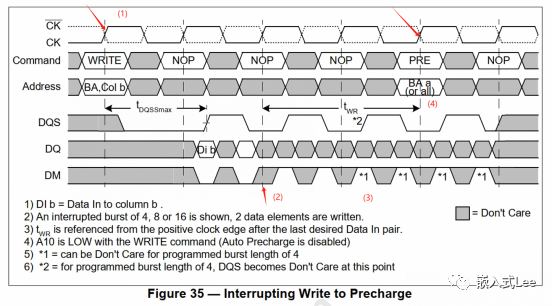

如图所示。任何WRITE burst的数据都可能被后续的PRECHARGE命令截断。

(1)写命令

(2)tDQSS比较大。大于1CK(最大不大于1.25CK)后,DQS输出数据。

(3)要提前截断,此时DM=1 可以MASK掉不需要写入的数据(图中所写实际此时颗粒也不关心DM了),此时只写了2个数据。

(4)tWR周期以最后DQS有效数据后的第一个CK上升沿开始,这里是2CK,此时间内颗粒不关心DQS,DM。

(5)tWR之后发送预充命令。

注意,只有在tWR周期之前的成对数据(双沿操作)才会写入内部阵列,任何后续数据都应该用DM屏蔽(但是图中写的Don’t Care??,这里控制器还是要求必须要DM数据吗 )。

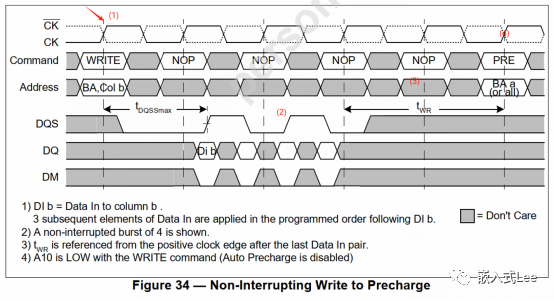

要在不截断WRITE burst的情况下遵循WRITE,应满足tWR,如图所示。

(1)写命令

(2)tDQSS比较大。大于1CK(最大不大于1.25CK)后,DQS输出数据,两个周期完成burst 4传输。

(3)tWR周期之后,可以发送预充点命令。tWR参数见后图。

(4)预充电命令。

在PRECHARGE命令之后,在满足tRP之前,不能向同一bank发出后续命令。

tRP对应3或4个CK。

@todo 为什么没有写终止而读有,为什么读到写不能无缝切换,写到读可以无缝切换。

下一篇继续