Prefetch Architecture实际和training没太大的关系,但是对于理解一些概念和一些参数的计算有很大的帮助,所以单独拎出来浅淡一下。

注:以下约定除非i特别说明均基于LPDDR2。

我们还是延续,”看到相关内容随时抛出疑问,引出问题,然后再去寻求理解”的过程。如下是在阅读LPDDR2的规格书JESD209-2F的第一节Scope时抛出的疑问。

我们看到文中提到了如下黄色部分的技术, 于是乎就想要了解一下其到底是什么?首先对SxA,SxB的这个数字2和4到底代表什么表示兴趣。

规格书后面也有简单的介绍,

LPDDR2-S2使用2n预取架构(2n prefetch architecture)。

LPDDR2-S4和LPDDR2-N使用4n预取架构(4n prefetch architecture)。

但是上文中后面的一堆文字怎么看都云里雾里不知所云,那么就引出了本文的主题,究竟什么是DDR的Prefetch Architecture。

这里搜到了镁光的一篇技术文档《TN-46-05 GENERAL DDR SDRAM FUNCTIONALITY》,里面的框图可以比较形象的解释。顺便提一下镁光的技术手册文档内容都是非常的不错,包括其数据手册也是学习DDR的不错的资料,可以去官网搜一搜看一看(https://www.micron.com/support下的Technical Notes目录下)。

DDR(或DDRI)应用2n预取技术,DDRII应用4n预取架构。

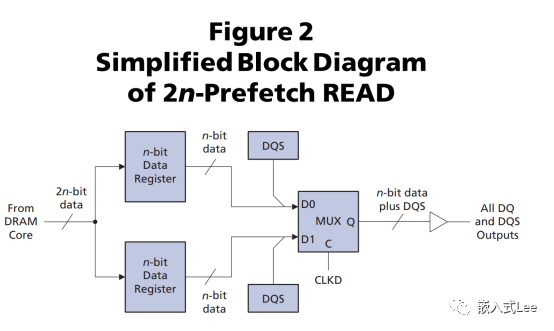

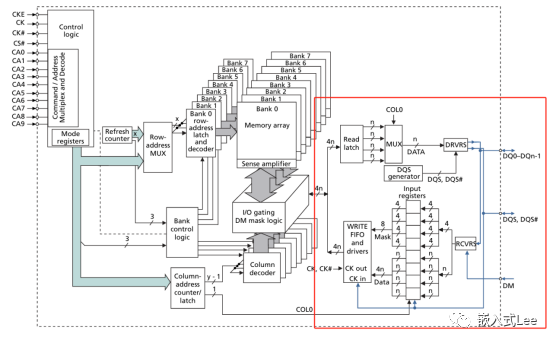

对于DRAM颗粒来说,2n预取即内部数据总线的宽度是外部数据总线宽度的两倍,因此内部列(column)访问频率可以为外部数据传输速率的一半。也就是说,对于设备内部的每个单读取访问周期,都会提供两个外部数据字(如图2所示)。

这里的”字”个人理解应该是颗粒外部总线宽度,即DQ宽度,不应该理解为通常意义的字,原文写的是word所以还是保留该说法。

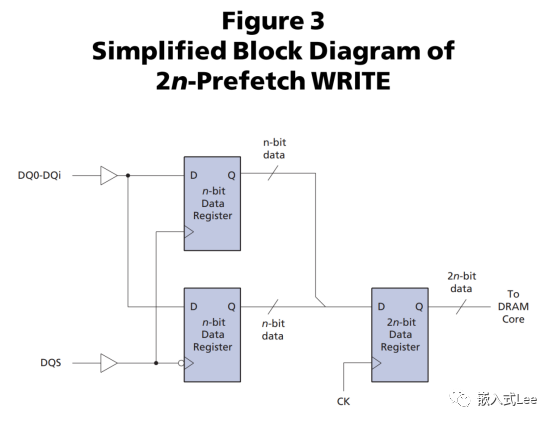

类似地,写入设备的两个外部数据字(DQ宽度)在内部组合并为一个内部访问写入(如图3所示)。

对用户从高层来看,2n预取意味着数据访问是成对发生的。即单个读取访问获取两个数据字(DQ宽度);对于单个写入访问,必须提供两个数据字(DQ宽度),和/或2个数据掩码位。这会影响最小burst大小传输和非最小burst传输的终止(BST命令)。2n预取架构的最小burst大小是两次外部数据传输。理解这些就可以理解手册中的burst length参数了。

总结一下就是相当于内部总线变宽了,是外部总线的两倍了,这个变宽是通过所谓的2n-Prefetch Architecture的架构实现的。 所以内部传输的单位即颗粒度就是外部总线DQ宽度的两倍,所以内部访问频率只需要外部总线频率一半,但是也要求外部总线访问必须要以2xDQ宽度为单位进行,因为内部访问2n预取架构不能拆分了。

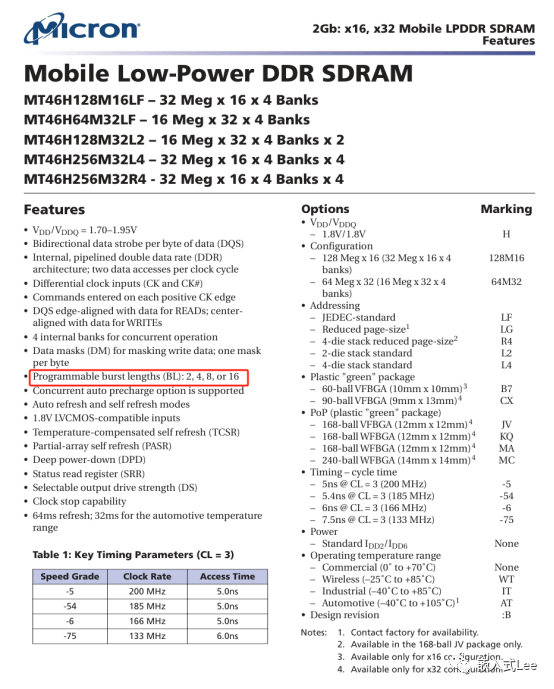

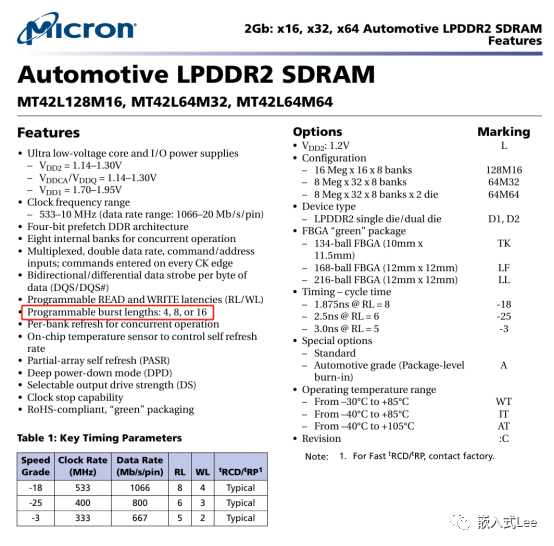

比如镁光某款DDR的burst length是2,4,8,16最低2.

某款LPDDR2的burst length就是4,8,16,最低4

某款LPDDR3的burst length就是8

和2n一样不再赘述,上个框图,见如下图右下角部分。

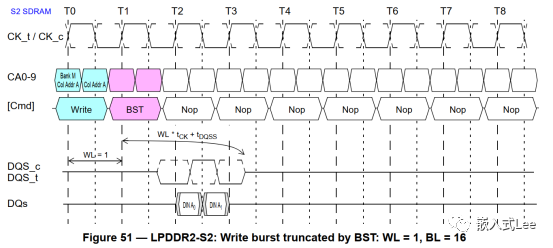

对于LPDDR2-S2设备,2位预取架构允许在写入或读取命令之后的任何周期中发出BST命令。

如下图所示,BST命令发出对应的始终上升沿后的WL个tCK加上tDQSS时间之后终止burst传输。注意已经发出BST命令之后即T1时刻之后,在新的读写burst之前不能再发BST命令。

所以图中burst设置为16想要传输16,实际传输2就终止了,即1x2(x2是因为一个时钟两个边沿都会传输),延迟了一个时钟终止。

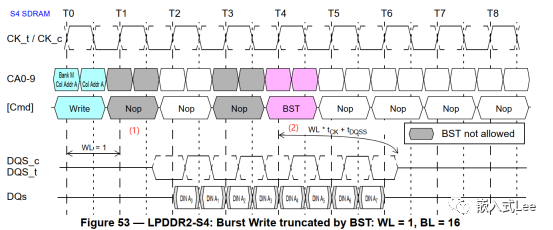

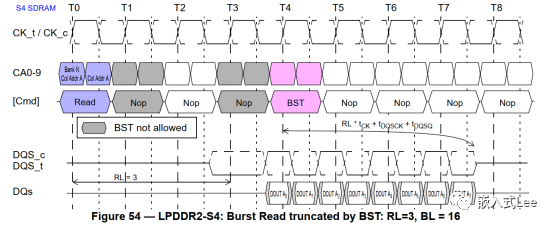

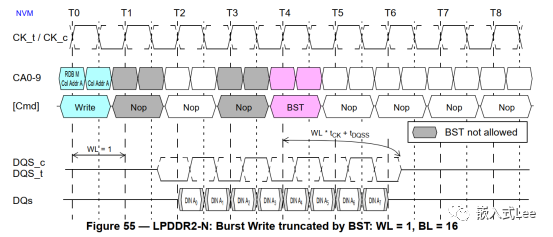

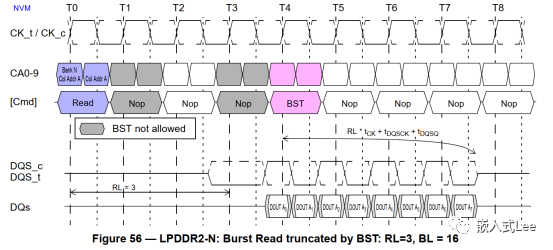

对于LPDDR2-S4和LPDDR2-N设备,4位预取架构,允许BST命令在写入或读取命令之后的偶数个时钟周期上发出。因此,被BST命令截断的读或写命令的有效burst长度是4的整数倍。如下如所示,不能在(1)处发送BST,必须在读写命令之后的偶数个时钟才能发,可以在T2处发,图中是在T4处发送,此时实际传输burst传输了8,即4x2(x2是因为一个时钟两个边沿都会传输),延迟了4个时钟终止。

同样注意已经发出BST命令之后即T4时刻之后,在新的读写burst之前不能再发BST命令。

读也类似

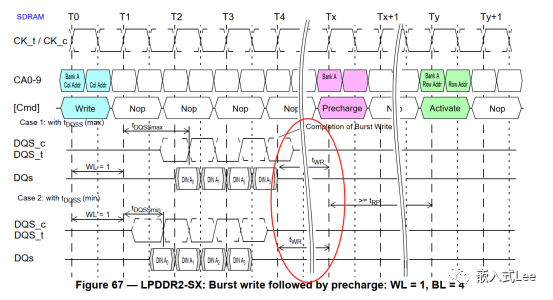

对于写入周期,从最后一个有效burst输入数据的时间到可以发出预充电命令必须满足一定延迟,该延迟即从burst写入完成到预充电命令的写入恢复时间(tWR)。在tWR延迟之前,不应向同一bank发出预充电命令。

LPDDR2-S2设备预取对为单位往阵列写入数据(prefetch = 2),

LPDDR2-S4设备以4倍预取为单位往阵列写入数据(prefetch = 4)。

内部写入操作的开始可以仅在预取组已经被完全锁存之后才开始。因此,对于LPDDR2-S2和LPDDR2-S4器件,写入恢复时间(tWR)在不同的边界处开始

对于LPDDR2-S2设备,到同一bank的最小写入到预充电命令间隔是WL +RU(BL/2)+1 +RU(tWR/tCK)时钟周期。

对于LPDDR2-S4器件,到同一bank的最小写入到预充电命令间隔是WL + BL/2 + 1 + RU(tWR/tCK)时钟周期。对于未终止的burst,BL是来自模式寄存器的值。对于终止的busrt,BL是有效burst长度。

如下图的tWR

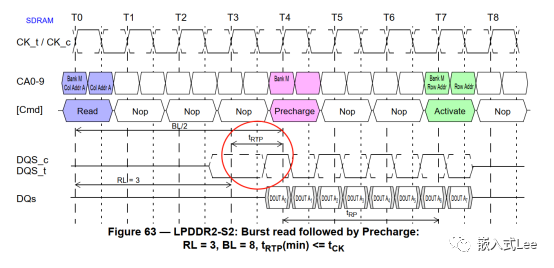

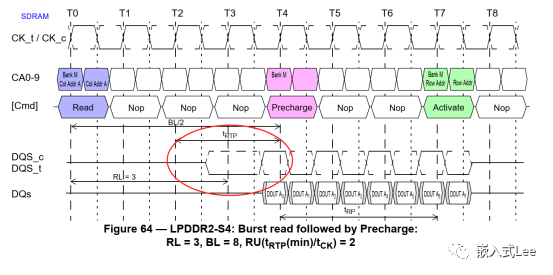

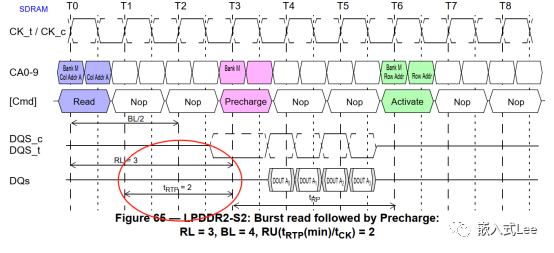

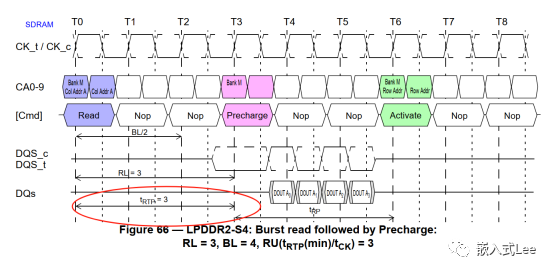

对于最早可能的预充电,可以在读取命令之后BL/2个时钟周期发出预充电命令。对于未终止的burst,BL是来自模式寄存器的值;对于终止burst,BL是有效burst长度。在行Row预充电时间(tRP)之后,可以向同一bank发出新的bank激活命令。在满足tRAS之后才能发出预充电命令。

对于LPDDR2-S4设备,读取到预充电最小间隔还必须满足,从启动读取命令的最后4位预取的时钟沿上升起的最小模拟时间。

对于LPDDR2-S2器件,读取到预充电最小间隔还必须满足,从启动读取命令的最后2位预取的时钟上升沿起的最小模拟时间。

这个时间被称为tRTP(Read to Precharge 读取到预充电)。

对于LPDDR2-S2设备,tRTP在读取命令之后启动BL/2 -1时钟周期。

对于LPDDR2-S4设备,tRTP在读取命令之后启动BL/2 -2时钟周期。如果BST命令或对另一bank的读取命令截断了burst,则应使用有效的BL(burst length)来计算tRTP何时开始。

1.从用户的角度看2n Prefetch Architecture颗粒内部数据总线是外部总线宽度的两倍, 4n类似。使得内部吞吐率增加了,以适配外部总线频率的提高,来提高速率。这也可以看到ddrx的x数字变高,该预取架构变大。

其实简单的类比到生活哲学,发现思想也是很朴素的,比如应生活需要,蓄水池放水速率要增加,于是可以对出水管加压或者加粗(提高总线频率),来提高放水速率,但是进水管受限于各种原因,要加压改造比较难(内部存储受限于物理固有特性工艺等,要提高访问频率较难),所以可以增加进水管数量(增加总线宽度)来提高速率。

2.xn Prefetch Architecture,使得最小burst length有要求,最小必须是x。同时4x预取 BST终止必须是命令之后的偶数时钟才能发。

3.Prefetch Architecture还影响一些命令的参数tWR,tRTP有影响,详见文中。