本文继续DDR Training系列的RX DQS Gating Training的介绍。

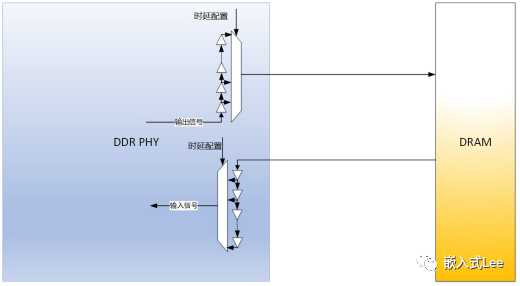

l所谓的Training即PHY调整输入输出两个方向的延迟,实现输入输出信号的时序调整,以满足收发要求。这里我们反向思维下为什么只能加延迟,而不能加快某一根信号,使得其和其他慢的信号匹配呢? 因为加延迟加缓冲电路即可,但是做不到加快信号的传输。

谈到RX DQS Gating Training需要先了解下DQS,DQ这几个信号。

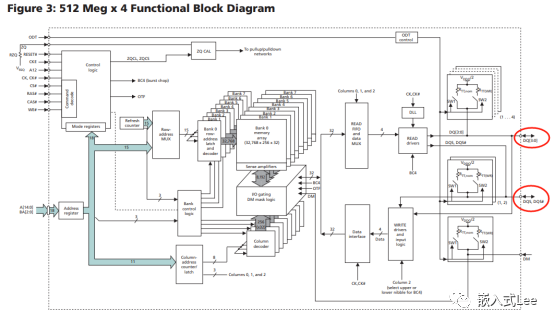

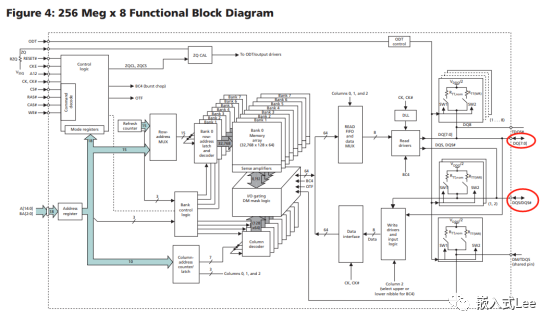

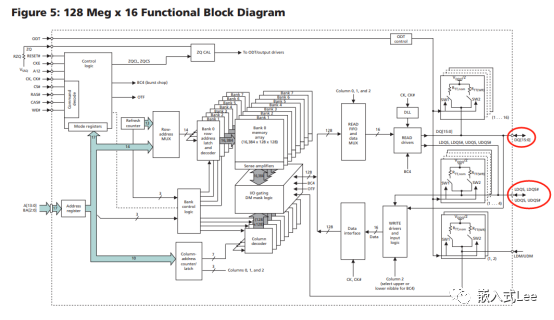

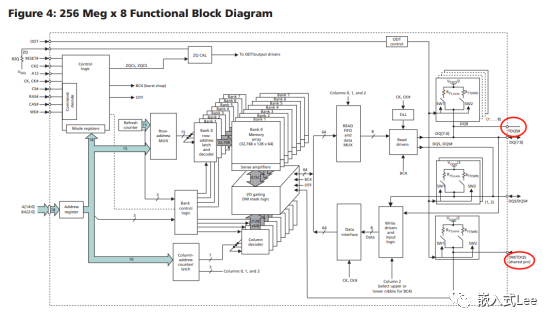

lDQ即Data input/output,双向数据总线,参考VREFDQ电压。DQ的宽度一般有x4,x8,x16几种。

lDQS/DQS# 差分对即Data strobe, 和读数据一起输出且边沿对齐,控制器在该信号边沿进行读数据采样,和写数据一起输出且和写数据中心对齐。对于x16模式,有LDQS和UDQS分别选择高低字节。

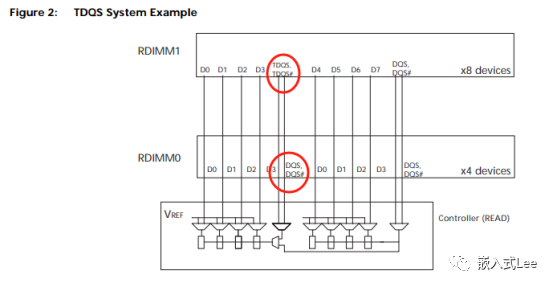

lTDQS/TDQS# 差分对即Termination data strobe,x8总线宽度的才有, TDQS和DM引脚共用,TDQS#引脚是独立的,所以使能了TDQS后就不能用DM。TDQS和TDQS#提供端接。(DDR3中加入该功能 MR1寄存器配置,只有x8模式才能使能,x4和x16需要关闭)。

应用于x8和x4混用的场景。

因为x8模式只要一组DQS提供端接,接两片x4则需要两组DQS端接(每片x4都要一组DQS),否则会端接不平衡,所以用TDQS来当另外一组端接。

TDQS与DDR2中的RDQS功能类似,但TDQS只提供端接。RDQS同时提供终端和输出脉冲output strobe。

参考《TN-41-06: DDR3 Termination Data Strobe (TDQS) Introduction》

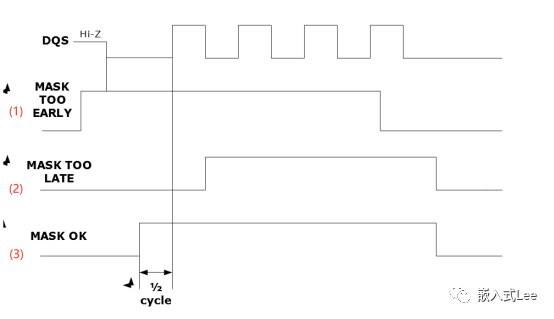

了解了DQS,然后再来看DQS Gating。顾名思义Gating就是门控,门控即MASK,即什么时候使能什么时候不使能。即决定DQS什么时候有效,什么时候无效的信号。

即DQS & DQS Gating决定最终的DQS的有效性。

前面我们介绍到了读数据是在DQS的边沿进行的,如果是受到干扰错误的DQS脉冲过来就可能错误的读数。

读操作时,DQS信号在前导(preamble)前是高阻态,同时DQS信号的前导部分也不能达到最稳定的状态,所以需要过滤掉前面的高阻态和前导,恰好得到整个Read Burst操作的有效DQS,这就是读DQS gatetraining。

如下图所示,在DQS没有驱动高阻态时容易受到干扰产生错误的DQS信号,也就是控制器可能会错误的读到数据。所以控制器需要额外产生一个信号DQS Gating来确定DQS当前是否有效。这个有效时间理论上刚好覆盖需要的DQS周期即可,这样可以减少受干扰区间,实际上需要前面多一点,后面再多一点,才能保证不丢失DQS。

比如如下

(1)DQS Gating太靠前了,前面有错误的DQS进来了,容易误读。

(2)DQS Gating太靠后了,丢失了DQS,即丢失读数。

(3)DQS Gating超前第一个DQS边沿前面一点点 1/2个cycle,刚刚好。

目标就是要调整到(3)这种情况。

以下以microchip的一款控制器为例,其他的也大同小异

参考《https://onlinedocs.microchip.com/pr/GUID-FF8061A7-7A15-470F-A6F5-E733C24D85F0-en-US-3/index.html?GUID-08CA0D56-360C-4362-A821-DEB5B791F178》

DDR子系统的初始化和Bring-Up一般过程如下:

该步在Write Leveling后进行

DFI Initialization->DRAM Initialization->ZQ Calibration->Write Leveling->DQS Gate Training->Read Data Eye Training->Write Calibration->Simple Burst Write->Simple Burst Read

1.控制器通过使能DFI_RDLVL_GATE_EN启动DQS Gating Training。控制器必须发MRS命令去关闭前一步的Write Leveling,即将MR1(对于DDR3/4)/MR2(对于LPDDR3)位7置0。

2.控制器将MR3的位2置1,以便DDR3和DDR4 SDRAM的MPR(多用途寄存器)输出到DQ总线流上。即让DDR输出一个固定数。

3.控制器设置DFI_RDLVL_GATE_EN = 1,并等待dfi_rdlvl_resp。当检测到DFI_RDLVL_GATE_EN = 1后, IP的Training模块启动DQS Gating training算法。

4.IP的Training模块设置DQS_GATE Gating信号,使得其和DQS,满足前一节图中(2)的情况。

那么如何知道Gating信号是正确的呢,怎么知道它是对准的第一个DQS边沿,提前1/2 cycle呢,实际是通过不断调整Gating的相位,直到读到的DQ总线上的值和MPR寄存器的值一样,说明设置正确。此时IP设置采样DFI_RDLVL_RESP = 1后,软件读到采样DFI_RDLVL_RESP = 1后设置DFI_RDLVL_GATE_EN = 0,结束Training。

5.对于DDR3/4,控制器必须将0写入MR3位2,才能恢复DQ总线上的正常数据流。(MR3位2 = 0 >正常数据流;MR3位2 = 1 > MPR数据流)

注意:对于DDR3/4,控制器必须发出常规的READ命令才能从MPR读取数据。对于LPDDR3,控制器必须发出模式寄存器MR32或MR40。读取之间的时间必须至少为62 SYS_CLK周期长,这样IP的Training模块才能稳定。在MPR读取过程中的DFI READ时间必须与正常的数据读取操作相同。在DQS Gate Training过程中,DFI_RDDATA_VALID时序没有Training。

总结一下training的核心思想是:总线上输出固定数据,调整gating信号的相位然后去读总线数据,读到正确的数据则training通过,当然还有很多算法细节和实现细节。

Try一下是training领域的圣经,几乎所有的training算法都是该思路,只是具体如何try涉及不同的实现算法。