最近在做DDR traing相关的驱动,对相关的概念进行一些整理。本文着重介绍ZQ校准相关的内容。

随着DDR的频率越来越高,性能越来越强,为了更稳健的系统操作,DDRn SDRAM驱动器做了一些增强设计,以下是针对DDR3。

l减小电容,这点好理解, 因为电容大导致充放电时间慢, 信号边沿就迟缓,不能满足高频要求。

l动态on-die端接电阻(ODT), 能够调整ODT来适应外围的实际电路,以满足信号的完整性要求,减小阻抗失配,减小信号的反射和振铃。

l校准机制。

以上其实现是使用新的“merged”驱动来完成的,组成该类型输出驱动器的电路是共享的(什么是共享见后面的分析),以用于实现动态ODT等。区别于DDR2的输出驱动器和端接电阻采用了单独的结构。

我们来看校准机制,那么校准到底是校准什么呢?

1.要先明确对象!

芯片内部有240欧的电阻网络来组合实现不同的端接电阻,但是该电阻受到PTV(制程,温度,电压)的影响,所以需要对其进行校准。一般是工艺本身会导致偏差,然后温度电压等会导致运行时动态偏差,针对这两种一般有初始化时间长的校准,和运行时时间短的校准。

2.其次要明确怎么校!

既然能校肯定电阻要是能改变的,如何实现电阻改变呢? 初中我们学习过串联并联都可以改变阻值,DDR也是这么干的,其实牛逼的技术往往就是这么朴素,常说的小学生都懂不是没有道理的!

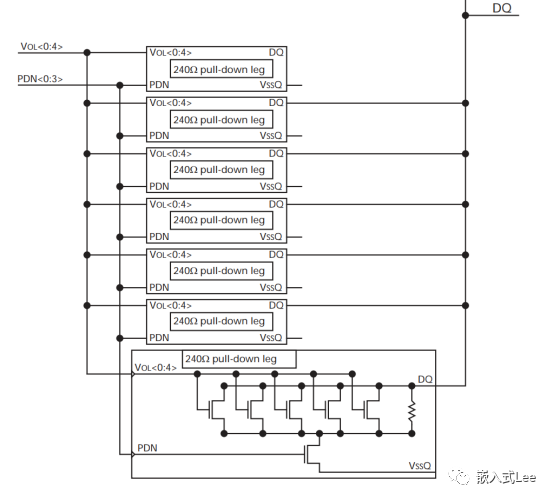

芯片内部通过一组CMOS和240欧电阻并联, CMOS关闭时阻抗很大相当于并联一个很大的电阻对最终阻值影响不大,当CMOS打开时电阻变小和240欧电阻并联结果就会小于240欧,打开的并联CMOS越多则最终阻值最小,这样就实现了电阻的调整。

所以这里电阻实际只能调小的,那么要得到准确的240欧,正常应该是要设计多留点余量保证默认是大于240欧的(这点本人不是专业人士,只是猜想,后面证实猜测是正确的,如下图)。

那么我们反向思维下,上学时老师可能不喜欢刨根问底的学生,认为是天生反骨调皮捣蛋,但是工作之后我们一定要有这种思想! 为什么不设计成既有串联,又有并联呢?这样就既可以调大又可以调小,多好是不是很完美? 其实初中的电阻串并联公式已经告诉我们答案了,串联就是电阻相加,那么调整步进就是串联的电阻的大小,对于调整肯定是微调(如果不是微调那就要去考虑工艺问题了,你差的太大了还调个啥劲!),但是这个电阻由于工艺等原因不能做的很小,且越小误差百分比越大,所以串接就不适合微调,并且串联的话电路设计也没有并联简单这点就不深入讨论了。 而并联根据公式,并联一个大电阻就可以改变较小的阻值,适合微调。

3.既然能够调整了,那怎么调,并联几个CMOS,怎么算是调整到位了,连环夺命追问有助于帮助思考问题 ! 可以自然想到,那就需要反馈。不能一顿操作猛如虎,最终阻值差了二百五。 实际我们就是要测量调整后的电阻是多大,是不是240欧, 那么怎么测呢,用万用表测呗,再不够我们用LCR测量仪测呗。芯片也是这么干的,你看多自然,好比把一头大象塞入冰箱需要几步一样的容易,只需要打开冰箱门把大象塞进去就好了! 芯片就是在内部又设计了一个”万用表”, 你看看万用表的原理是啥,不就是电阻分压,再测电压吗, 再高精度可能用到桥式电路,但是本质还是电阻分压测电压。 那么DDR芯片中也是这么干的。 ZQ引脚就是用来分压用的, 当然有UP和DOWN端, 对于UP端就需要从对应的ZQ引脚下接一个240欧电阻。 这样内部240欧电阻和外接240欧电阻对VDDQ,VSSQ之间的电压分压,用外接电阻来校准内部电阻。 这样需要外部电阻精度高一般要求±1%,要求VDDQ稳定,抖来抖去会让内部比较器精神分裂的! 对分压点电压采样,当电压为VDDQ/2时说明电阻准确,实际是和内部参考VDDQ/2电压比较即可,无需得到具体的ADC值。

如果电压小了,说明内部电阻大,则多并联CMOS来减小电阻。

为了满足DDR3的数据速率,必须注意信号的完整性。尽量减小存储器控制器连接到DRAM输出的路径上的阻抗失配,有助于减少信号上的反射和振铃。为了减少这些阻抗不连续性,就必须保证ODT的准确,DDR3中引入了精确校准方案,来保证内部电阻的精度最终实现ODT的精度,所以费这么大功夫是值得的也是必须的。

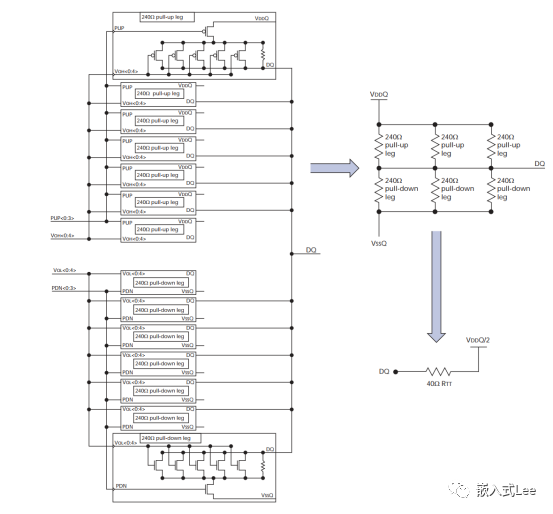

上面提到了各种功能实现都是依赖于“merged”驱动, 现在就来看看这个神秘的驱动结构到底是什么样的,先上框图! no tu no bi bi,能用图说话的地方就用图,更形象。

我们来看上图,上下两部分,上面是pull-up部分,下面是pull-down部分。原理都是一样的。

只是pull-up需要用PMOS,所以叫做PUP, pull-down部分用的NMOS所以叫做PDN。

一些英文术语缩写知道其整个单词有助于理解记忆。

我们先来看最终效果,即需要实现指定的端接电阻ODT,这是通过电阻网络实现的,无非就是电阻串联并联嘛! 初中老师教的。

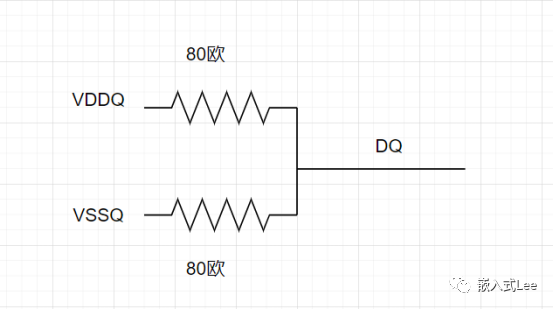

比如我们需要实现40欧的端接电阻那么怎么办,40就是两个80欧的并联。

如下形式即可,即上下拉都是80欧,然后等效端接就是并联40欧。

那么怎么得到上下拉的80欧呢,3个240欧并联刚好就是80欧,完美! 不过实际总是有遗憾的,不会这么完美,遗憾也是美嘛。对于DDR3,全强度驱动器的输出阻抗默认为34Ω,通过启用所有七个240Ω电阻并联就可以配置为该ODT。

所以从上图可以看到,有两个寄存器

PUP<0:3> 控制4个上拉电阻的的使能。

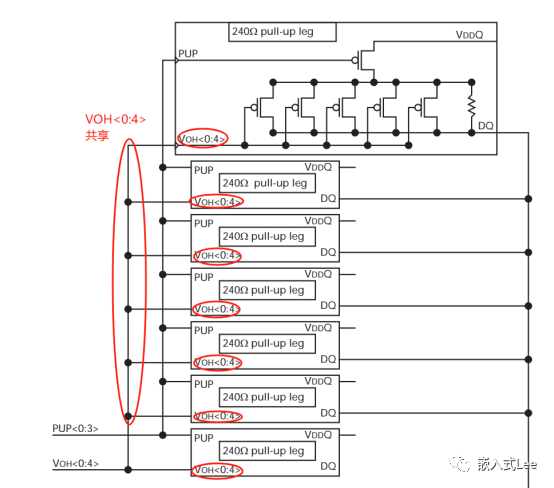

VOH<0:4> 控制5个上拉CMOS的开关,用于校准内部240电阻。可以看到所有的上拉电阻都是共享一个VOH<0:4>的,也就是文章开头那里提到的共享。

上图中第一个PUP是详细的结构,下面的6个是一样的所以是简图。

但是PUP<0:3>应该只能控制4个PUP为什么上面画了7个PUP???

PDN也是类似,就不再赘述

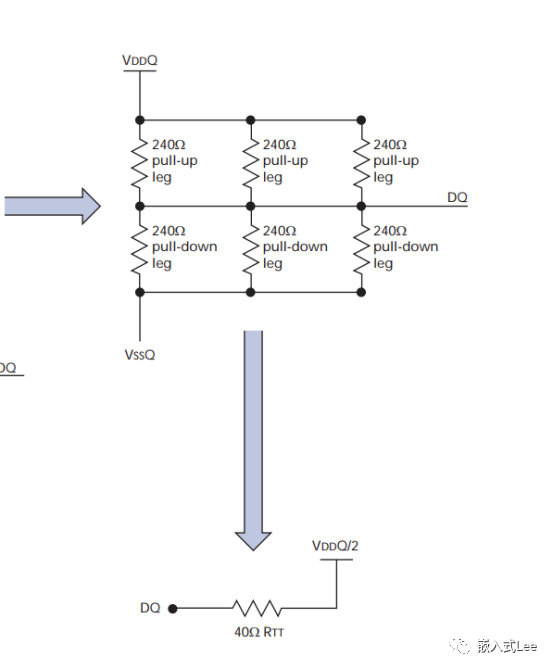

上面实际已经初步解释了校准的原理,但是文字说来不是很形象,继续上框图!

DDR3中的ZQ校准同时应用于输出驱动器和ODT。每个DRAM的ZQ引脚连接到一个外部精密(±1%)240Ω电阻。只要不同控制器不同时校准,即不同时使用该外部电阻,且只要电容负载不超过规范,该电阻就可以不同控制器共享。

如上所示,以pull-up为例,校准就是控制VOH<0:4>

来控制5个CMOS的开关,来和内部240欧电阻并联微调阻值。 并联的电阻一起和外部的240欧电阻分压,分压点的电压VPULL-UP和VDDQ/2比较,如果小于VDDQ/2则说明内部电阻过大,还需要增加打开的CMOS个数。 图中没有画出这个比较器的结构,实际前面还有一系列结构:模数转换器(ADC)、比较器、众数滤波器(众数即出现频率高的数,毕竟我党也是遵循小数服从多数的原则的,搞技术也是可以上升到搞政治的觉悟的,时刻保持对自己的高要求!)、内部参考电压发生器和近似寄存器(用于存储VOH值)等。

校准一般都可以自动完成,能自动挡的谁还开手动挡呢,太累!软件配置使能等待结束即可,结果就到了寄存器。有些控制器也可以手动配置VOH寄存器来手动校准,这样可以直接使用之前校准过的值直接设置, 毕竟开飞机也不能一直自动挡不,灵活驾驶乐趣还得看手动挡。

与DDR2相比,DDR3 ZQ校准方案,提供了可控阻抗值的改进和明显更严格的公差。初始化时的长校准使DRAM能够最大限度地减少驱动器中存在的任何工艺变化。正常操作期间的短校准减少了由于电压和温度漂移引起的阻抗变化。这种精度有助于最大限度地减少PCB迹线和驱动器之间的阻抗不连续性,并提高整体信号完整性

以下内容翻译自参考文档,即美光相关的控制器和DDR,其他厂家的可能不一样,大部分机翻,瞅一眼就行了,不是本文的招牌菜。

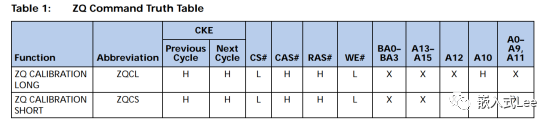

DDR3中引入了两个与ZQ校准相关的新命令

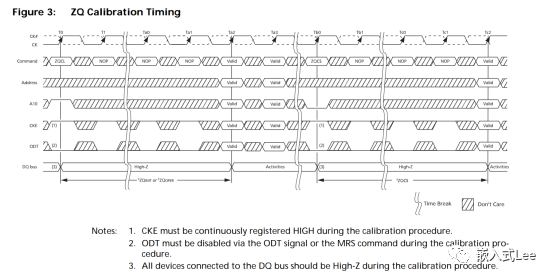

1.ZQ CALIBRATION LONG(ZQCL)命令最常用于初始系统通电或设备处于复位状态时。ZQCL命令解决了制造工艺变化的问题,并将DRAM校准到初始温度和电压设置。使用ZQCL命令的完全校准需要512个时钟周期才能完成。

在此校准时间内,内存数据总线必须保持完全空闲和安静。在初始校准之后DRAM空闲的任何时候,都可以发出后续的ZQCL命令。对于这些后续命令(在初始化和复位以外的时间发出的命令),完成校准所需的时间窗口减少到256个时钟周期。

2.ZQ CALIBRATION SHORT(ZQCS)命令跟踪与正常操作相关的连续电压和温度变化。周期性短校准使DRAM能够在整个电压和温度范围内保持线性输出驱动器和端接阻抗。ZQCS命令需要64个时钟周期才能完成

在RESET之后第一个ZQCL必须保证tZQINIT(512个时钟周期)的定时周期以执行完全校准。对于任何后续的ZQCL命令,必须允许tZQOPER(256个时钟周期)的定时周期。ZQCL命令可以在阻抗误差大于ZQCS命令所能校正的阻抗误差的任何时候使用。同样,在tZQINIT和tZQOPER时间窗口期间,DRAM通道必须保持完全安静。

ZQCS命令可以在DRAM不执行活动的任何时候发出。在可以恢复正常操作之前,必须满足64个时钟(tZQCS)的较短定时窗口。

在控制器发出任何校准命令之前,必须对所有banks进行预充电并满足tRP要求(参见第4页图3)。当退出自刷新时,ZQCL或ZQCS命令可以在t XSDLL时间内发出。自刷新退出时必须发出明确的校准命令,以便进行I/O校准。自刷新退出后,必须满足tXS,然后才能发布ZQCL或ZQCS。

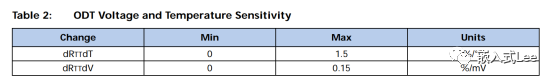

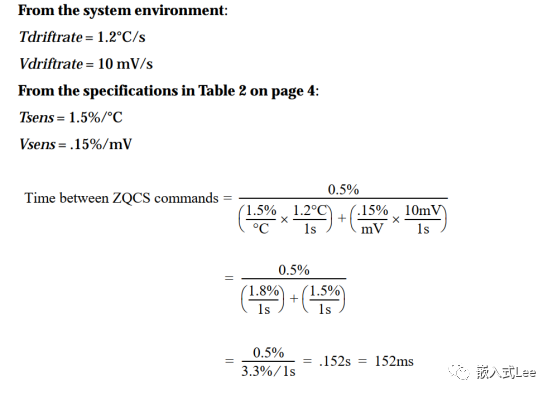

ZQ校准命令的频率将取决于系统温度和电压漂移率。为了保持线性输出驱动器和端接阻抗,控制器需要以特定的间隔发出ZQCS命令,以考虑轻微的系统环境变化。

用于确定这些定时间隔的一种方法是使用DRAM在应用中所经受的温度(Tdriftrate)和电压(Vdrift rate)漂移率。如表2所示,除了系统特定的漂移率外,设计还应假设DDR3规范中的最大ODT电压和温度灵敏度。

DRAM能够在64时钟周期(ZQCS命令周期)内校正0.5%的阻抗误差。这个数字以及系统漂移率可以在下面的公式中用于计算校准间隔。

注意:Tsens和Vsens是表2中的最大温度和电压敏感度。值仅用于插图目的。请参阅当前规范的组件数据表。

计算样例

为了保持RON和ODT的准确性,对于本例中的系统,ZQCS命令之间的最大时间量为152ms。要确定时钟数,请除以tCK。

以下是某一个具体的DDR控制器说明,仅作参考

ZQ校准是PHY的一个功能,用于校准驱动输出的阻抗和DDR IO的晶片端接电阻。

ZQ校准在PHY初始化之后进行。

使用ZQ校准功能需要在PHY的ZQ引脚和VSSQ引脚之间接一个120Ω±1%的电阻, ZQ引脚的负载电容必须小于3pF。

以上电阻精度有要求是为了保证分压的精度,而负载电容的要求是要保证分压后电压采样速度,电容大则需要较长时间电压才能稳定影响采样速率。

1.PHY初始化之后, 配置reg_zqcali_en为1,使能校准模块。

2.等待reg_zqcali_done完成置高。

3.配置reg_zqcali_en为0关闭校准模块。

4.配置reg_a_l_dq_drv_zacali_en/reg_a_h_dq_drv_zacali_en;reg_a_l_dq_odt_zacali_en/reg_a_h_dq_odt_zacali_en为1以使用校准结果(默认是使用寄存器默认值)。

可以使用校准值,也可以使用寄存器值。上述是自动校准后使用校准值即相应的_en位为0.

如果之前已经校准过,之后又由于频率改变等原因将PHY复位了,则需要调整,则可以读出已经校准的寄存器值,然后写回,并配置_en位为0,使用寄存器值。

1.校准后,读出以下寄存器校准值drvlegpd_zacali_2reg[4:0]/drvlegpu_zacali_2reg[4:0];odtlegpd_zacali_2reg[4:0]/odtlegpu_zacali_2reg[4:0]

2.频率改变等原因复为了PHY

3.设置eg_a_l_dq_drv_zacali_en/reg_a_h_dq_drv_zacali_en;reg_a_l_dq_odt_zacali_en/reg_a_h_dq_odt_zacali_en为0以使用寄存器值。

4.将之前保存的寄存器值重新写入drvlegpd_zacali_2reg[4:0]/drvlegpu_zacali_2reg[4:0];odtlegpd_zacali_2reg[4:0]/odtlegpu_zacali_2reg[4:0]

所以驱动接口设置为,根据参数决定是使用寄存器值还是使用自动校准,如果传入的参数标志为自动校准,则使用自动校准,否则使用寄存器值配置。并提供缓冲区指针做欸参数,自动校准则回写校准值,如果是配置寄存器则传入需要配置的寄存器值。

int ddr_zq_calibration(int flag, uint8_t* cfg);

《TN-41-02: DDR3 ZQ Calibration Introduction》

一切尽在”酒中”,哦不文中,这里就不总结了,占个位置。