设计出色功效的电子应用时,需要考虑使用新型高性能氮化镓 (GaN) 和碳化硅 (SiC) 技术的器件。与电子开关使用的传统硅解决方案相比,这些新型宽带隙技术具有祼片外形尺寸小、导热和热管理性能优异、开关损耗低等显著优势,非常适合工业、医疗、通信和车载应用电源、驱动器和逆变器等空间受限的应用。

不过,设计需要考虑一些利弊关系,特别是开关损耗。例如,di/dt 和 dv/dt 提高,开关速度加快,电路频率振荡放大,使噪声成为重要考虑因素。

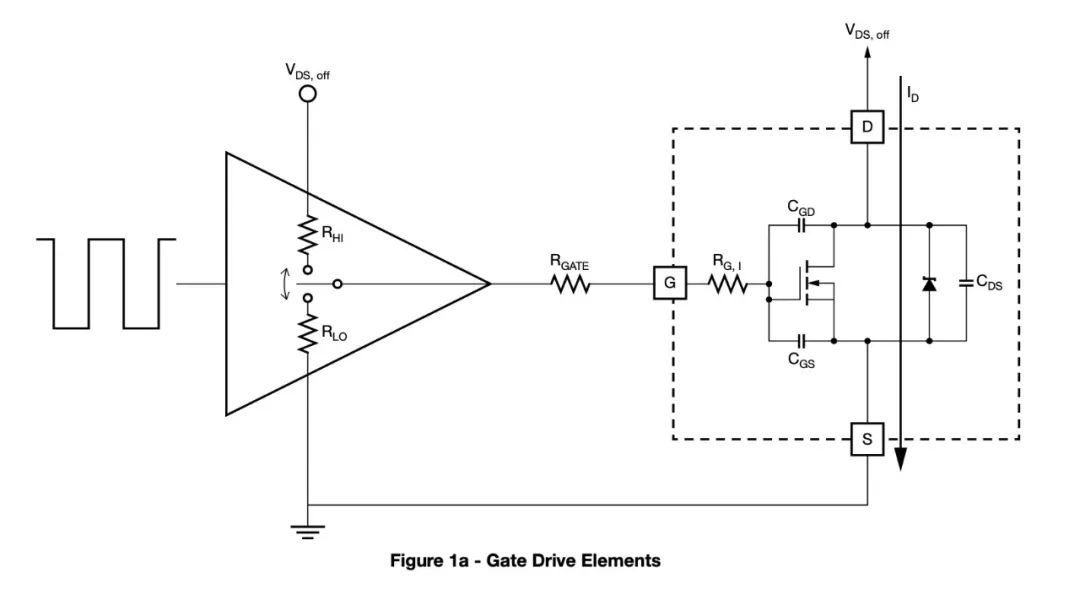

典型电路功能中,高边 (HS) 和低边 (LS) MOSFET 用作开关器件驱动电感负载。在 HS 开关导通,LS 开关关断时,电流从电源 Vcc 流向电感器 Lo。反之,在 HS 开关关断,LS 开关导通时,电感器电流继续从接地端同步流向 Lo。导通/关断状态由栅极电压定义,栅极电压的变化影响栅极回路的充放电。开关时间和相关损耗取决于栅极电容通过栅极电流充放电的速度。栅极电流受驱动电压栅极电阻和驱动电路整体寄生效应的影响(图1a)。

图1a:栅极驱动电路元件

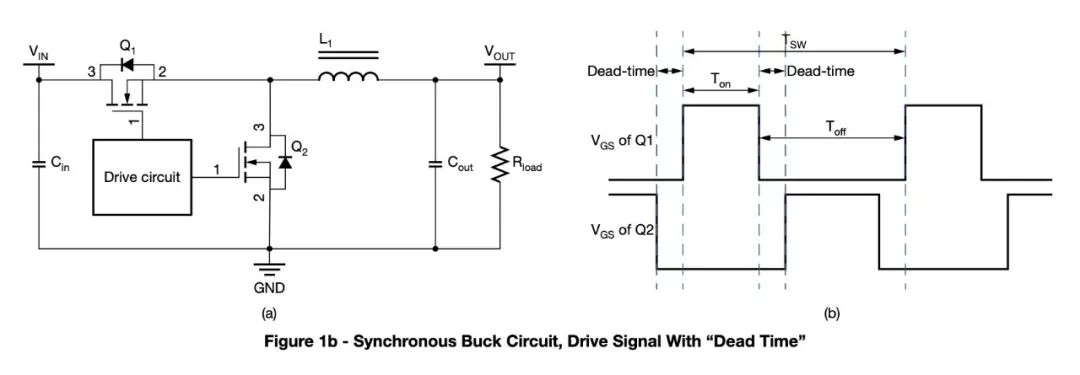

为了避免同时导通/关断,需要认真选择栅极电阻解决方案,如高功率厚膜片式电阻、薄膜 MELF 或高功率背接触电阻。这类解决方案不需要延长有效转化为功率损耗的“死区时间”(HS 和 LS 开关导通之间的时间间隔)(图1b)。

图1b:同步降压电路,带“死区时间”的驱动信号

图1b:同步降压电路,带“死区时间”的驱动信号

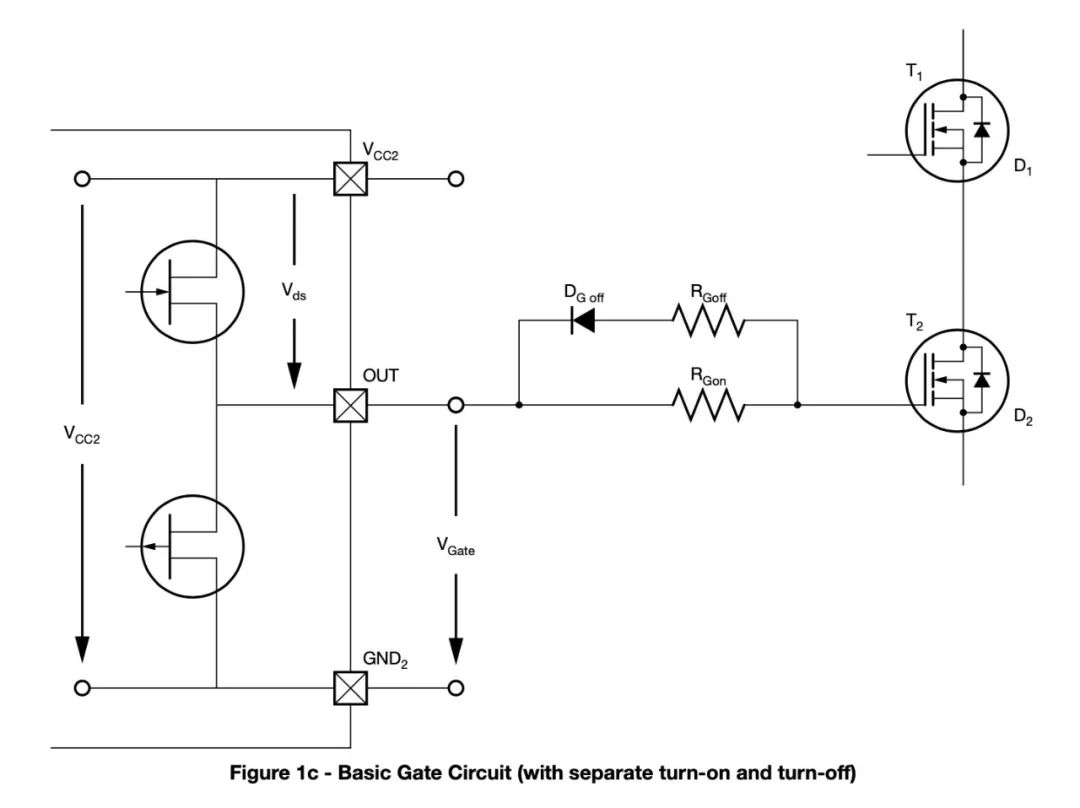

选择栅极电阻技术的基本考虑因素主要包括脉冲功率、脉冲时间和温度以及稳定性。使用两个栅极电阻时,通常建议导通栅极电阻值至少是关断栅极电阻值的两倍(图1c)。重要的是注意关断栅极电阻值,避免漏极(或 IGBT 情况下,集电极)电压上升发生寄生导通。

图1c:基础栅极电路(独立导通和关断)

图1c:基础栅极电路(独立导通和关断)

同时,还要考虑栅极电阻的阻值,阻值过高或过低都会发生损耗或振荡。栅极电阻要求能够承受短时间高峰负载,平均功耗随频率和占空比而增加。在功能上,电阻能够对器件内部寄生电容放电并进行 Miller 充电。减小电压过冲可以降低器件和驱动器的应力,减小寄生电感可以避免开关过程产生 VGS 振荡。 为了尽量减少电路中的噪声,缩短布线长度(减小寄生电感)很重要。因此,通常首选打线或表面贴装栅极电阻。采用 IGBR 打线电阻的情况下,背接触具有优异导热性,并最大限度减小器件与 PCB 之间的热梯度。在连接、外形尺寸和烧结能力方面,IGBR 电阻在打线连接,小尺寸以及烧结能力方面的综合性能可以让其更灵活地内置于高功率半导体模块或封装。这样电阻可以在布局上非常接近开关器件,从而减少部分寄生元件,有助于降低电路噪声。

栅极电阻涵盖多种技术解决方案,包括高功率厚膜片式电阻 (a)、薄膜 MELF 电阻 (b) 和额定功率达 4 W 的薄膜衬底电阻 (c)。栅极电阻选型的其他考虑因素包括元件尺寸、精度、可靠性、元件与 PCB 之间的热性能以及并联寄生电感。

图2. 栅极电阻类型

栅极电阻的阻值 (RG) 通常为 1 Ω 至 100 Ω 之间。选择较低的 RG 值可以减少器件功耗 (EON, EOFF),但也会导致驱动电流增加。宽带半导体器件上升时间短,因此还要考虑栅极电阻的 RF 影响,平衡开关损耗与 EMI(电磁干扰)性能。如想减少 EMI,可使用更高阻值的电阻,延长开关上升时间,但这自然会增加开关损耗。

根据电源电路的电感和负载,不同电阻技术解决方案的最大工作电压也是重要的考虑因素,因为开关过程会出现电压脉冲。通过考虑所有这些因素,可以选择适用的栅极电阻解决方案,满足功效、可靠性和降噪方面的特定要求。

为满足瞬态的高峰电流(可达到两位数电流) 和高频 (有时甚至瞬间达到 MHz )的要求,工作温度对电阻就显得尤为重要。高温会造成阻值漂移并且漂移会随着时间增加。阻值的长期稳定性由器件结构决定。

例如,与片式电阻的矩形电阻区域相比,MELF 电阻的圆柱体电阻区域面积扩大了 π 倍,可显著提高抗脉冲性能。NiCr 之类稳定薄膜材料也具有出色的抗脉冲负载性能。在空间受限的设计中,电源开关的相对位置很重要,因为热量可从电源开关流入 PCB,从而影响栅极电阻的工作温度。

如果您想充分利用宽带隙半导体器件的功效优势,需要考虑栅极电荷 Qx、开关频率、驱动峰值电流以及快速开关时开关的高准确性和稳定性的具体要求,设计最佳栅极驱动电路。正确选择具有相应技术和器件结构的低阻值栅极电阻对于实现最佳电路效率至关重要。