延续摩尔定律的三维堆叠晶体管概念,其背后有北京大学的原创贡献。早在2000年前后北京大学就已经提出了三维堆叠互补晶体管(3D Stacked CMOS)的概念,并在2004年研发完成堆叠互补晶体管的雏形,发表了论文和申请了专利,只是概念太过超前,没有引起太多关注。 当下摩尔定律放缓,堆叠晶体管概念重获关注,imec于2018年提出了堆叠互补晶体管的微缩版CFET,英特尔(Intel)和台积电(TSMC)也都适时跟进。IEDM2021大会,英特尔的邀请报告中就引用了北京大学的该篇论文。 IEDM2023年将有更多有关三维堆叠晶体管的论文。 |

自从集成电路发明以来,集成密度的提升一直是业界持续追求的方向,也是“集成”的含义所在,集成密度的提升不仅可以提高芯片性能,实现更低的功耗和更高的效率,还可以有效降低生产成本。

提升集成密度的方式多种多样,增加芯片面积、异构集成封装,但缩小器件的单位面积是最根本也是最有效的途径。可以说,过去60多年影响最深远的就是晶体管的发展。

笔者自踏入集成电路产业圈子时,20多年来一直听到警示:随着集成电路器件的特征尺寸缩小到纳米尺度,各种基本的和实际的限制开始出现,传统的建立在体硅衬底上的 CMOS 技术正遭受前所未有的挑战,晶体管的尺寸极限即将到来,摩尔定律也将随之失效。然而年复一年,依靠创新,业界持续在推动半导体行业进一步发展。尽管困难重重,但经过各种努力,CMOS技术已经推进到10纳米及7/5/3/2纳米技术节点。

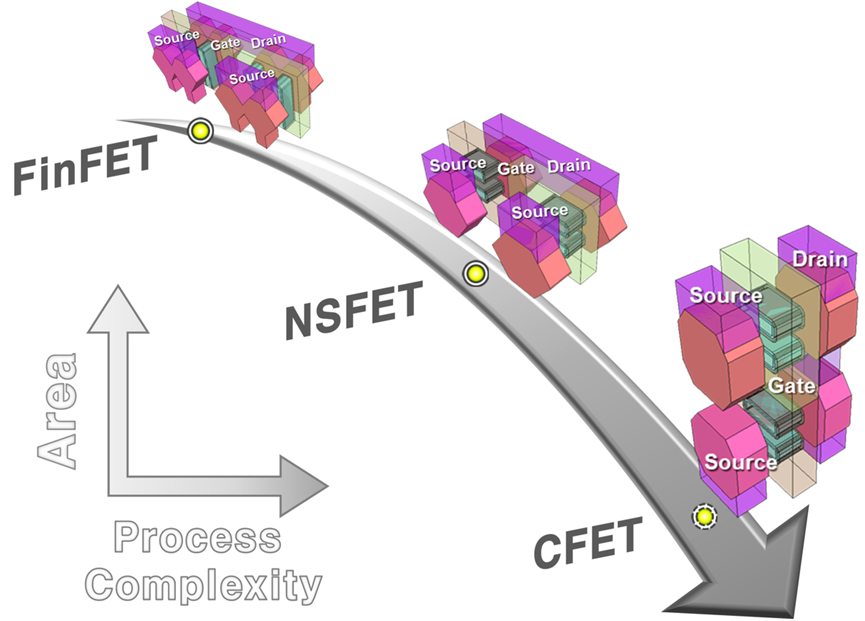

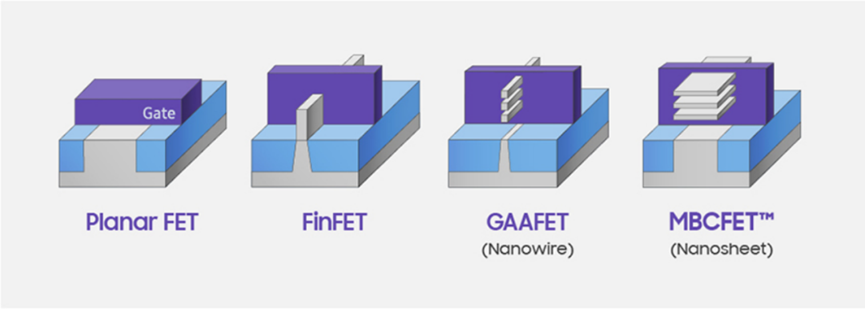

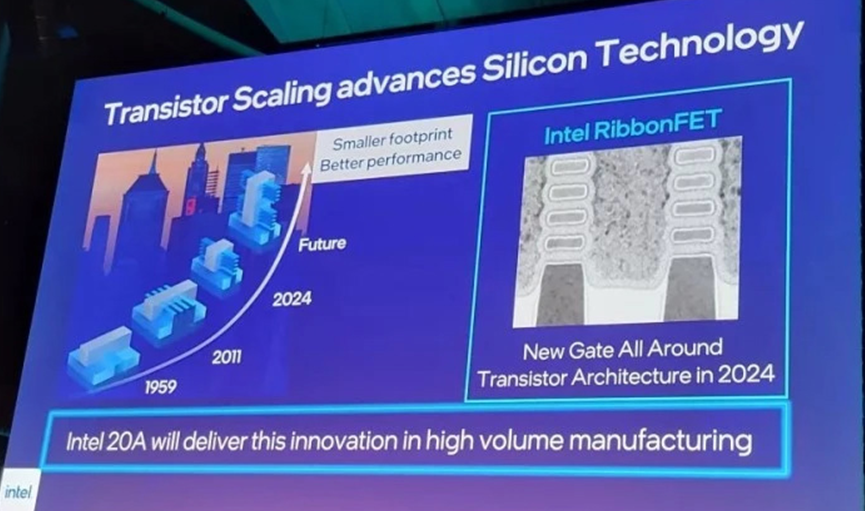

晶体管演变的历程:从Planar FET到FinFET到GAA(MBC)(图片来源于网络)

晶体管演变的历程:从Planar FET到FinFET到GAA(MBC)(图片来源于网络)

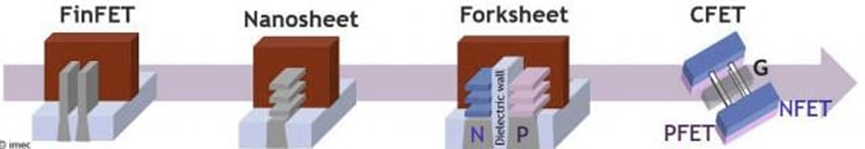

从平面晶体管(Planar FET),到鳍式场效应晶体管(FinFET,Fin Field-Effect Transistor),再到全环绕栅或围栅(GAA,Gate-all-Around),都是为了减少漏电,降低功耗。

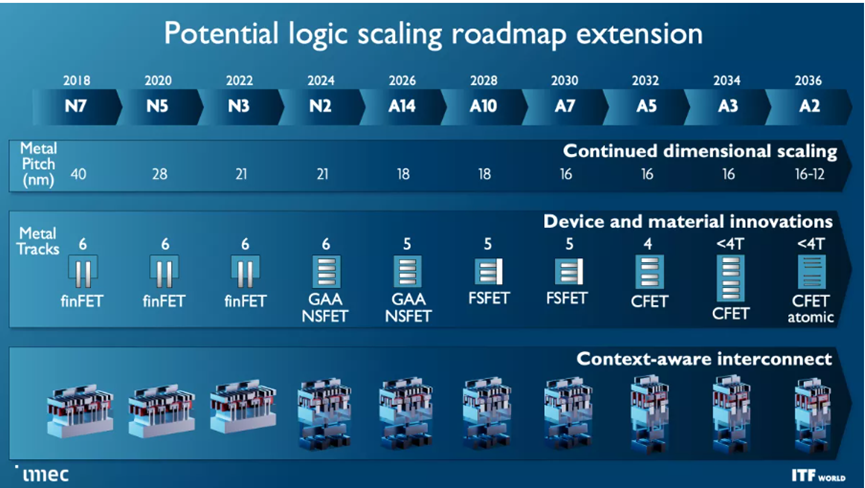

因为GAA晶体管架构的能力有其局限性,单个器件的结构形式优化已经几乎推至极限,要有新的结构来支持下一代工艺。于是在VLSI 2018技术会议上,imec发表的论文《The Complementary FET (CFET) for CMOS scaling beyond N3》中提出互补场效应晶体管(CFET,Complementary FET)概念。CFET采用Nanosheet结构,将一个p型Nanosheet FET叠加在一个n型Nanosheet FET之上,形成三维晶体管,可以显著增强晶体管性能,并减小其尺寸。英特尔(Intel)和台积电(TSMC)等产业三巨头适时跟进,CFET成为未来1纳米的发展利器。IEDM2023会议上英特尔(Intel)和台积电(TSMC)将发表有关CFET产业化进展的论文。

CFET源于北京大学的3D stacked CMOS

说起来,最近非常火爆的堆叠晶体管概念,其背后有着北京大学的原创贡献。早在2000年前后,北京大学的张盛东博士就已经提出了堆叠互补晶体管(stacked CMOS)概念,并在2004年开发完成堆叠晶体管的雏形,以一作身份在 IEEE Electron Device Letters ( Volume: 25, Issue: 9, September 2004,P661-663)发表了论文《A stacked CMOS technology on SOI substrate》。据笔者调研,这是世界上首次报道堆叠互补晶体管的概念和实验成果,同时还以第一专利权人在国内申请了专利《一种位于SOI衬底上的CMOS电路结构及其制作方法》。

《一种位于SOI衬底上的CMOS电路结构及其制作方法》权利说明书中写道,该专利所述的CMOS电路结构,其特征在于:所述CMOS电路结构的上半部分是负载管p-MOSFET,该p-MOSFET的栅电极、栅介质层和有源区分别由所述栅电极、位于上层硅锭有源区顶部和两侧的栅介质层和上层硅锭有源区构成: 该p-MOSFET的源区和漏分别为所述上层硅锭有源区的两端部分;该p-MOSFET的沟道区为位于所述栅电极之下的上层硅锭有源区的中间部分;所述CMOS电路结构的下半部分是驱动管n-MOSFET,该n-MOSFET的栅电极、栅介质层和有源区分别由所述栅电极、位于下层硅锭有源区两侧的栅介质层和下层硅有源区构成:该n-MOSFET的源区和漏区分别为所述下层硅有源区的两端部分;该n-MOSFET的沟道区为位于所述栅电极之下的下层硅有源区的中间部分。

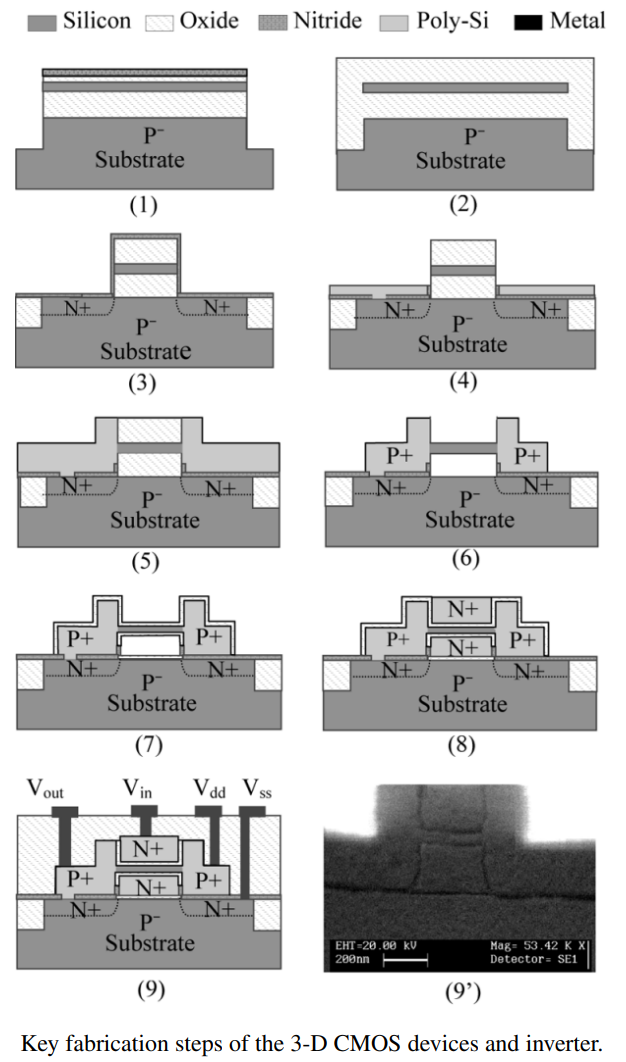

图片来源于IEEE EDL《A stacked CMOS technology on SOI substrate》论文 P662

图片来源于IEEE EDL《A stacked CMOS technology on SOI substrate》论文 P662

《A stacked CMOS technology on SOI substrate》论文摘要写道,堆叠晶体管技术优点包括:(1)有源器件的单晶多层;(2)具有厚源极/漏极和薄沟道区域的自对准双栅极p-MOSFET;(3)n-MOSFET到p-MOSFET的自对准沟道区域完美地堆叠在彼此之上;(4)显著节省面积;和(5)减少了互连距离和负载。实验结果表明,所制备的双栅p-MOSFET具有几乎理想的亚阈值摆幅和与具有相同横向宽度的n-MOSFET几乎相同的电流驱动,从而产生了高度紧凑且完全重叠的堆叠CMOS反相器。

张盛东博士的想法在当时太过超前,没有引起太多关注。当下摩尔定律放缓,堆叠晶体管概念重获关注。近几年来,该论文及其后续工作已被国际发明专利引用数百次;且受到产业巨头的推崇,IEDM 2021大会中英特尔的有关晶体管堆叠技术的邀请报告《Opportunities in 3-D stacked CMOS transistors》中就引用了上述论文,且是引用文献中时间最早的一篇;台积电在VLSI 2021的报告《CMOS Device Technology for the Next Decade》中指出,北京大学的3D Stacked CMOS晶体管是业界第一个堆叠互补晶体管,比台积电和英特尔要早15年。

鉴于这一原创性工作的重要贡献,笔者联系到目前为北京大学集成电路学院教授的张盛东老师,对当年的研究情况进行了访谈!

张盛东教授简传 获东南大学半导体物理与器件专业工学学士、东南大学半导体与微电子专业工学硕士、北京大学微电子学与固体电子学专业理学博士。参加工作30多年来,一直工作在我国半导体集成电路和半导体显示领域的科研和教学第一线。1999年前在国内的部属研究所从事工程技术开发工作。2002年加入北京大学信息科学技术学院(现集成电路学院)任教至今,并自2009年起兼任北京大学深圳研究生院信息工程学院教授。曾获国家技术发明二等奖,教育部技术发明一等奖,北京市科技一等奖,以及华为公司的“卓越贡献成就产业”勋章。

|

张盛东博士1980-90年代曾在南京某研究所从事研发工作。后因向往大学的工作环境,于1999年到北京大学攻读博士学位并留校任教。攻读博士学位期间,有幸加入王阳元院士和韩汝琦教授领导的超大规模集成电路新器件团队,围绕集成电路器件的Scaling-down(微缩)开展研究。

关于3D CMOS技术的研发过程,张教授回忆道,当时国际集成电路领域无论是学术界还是工业界,都在全力探究MOS器件特征尺寸的微缩极限。而我们当时就在思考这样一个问题,在未来,当特征尺寸微缩到达极限之后,集成电路将如何发展?众所周知,集成电路的基本单元是一互补的晶体管(CMOS)架构,即n-MOSFET和p-MOSFET构成的反相器。而n-MOS和p-MOS晶体管通常总是成对出现,因此,我们的构想就是将平面CMOS变成一个立体CMOS,即把其中的一个晶体管搬到另一个晶体管的上面,这样显然可以缩小单元面积,缩短互连,从而提升集成电路的集成度和性能。

基于这个思路,我们提出了三维堆叠晶体管(3D stacked CMOS)的概念。当时提出的器件结构,并不是一个n-MOS与p-MOS的简单堆叠,而是要形成了一个有机的组合体,成为了一个互补和共栅的器件单元。同时,考虑到空穴迁移率只有电子的一半甚至更小,我们的构想还包括,底层为n-MOS晶体管,而上层为双栅的p-MOS晶体管,这样上层的p-晶体管的驱动能力有望加倍甚至更强,因而可与底层n-晶体管的驱动能力实现匹配。所以,理论上,所提出的结构的单元面积只有常规结构面积的1/3。

概念形成后,如何在工艺层面上实现它?对此张教授表示:“这样一个概念具有价值的一个条件是,上层的晶体管有源层必须是单晶半导体材料,而在硅衬底上在位制备第二层单晶材料是非常困难的。我们当时想到采用硅的SOI晶圆来制备所提出的3D CMOS晶体管,即分别用单晶的SOI薄膜和隐埋氧化层下的单晶体硅来制备上下层的MOS晶体管,并设计了一个相对比较复杂的工艺流程。所设计的工艺制备方法需要用到CMP(化学机械抛光)设备,而当时的北京大学工艺实验室没有可用的CMP设备。”

根据张教授的回忆,当时受限于工艺条件,制备工作推进缓慢。后来受香港科技大学陈文新(Mansun Chan)教授的邀请,他作为访问学者赴香港科技大学纳米系统制造实验中心(NFF,Nanosystem Fabrication Facility)进行实验制备工作,最终在SOI衬底上成功完成第一个3D stacked CMOS原型器件,并获得了相当满意的器件/电路性能,证明了这一构想的可行性。这一工作成果发表于IEEE EDL的2004年第9期。在此同时,他又与同样来自北京大学的吴旭升博士合作,提出并实现了基于FinFET的3D stacked CMOS器件,该工作成果以《Stacked 3-D Fin-CMOS technology》为题发表于 IEEE Electron Device Letters( Volume: 26, Issue: 6, June 2005,P416-418)。张教授认为,这两工作应为3D CMOS技术最早的工作,目前所提出和开发的3D CMOS 结构总体上没有脱离他们原先的概念。

对于imec将这样一个三维结构的器件称为CFET,张教授也很认可,觉得也很有道理。不过,他指出,英特尔一直采用他们当初的名称,即3D stacked CMOS。

谈及如何看待堆叠晶体管时,张盛东教授表示:“一个新东西的出现往往会有很多的争议,这是很正常的,特别是在集成电路领域。一个新的结构或新材料的出现时,人们总希望它能与现有的制造工艺线兼容,不然难以产业化。当年FinFET提出时,也遭到很多人的质疑。我自己当年也从事FinFET的研究,随着研究的深入,发现要解决的工程难题越来越多,多到甚至让人失去信心,但最终还是被业界一一解决。同FinFET一样,堆叠晶体管面临要解决的工程问题也很多。”

谈及集成电路器件的未来发展趋势时,张盛东教授表示,就器件结构而言,从平面结构向三维结构发展,这是现在和未来一段时间正在和将要发生的事情。不过这只是结构和工艺上的增量创新,不会带来根本性的变化。他个人期待具有新功能和新原理器件的出现,这有望带来革命性的进步。长期以来,集成电路器件一直是MOSFET,即场效应晶体管,将来是否有新原理器件出现?值得拭目以待。最后张教授告诉笔者,关于集成电路未来发展的另一个热点话题是如何从集成电路发展到集成光路。

结语

张盛东教授的原创性工作也得益于北京大学在集成电路领域的深厚基础。

北京大学一直是我国集成电路学科建设和科技创新改革的排头兵,诞生了我国第一个半导体专业(1970年),研制了中国第一款大规模集成电路(1976年),获批国内第一个微米/纳米加工领域的国家级重点实验室(1996年),是首批国家集成电路人才培养基地(2003年)、首批国家示范性微电子学院建设单位(2015年)和首批国家集成电路产教融合创新平台(2019年)。经过几代北大微电子人的奋斗,集成电路学科发展迅速,取得了令人瞩目的成绩,北京大学黄如院士团队的低功耗多栅新结构器件和TFET超低功耗器件都已在中芯国际进行产业化转化工作,而对纳米级器件可靠性模型和测试方法已集成于Synopsys和Cadence 的EDA软件中,并注明”北京大学”的知识产权;刘飞研究员团队开发的基于流体动力学(HD)的TCAD工具原型和国内首个支持电子散射的量子输运器件仿真工具原型,以及林亦波研究员和王润声教授团队提出了模拟版图自动生成方法、交互式敏捷编辑方法,都即将应用于国内EDA企业。

北京大学在ISSCC、IEDM、VLSI等器件和电路顶会中发表一作超过120篇,在即将于2023年12月9-13日举行IEDM大会上,北京大学以14篇入选数量成为IEDM 2023接收来自全球论文最多的高校,连续第三年成为IEDM接收来自全球论文最多的高校。

这一切表明北京大学在集成电路技术领域的研究水平持续保持在国际前沿之列。

延伸阅读之晶体管的演变

自集成电路发明以来,经历了1960年代开始盛行的平面晶体管(Planar Transistor),2011年前后开始的三维鳍式场效应晶体管(FinFET,Fin Field-Effect Transistor)。现在环绕栅极场效应晶体管(GAA,Gate-All-Around FET)已经开始投产,将要替代FinFET。GAAFET有两种结构,分别是纳米线(Nanowire)、纳米片(Nanosheet),GAA在各家公司叫法不同,英特尔(Intel)将其2024年投产的GAA技术命名为RibbonFET,三星(Samsung)命名MBCFET(Multi-Bridge-Channel FET)。

因为GAA晶体管架构的能力有其局限性,单个器件的结构形式优化已经几乎推至极限。业界必须看得更远,要有新的结构来走支持下一代工艺。

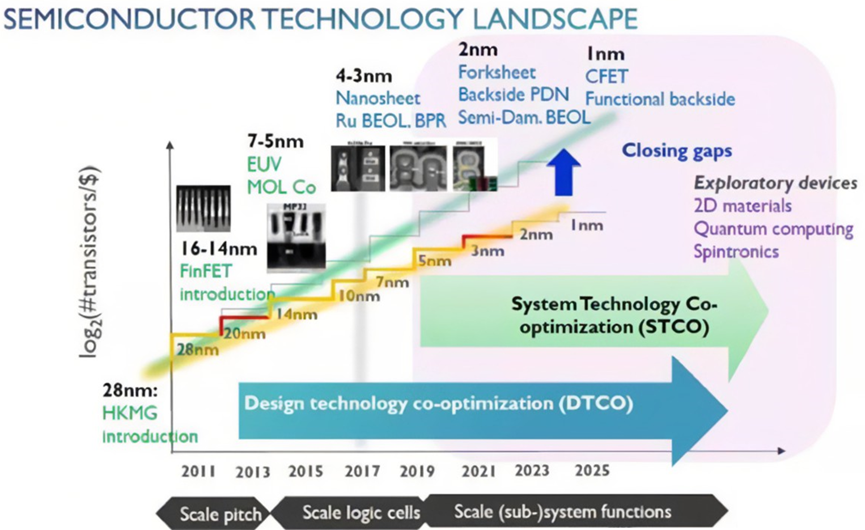

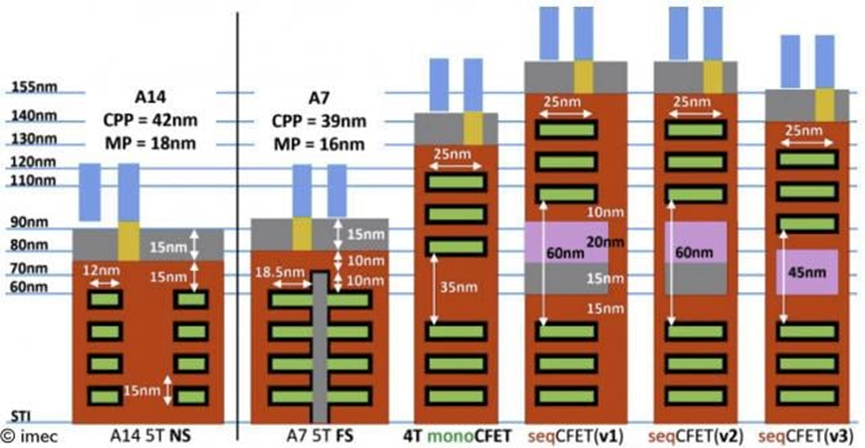

图片来源:imec半导体微缩化工艺/器件部门Myung-Hee Na博士2019年演讲PPT

图片来源:imec半导体微缩化工艺/器件部门Myung-Hee Na博士2019年演讲PPT

我们透过Myung-Hee Na博士的《Semiconductor Technology Landscape半导体技术前景》一页PPT来了解三维晶体管技术近10几年的变迁。

在28纳米技术世代,平面型MOS晶体管依然采用HKMG(High-K Metal Gate,高介电常数金属闸极)技术。

按照摩尔定律,晶体管的数量与芯片性能息息相关,在平面晶体管时代,22纳米基本就是业界公认的极限了。为了突破工艺极限,继续延续摩尔定律,胡正明教授于2000年前后提出了两种解决途径:一种是立体型结构的FinFET晶体管(鳍式场效应晶体管),另一种是基于SOI的超薄绝缘层上硅体技术FD-SOI晶体管技术(超薄绝缘层上硅体技术)。之后两者走出了不同的发展道路。

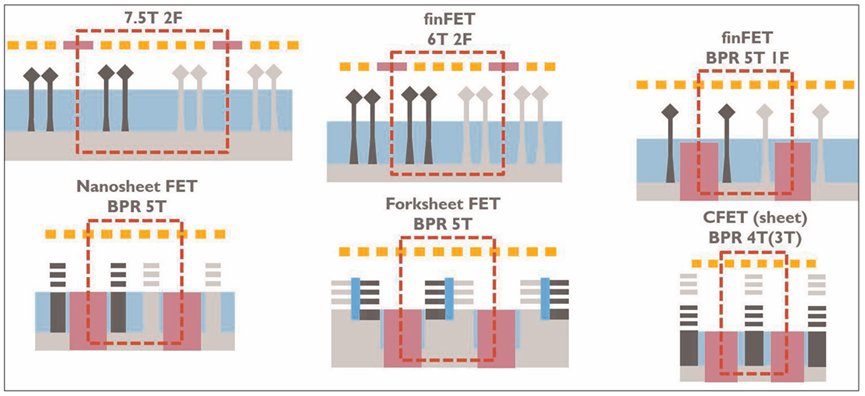

三维晶体管演变的历程:从 FinFET 到 nanosheet 到 forksheet,最后到 CFET

三维晶体管演变的历程:从 FinFET 到 nanosheet 到 forksheet,最后到 CFET

FinFET确切来说,是一个技术的代称。FinFET最大的特色就是将晶体管的结构从平面变立体,对栅极形状进行改制,栅极被设计成类似鱼鳍状3D架构,位于电路的两侧控制电流的接通与断开,大幅度提升了源极和栅极的接触面积,减少栅极宽度的同时降低漏电率,让晶体管空间利用率大大增加。

晶体管是最早实现3D化的,世界上第一个3D晶体管是由英特尔在2011年5月宣布研制成功,当时英特尔称其为 “Tri-Gate”。早在2002年,英特尔就已经提出了相关技术专利,花了将近10年完善,才在2011年用Tri-Gate技术量产22纳米工艺的新一代处理器lvy Bridge,显著提高了性能并降低了功耗,2012年初正式发布。虽然叫法不同,但Tri-Gate的本质就是FinFET。之后台积电(TSMC)、三星等全球半导体大厂陆续跟进,采用FinFET技术取得了巨大成功,使得FinFET大放异彩。从16/14纳米开始,FinFET成为了半导体器件的主流选择,成功地推动了从22纳米到5纳米等数代半导体工艺的发展,并将扩展到3纳米工艺节点,成为全球主流晶圆厂的“不二”之选。

FinFET工艺技术自2011年商业化以来,体系结构持续进行改进,以提高性能并减小面积。到了5纳米节点后,虽然使用了EUV光刻技术,但是基于FinFET结构进行芯片尺寸的缩小变得愈发困难。

而当制程工艺跨入5纳米世代,更是出现一系列新的问题。比如,随着栅极宽度的进一步缩小,很难再像过去那样在一个单元内填充多个鳍线,而鳍式场效应晶体管的静电问题也会严重制约晶体管性能的进一步提升。同时,从7纳米到5纳米,光刻技术发生了巨大的变化。不采用以往的DUV ArF浸没式光刻,而是导入了EUV(Extreme Ultraviolet,极紫外光刻)光刻技术。此外,将钴(Co)金属应用于MOL(middle of the line)的布线材料也开始被厂商引入。

换句话说,FinFET在5纳米世代就已逼近极限,想生产更具能效比的3纳米、2纳米甚至1纳米工艺,需要新型晶体管技术救场。

随着三星、英特尔两大晶圆代工巨头率先转向GAA(Gate-All-Around FET,环绕式场效应晶体管)工艺,也许预示着在更先进的节点上,FinFET将走向终结。根据国际器件和系统路线图(International Roadmap for Devices and Systems,IRDS)的规划,4/3纳米工艺制程中的FinFET晶体管结构将逐步被GAA晶体管结构所取代。

从4/3纳米世代开始,采用硅纳米片(Nanosheet)结构GAA,独创的埋入式电源线(将Vcc和地线埋入前层以压缩标准单元面积),采用Ru(钌)作为布线材料。

对于高性能和低功耗应用,2纳米世代计划采用截面类似于餐叉的叉板晶体管(Forksheet)结构,其中n型和p型纳米片紧密地靠在一起,并且其间有一层“绝缘墙”,与此同时,在芯片背面提供配电网络(PDN)从而向BPR提供有效的电能供应。

当达到1纳米世代时,计划采用互补场效应晶体管(CFET,Complementary FET)。CFET就是通过在p型FET上堆叠n型FET,即通过三维堆叠具有不同导电类型的晶体管,从而使得标准单元面积大大减小。

延伸阅读之CFET的研究进程

2018年,imec 提出CFET概念。CFET一般采用Nanosheet结构,将一个p型Nanosheet FET叠加在一个n型Nanosheet FET之上,形成三维晶体管,可以显著增强晶体管性能,并减小其尺寸。

CFET制造工艺包括单片(monolithic)与顺序(sequential)两种。单片CFET制备流程分为三部分:底部沟道的外延生长、沉积中间层,顶部沟道的外延生长;顺序CFET制备流程是从底部向上制造器件,利用晶圆键合技术,在顶部形成覆盖半导体层,最后对顶部元件进行集成,并连接顶栅和底栅。

对比来看,两种产品各有优缺点,单片CFET整合流程复杂,但成本较低,顺序CFET整合流程相对简单,但晶圆转移难度高。目前,CFET工艺仍在研究探索过程中,两种制造工艺哪一种更具发展价值尚未定论。

nanosheet、forksheet (FS)和CFET (单片和顺序)的栅极截面(基本顺序 CFET (=v1) 比单片设计更宽、更高;通过优化流程(包括自对准栅极合并 (v2)和无栅极帽 (v3)),顺序 CFET 在面积消耗方面接近单片 CFET)

CFET在晶体管设计中引入了一个显著的转变,即通过垂直堆叠,可以在一个晶体管的尺寸内放置两个晶体管,从而提高了芯片上晶体管的密度。CFET不仅为提高空间效率铺平了道路,还促进了CMOS逻辑电路布局的精简,提高了设计效率。

同时CFET的固有结构可减少寄生效应,从而提高性能和能效。CFET具有适应性强的设计能力,如平衡NMOS和PMOS沟道变化的能力,再加上背面功率传输等创新技术,进一步简化了制造流程,使CFET成为晶体管技术领域中一项前景广阔的发展。

近三年来,在IEDM、VLSI Technology大会以及ED杂志上,有关CFET的论文开始逐渐增多。

但是对于4T cell设计和16nm的金属间距,即使叉板变得太窄,也难以提供所需的性能。Imec的研究人员在VLSI 2022的论文中强调了这一挑战。这就是CFET可以提供缓解的地方。因为在CFET架构中,nMOS和 pMOS 器件相互堆叠,从而进一步最大化有效沟道宽度。

在CFET架构中,nMOS型和pMOS 器件相互堆叠。堆叠从单元高度考虑中消除了n-p间距,允许进一步最大化有效沟道宽度,从而进一步最大化驱动电流。我们还可以使用由此产生的面积增益将轨道高度推至 4T 及以下。

在CFET研究方面,中国内地的学术界也展现了相当的实力。

在IEDM 2021上,北京大学集成电路学院发表题为《Demonstration of Vertically-Stacked CVD Monolayer Channels:MoS2 Nanosheets GAA-FET with Ion>700μA/μm and MoS2/WSe2 CFET”》的论文,展示了基于单层二硫化钼的堆叠围栅纳米片器件,实现了开态电流超过400μA/μm(@Vd=1V)或700μA/μm(@Vd=2V),该结果远超同类器件的文献报道水平;并通过上百个器件的统计分析,显示了该器件由三维集成和尺寸缩小带来的性能提升;同时,首次报道了亚1纳米沟道厚度的二硫化钼/二硒化钨CFET器件,实现了反相器逻辑功能。

2022年IEEE Transactions on Electron Devices的7月刊发表了中国科学院微电子研究所集成电路先导工艺研发中心题为“Investigation of Novel Hybrid Channel Complementary FET Scaling Beyond 3-nm Node From Device to Circuit”的论文,利用业界主流的Design-Technology Co-optimization(DTCO)方法全面探索了CFET的器件架构优势,提出了新型混合沟道CFET(Hybrid Channel Complementary FET,HC-CFET)结构设计和集成方案。该结构能够在单一衬底上,不借助晶圆键合等混合晶向技术,利用SiNx与SiO2的高刻蚀选择比,通过分步沟道形貌刻蚀,实现对N-FET和P-FET首选高电子与空穴迁移率导电沟道的共同优化,即使得N-FET具有(100)沟道表面晶向,P-FET具有(110)沟道表面晶向,从而在同等投影平面下获得最佳的器件与电路性能。该结构设计与集成方案的可行性已通过Virtual-FAB模拟仿真验证。进一步通过精确数值求解预测了全部寄生参数,对比了不同CFET架构下的17级环形振荡器和SRAM单元性能。结果表明,相较于常规垂直集成Fin和垂直集成纳米片的CFET结构(MS-CFET和MB-CFET),新型HC-CFET具有沟道晶向与空间布局优势,展现出更高的工作频率以及更优的噪声容限窗口,以及在高度微缩的高性能CMOS集成电路应用上的巨大潜力。

2022年12月Nature Electronics发表了复旦大学微电子学院题为“Heterogeneous Complementary Field-effect Transistors Based on Silicon and Molybdenum Disulfide”的论文,团队将新型二维原子晶体引入传统的硅基芯片制造流程,实现了晶圆级异质CFET技术。相比于硅材料,二维原子晶体的原子层精度使其在小尺寸器件中具有优越的短沟道控制能力。利用硅基集成电路的标准后端工艺,将新型二维材料二硫化钼(MoS2)三维堆叠在传统的硅基芯片上,利用两者高度匹配的物理特性,形成p型硅-n型二硫化钼的异质CFET结构。在相同的工艺节点下将集成电路的集成密度翻倍,并获得了优越的器件性能。

在学术界展开CFET研究的同时,工业界的研发也在快速跟进中。

而在即将召开的IEDM2023大会上,英特尔(Intel)和台积电(TSMC)即将公布下一代CFET(Complementary FET,互补场效应晶体管)晶体管的进展情况。从两家公司提前公布的信息判断,堆叠式CFET架构未来将取代GAA(Gate-All-Round),成为1nm以下逻辑技术节点的极具吸引力的器件架构。

其实英特尔最早发表的有关CFET论文是 IEDM 2019的主题演讲《Process and Packaging lnnovations for Moore's Law Continuation and Beyond》中,在IEDM 2020上展示了第一个使用CFET技术的逻辑电路设计。

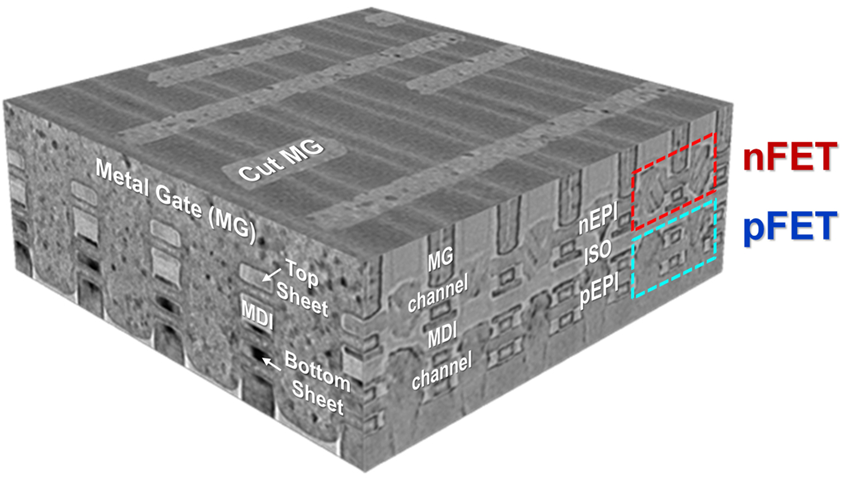

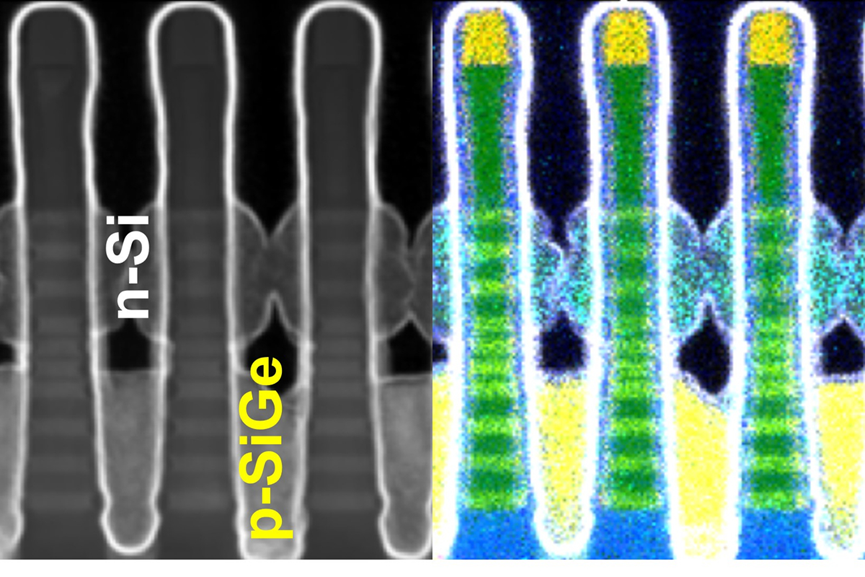

IEDM 2021邀请论文中来自英特尔的“Opportunities in 3-D stacked CMOS transistors”论文,该论文展示了实现三维CMOS堆叠的几种方法,顺序方法通过在Si NMOS上通过层转移制造Ge PMOS来强调,而自对准方法通过在PMOS多纳米带硅晶体管上同时制造NMOS来证明。这两种方法都展示了由顶部和底部器件层的晶体管构建的平衡良好的CMOS反相器。并强调三维堆叠CMOS晶体管为实现进一步的标准单元和SRAM缩放提供了机会,使其成为扩展摩尔定律的有前景的晶体管架构。

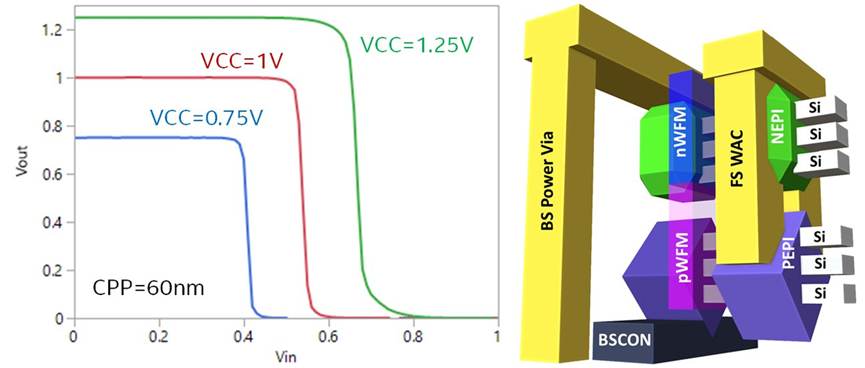

根据IEDM2023的议程安排得知,英特尔将发表题为“Demonstration of a Stacked CMOS Inverter at 60nm Gate Pitch with Power Via and Direct Backside Device Contacts”的论文,详细介绍由单个CFET构建的inverter circuit。这种电路的尺寸可能只有普通CMOS电路的一半。

a TEM micrograph of the CFET device following vertically stacked dual source-drain (SD) epitaxy at CPP-60nm.

a TEM micrograph of the CFET device following vertically stacked dual source-drain (SD) epitaxy at CPP-60nm.

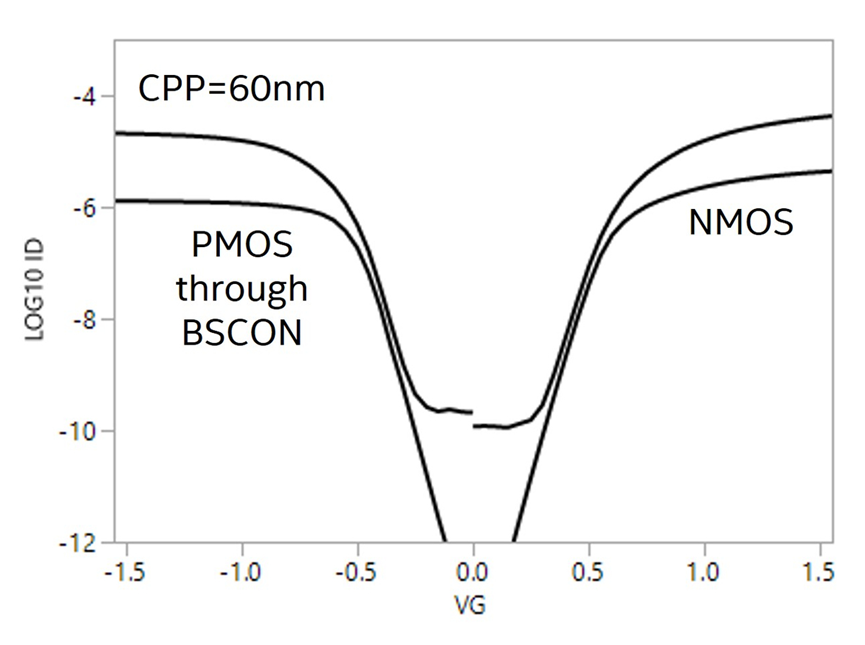

l-Ve curves at VDS-0.05V and 0.65V for CFET devices on the same difrusion at CPP-60nm. Bottom p-MOs is measured through backsidedevice contacts (BSCON). whereas top -MOS is measured through shallow frontside contacts and backside power via. Devices show asubthresholdswing (SS) of 63mV/dec and 66mV/dec and DIBL of 57V/V and 38mV/V for n-MOS and p-MOS, respectively

l-Ve curves at VDS-0.05V and 0.65V for CFET devices on the same difrusion at CPP-60nm. Bottom p-MOs is measured through backsidedevice contacts (BSCON). whereas top -MOS is measured through shallow frontside contacts and backside power via. Devices show asubthresholdswing (SS) of 63mV/dec and 66mV/dec and DIBL of 57V/V and 38mV/V for n-MOS and p-MOS, respectively

the inverter voltage transfer curve. which verifies that a highlighted components are working toeether on the same diffusion. making for awell-balanced inverter

the inverter voltage transfer curve. which verifies that a highlighted components are working toeether on the same diffusion. making for awell-balanced inverter

英特尔表示,该器件由3p-FET纳米带顶部的3个n-FET纳米带组成,它们之间的垂直间距为30纳米。他们使用该器件以60nm栅极间距构建全功能inverters (test circuits),这在业界尚属首次。该器件还采用垂直堆叠双S/D外延技术;连接n和p晶体管的双金属功函数栅极叠层;以及与PowerVia背面供电和直接背面器件接触的集成。研究人员还将描述纳米带“depopulation”过程,用于需要数量不等的n-MOS/p-MOS器件。这项工作有助于加深对逻辑和SRAM应用扩展CFET潜力的理解,并了解关键的工艺推动因素。

同一个SESSION中,台积电也将发表题为《Complementary Field-Effect Transistor (CFET) Demonstration at 48nm Gate Pitch for Future Logic Technology Scaling》论文,讨论专为逻辑技术量身定制的、具有48纳米栅极间距的CFET方法。台积电的设计强调在p型晶体管上分层放置n型纳米片晶体管,从而实现了跨越六个数量级的出色导通/关断电流比。台积电已经证明了其耐用性,据称,90%以上的晶体管成功通过了测试。但是台积电担承,要充分发挥CFET技术的能力,还需要吸收更多的功能,但目前正在进行的工作是实现这一目标的关键一步。