关注 ▲射频美学 ▲ ,一起学习成长

这是射频美学的第1441期分享。

来源 | 整编;

微圈 | 进微信群,加微信: RFtogether521 ;

备注 | 昵称+地域+产品及岗位方向 (如大魔王+上海+芯片射频工程师);

宗旨 | 看到的未必是你的,掌握底层逻辑才是。

半导体封装的四个主要作用,包括机械保护、电气连接、机械连接和散热。封装的形状和尺寸各异,保护和连接脆弱集成电路的方法也各不相同。

半导体封装的分类

半导体封装方法,大致可以分为两种:传统封装和晶圆级(Wafer-Level)封装。传统封装首先将晶圆切割成芯片,然后对芯片进行封装;而晶圆级封装则是先在晶圆上进行部分或全部封装,之后再将其切割成单件。

晶圆级封装方法可进一步细分为四种不同类型:

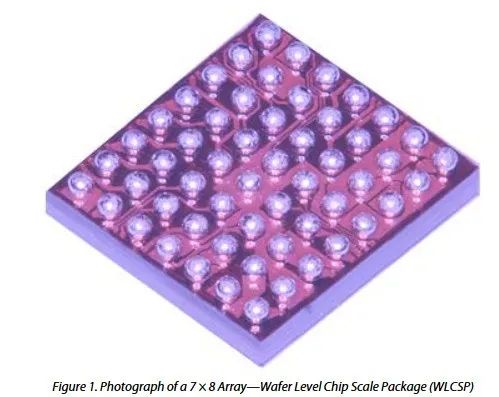

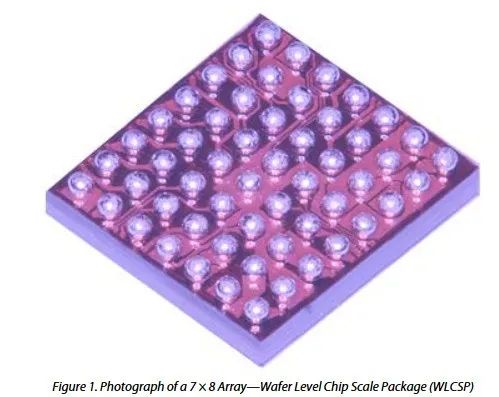

1)晶圆级芯片封装(WLCSP),可直接在晶圆顶部形成导线和锡球(Solder Balls),无需基板;

2)重新分配层(RDL),使用晶圆级工艺重新排列芯片上的焊盘位置1,焊盘与外部采取电气连接方式;

3)倒片(Flip Chip)封装,在晶圆上形成焊接凸点2进而完成封装工艺;

4)硅通孔(TSV)封装,通过硅通孔技术,在堆叠芯片内部实现内部连接。

晶圆级芯片封装分为扇入型WLCSP和扇出型WLCSP。扇入型WLCSP工艺将导线和锡球固定在晶圆顶部,而扇出型WLCSP则将芯片重新排列为模塑3晶圆。这样做是为了通过晶圆级工艺形成布线层,并将锡球固定在比芯片尺寸更大的封装上。

扇入型 (Fan-In) WLCSP (Wafer Level Chip Scale Package)

晶圆级芯片封装的大多数制造过程都是在晶圆上完成的,是晶圆级封装的典型代表。然而,从广义上讲,晶圆级封装还包括在晶圆上完成部分工艺的封装,例如,使用重新分配层、倒片技术和硅通孔技术的封装。在扇入型WLCSP和扇出型WLCSP中,“扇”是指芯片尺寸。扇入型WLCSP的封装布线、绝缘层和锡球直接位于晶圆顶部。与传统封装方法相比,扇入型WLCSP既有优点,也有缺点。

在扇入型WLCSP中,封装尺寸与芯片尺寸相同,都可以将尺寸缩至最小。此外,扇入型WLCSP的锡球直接固定在芯片上,无需基板等媒介,电气传输路径相对较短,因而电气特性得到改善。而且,扇入型WLCSP无需基板和导线等封装材料,工艺成本较低。这种封装工艺在晶圆上一次性完成,因而在裸片(Net Die,晶圆上的芯片)数量多且生产效率高的情况下,可进一步节约成本。

扇入型WLCSP的缺点在于,因其采用硅(Si)芯片作为封装外壳,物理和化学防护性能较弱。正是由于这个原因,这些封装的热膨胀系数与其待固定的PCB基板的热膨胀系数5存在很大差异。受此影响,连接封装与PCB基板的锡球会承受更大的应力,进而削弱焊点可靠性。

存储器半导体采用新技术推出同一容量的芯片时,芯片尺寸会产生变化,扇入型WLCSP的另一个缺点就无法使用现有基础设施进行封装测试。此外,如果封装锡球的陈列尺寸大于芯片尺寸,封装将无法满足锡球的布局要求,也就无法进行封装。而且,如果晶圆上的芯片数量较少且生产良率较低,则扇入型WLCSP的封装成本要高于传统封装。

扇出型WLCSP

扇出型WLCSP既保留了扇入型WLCSP的优点,又克服了其缺点。

扇入型WLCSP的所有封装锡球都位于芯片表面,而扇出型WLCSP的封装锡球可以延伸至芯片以外。在扇入型WLCSP中,晶圆切割要等到封装工序完成后进行。因此,芯片尺寸必须与封装尺寸相同,且锡球必须位于芯片尺寸范围内。在扇出型WLCSP中,芯片先切割再封装,切割好的芯片排列在载体上,重塑成晶圆。在此过程中,芯片与芯片之间的空间将被填充环氧树脂模塑料,以形成晶圆。然后,这些晶圆将从载体中取出,进行晶圆级处理,并被切割成扇出型WLCSP单元。

除了具备扇入型WLCSP的良好电气特性外,扇出型WLCSP还克服了扇入型WLCSP的一些缺点。这其中包括:无法使用现有基础设施进行封装测试;封装锡球陈列尺寸大于芯片尺寸导致无法进行封装;以及因封装不良芯片导致加工成本增加等问题。得益于上述优势,扇出型WLCSP在近年来的应用范围越来越广泛。

WLCSP 封装流程

晶圆片级芯片规模封装(Wafer Level Chip Scale Packaging,简称WLCSP),即晶圆级芯片封装方式,不同于传统的芯片封装方式(先切割再封测,而封装后至少增加原芯片20%的体积),此种最新技术是先在整片晶圆上进行封装和测试,然后才切割成一个个的IC颗粒,因此封装后的体积即等同IC裸晶的原尺寸。

图源:ADI《AN-617 Application Note》

本文主要介绍一下WLCSP封装的大致流程:(一般分为Bumping,CP test,WLCSP三个阶段)

Bumping阶段

1. Customer Wafer

这是第一道工序,主要是将从晶圆厂收到的wafer经过Pre-Clean + SRD预处理,然后使用O2 Plasma等离子清洗并烘干,目的是去除来料wafer表面的杂质。

2. PI coating

PI是一层聚合物薄膜层,可以加强芯片的passivation,起到应力缓冲的作用。做法是将预处理后的wafer置于设备吸盘上,wafer正面朝上,在wafer正面喷涂高度光敏感性的光刻胶,设备吸盘高速旋转,使光刻胶均匀喷涂在整个wafer表面。

3.PI Expose

PI曝光是在喷涂光刻胶的wafer与光源(紫外光)中间放入掩膜版(mask),再用紫外光透过掩模照射在硅片表面,被光线照射到的光刻胶会发生反应。光刻胶有正性光刻胶和负性光刻胶两种。正性光刻胶是掩膜版遮挡的区域进行曝光,而负性光刻胶是对掩膜版未遮挡的区域进行曝光。

4.PI Develop

PI显影。与PI Coating原理类似,在wafer正面喷涂显影液,显影液与之前曝光区域形成化学反应后,会将曝光区域显影出来,即形成后续工艺中UBM层所需的一层开口区域。

5.PI CURE

对已显影的wafer进行烘烤,目的是蒸发掉剩余的溶剂使光刻胶变硬,提高光刻胶对硅片表面的粘附性。

6.Sputter Ti

溅射Ti层。Ti层是组成UBM(under ball metal)的第一层。UBM层一般有两层组成(有些厂家做三层),第一层为Ti,第二层为Cu。Ti具有高强度,耐腐蚀性等特点,能与AL PAD和Passivation连接良好,所以Ti层能为UBM层提供高强度的支撑。Sputter 原理是在真空环境下,电极两端加上高压产生直流光辉放电,使加入腔体内的工艺气体(如Plasma)进行电离,电离后的正离子在电压的作用下高速轰击靶材,靶材逸出的原子和分子向wafer表面沉积形成薄膜层,即Ti层。

7.Sputter Cu

溅射UBM的第二层Cu. 此处的Cu一般只有1um左右,只是为了形成一个钝化层面,为后续电镀Cu提供坚实的基础。SputterCu的原理与Sputter Ti类似。

8. PR Coating

PR胶是一种负性光刻胶,是一种间接材料,与PI时的正性光刻胶作用相反。它的作用是为了在后续工艺中将不需要电镀Cu的地方覆盖,这样在电镀Cu时,只在PR胶未覆盖的地方”长”Cu,即UBM开口区域。

9.PR曝光

PR胶曝光同PI曝光原理类似,为了形成UBM开口区域,需通过曝光和显影工序将UBM开口区域多余的化学层去除。

10.PR显影

PR胶显影与PI显影原理类似,在PR曝光区域,利用显影液将曝光区域去除,只留出UBM开口区域。

11.Plating Cu

电镀Cu层,将刚溅射的Cu电镀到一定厚度,不仅为置球提供良好的支撑,也为锡球与wafer内部电路层提供良好的导电连接。此时PR胶覆盖区域就不会”长”Cu,而未覆盖区域”长”出所需要的Cu层。

12.刻蚀(PR, Cu , Ti )

利用化学品分别刻蚀掉UBM开口四周多余的PR层,Cu层,Ti层。至此,一个完整的UBM开口区域就形成了。

13.Ball Mount

置球。UBM开口形成后,就需要将球置于UBM开口上。将带有UBM开口的wafer置于钢网(Stencil)下面,UBM开口与钢网开口一一对齐,然后在钢网上刷上一层助焊剂Flux,最后用刮刀将锡球从钢网开口”落”在UBM开口区域

14.Reflow

回流焊。将置好球的wafer放入回流炉中,锡球在助焊剂flux和高温(大约260°)的作用下慢慢”长大”,并完美的填充UBM开口区域,与wafer形成良好的连接。锡球的作用是建立wafer内部电路与外部电路的”桥梁”。至此,整个Bumping工艺完全结束。

CP test阶段

晶圆测试。将完成回流焊的wafer进行测试,目的是将在bumping工艺中的不良筛选出来,提高后续封装的良率,监测整个bumping工艺的质量。

WLCSP阶段

1. Backside Grind

在wafer正面(球面)贴上一层蓝膜,保护锡球,然后在Wafer背面用磨轮磨至wafer指定厚度。

2. Wafer Backside Coating

在wafer背面刷一层背胶。目的是为了增强wafer的硬度,避免容易造成chipping。然后在一定温度下进行烘烤。(这一步选做,可做可不做)。

3. Marking(丝印)

在wafer背面按照产品要求打上Marking,包括公司Logo,生产日期,产品批次等相关信息。

4.Wafer Saw

Wafer切割。将打好丝印的wafer切割成一粒一粒的芯片。在切割之前,需在wafer背面贴上蓝膜,目的是为切割后的单颗芯片提供保护,不会散落。

5.Tape & Reel

先由顶针将切割后的芯片从蓝膜上一颗一颗顶起,然后由吸嘴吸起来,放在编带中进行卷带,最后包装出货。

以上步骤是整个流程的大致步骤,忽略了一些检验,ball shear之类的动作。

资料来源:

1.《[半导体后端工艺: 第三篇] 了解不同类型的半导体封装》,作者:skhynix

https://news.skhynix.com.cn/semiconductor-back-end-process-episode-3-understanding-the-different-types-of-semiconductor-packages/

2. 《WLCSP封装流程》,作者:简单qqq

https://mbb.eet-china.com/forum/topic/85620_1_1.html

声明: 欢迎转发本号原创内容,转载和摘编需经本号授权并标注原作者和信息来源为射频美学。 本公众号目前传播内容为本公众号原创、网络转载、其他公众号转载、累积文章等,相关内容仅供参考及学习交流使用。由于部分文字、图片等来源于互联网,无法核实真实出处,如涉及相关争议,请跟我们联系,我们致力于保护作者知识产权或作品版权,本公众号所载内容的知识产权或作品版权归原作者所有。