/*********************************************************************

* Copyright © blog.csdn.net/whik1194

* ModuleName : board_sel.v

* CreateTim : 2023年11月5日 19:16:48

* Author : mcu149

* Function : function

* Version : v1.0

* Version | Modify

* ----------------------------------

* v1.0 | first version

*********************************************************************/

module board_sel(

//Inputs

input clk_a, //100MHz

input clk_b, //100MHz

//Outputs

output reg [1:0] sel = 2'd0,

output reg rst_n = 1'b0

);

//1.parameter

// parameter LATCH_TIME = 10_000_000 / 10; //10ms

// parameter RESET_TIME = 100_000_000 / 10; //100ms

// for simulation

parameter LATCH_TIME = 5_000 / 10; //simulation, 5 us

parameter RESET_TIME = 10_000 / 10; //simulation, 10 us

//2.localparam

localparam BOARD_A = 2'd1;

localparam BOARD_B = 2'd2;

//3.reg

reg [31:0] cnt_a = 0;

reg [31:0] cnt_b = 0;

//4.wire

//5.assign

//6.always

always @ (posedge clk_a) begin

if(cnt_a < LATCH_TIME + RESET_TIME)

cnt_a <= cnt_a + 1;

end

always @ (posedge clk_b) begin

if(cnt_b < LATCH_TIME + RESET_TIME)

cnt_b <= cnt_b + 1;

end

always @ (*) begin

if(cnt_a == LATCH_TIME)

sel <= BOARD_A;

else if(cnt_b == LATCH_TIME)

sel <= BOARD_B;

end

always @ (*) begin

if((cnt_a == LATCH_TIME + RESET_TIME) || (cnt_b == LATCH_TIME + RESET_TIME))

rst_n <= 1;

end

//7.instance

endmodule //board_sel end

/*********************************************************************

* Copyright © blog.csdn.net/whik1194

* ModuleName : board_sel.v

* CreateTim : 2023年11月5日 19:40:48

* Author : mcu149

* Function : function

* Version : v1.0

* Version | Modify

* ----------------------------------

* v1.0 | first version

*********************************************************************/

module board_dock(

//Inputs

input [1:0] sel,

input clk_a,

input clk_b,

input uart_txd,

input led1,

//Outputs

output clk,

output uart_txd_a,

output uart_txd_b,

output led1_a,

output led1_b

);

//1.parameter

//2.localparam

localparam BOARD_A = 2'd1;

localparam BOARD_B = 2'd2;

localparam DEFAULT_OUT_VALUE = 1'b1;

//3.reg

//4.wire

//5.assign

assign clk = (sel == 2'd0 ) ? DEFAULT_OUT_VALUE : ((sel == BOARD_B) ? clk_b : clk_a );

assign uart_txd_a = (sel == BOARD_A) ? uart_txd : DEFAULT_OUT_VALUE;

assign uart_txd_b = (sel == BOARD_B) ? uart_txd : DEFAULT_OUT_VALUE;

assign led1_a = (sel == BOARD_A) ? led1 : DEFAULT_OUT_VALUE;

assign led1_b = (sel == BOARD_B) ? led1 : DEFAULT_OUT_VALUE;

//6.always

//7.instance

endmodule //board_dock end

`timescale 1ns/1ps

`define BRD_A

// `define BRD_B

module top_tb;

localparam PERIOD = 10; //10ns

localparam BOARD_A = 2'd1;

localparam BOARD_B = 2'd2;

reg clk_a;

reg clk_b;

reg uart_txd;

reg led1;

wire [1:0] sel;

wire rst_n;

`ifdef BRD_A

always #(PERIOD/2) clk_a <= !clk_a;

`endif

`ifdef BRD_B

always #(PERIOD/2) clk_b <= !clk_b;

`endif

initial begin

$display("testbench: %s", "top_tb");

clk_a = 0;

clk_b = 0;

uart_txd = 0;

led1 = 0;

end

always #(500_000) uart_txd <= !uart_txd;

always #(200_000) led1 <= !led1;

board_sel board_sel_ut0(

//Inputs

.clk_a(clk_a), //100MHz

.clk_b(clk_b), //100MHz

//Outputs

.sel(sel),

.rst_n(rst_n)

);

board_dock board_dock_ut0(

//Inputs

.sel(sel),

.clk_a(clk_a),

.clk_b(clk_b),

.uart_txd(uart_txd),

.led1(led1),

//Outputs

.clk(clk),

.uart_txd_a(uart_txd_a),

.uart_txd_b(uart_txd_b),

.led1_a(led1_a),

.led1_b(led1_b)

);

endmodule //top_tb end

Xilinx FPGA芯片内部时钟和复位信号使用

强大的JTAG边界扫描5-FPGA边界扫描应用

强大的JTAG边界扫描4-STM32边界扫描应用

强大的JTAG边界扫描3-常用边界扫描测试软件

强大的JTAG边界扫描2-BSDL文件

强大的JTAG边界扫描1-基本原理

用JLink和OpenOCD来下载Xilinx FPGA程序

获取Xilinx FPGA芯片IDCODE的4种方法(支持任何FPGA型号)

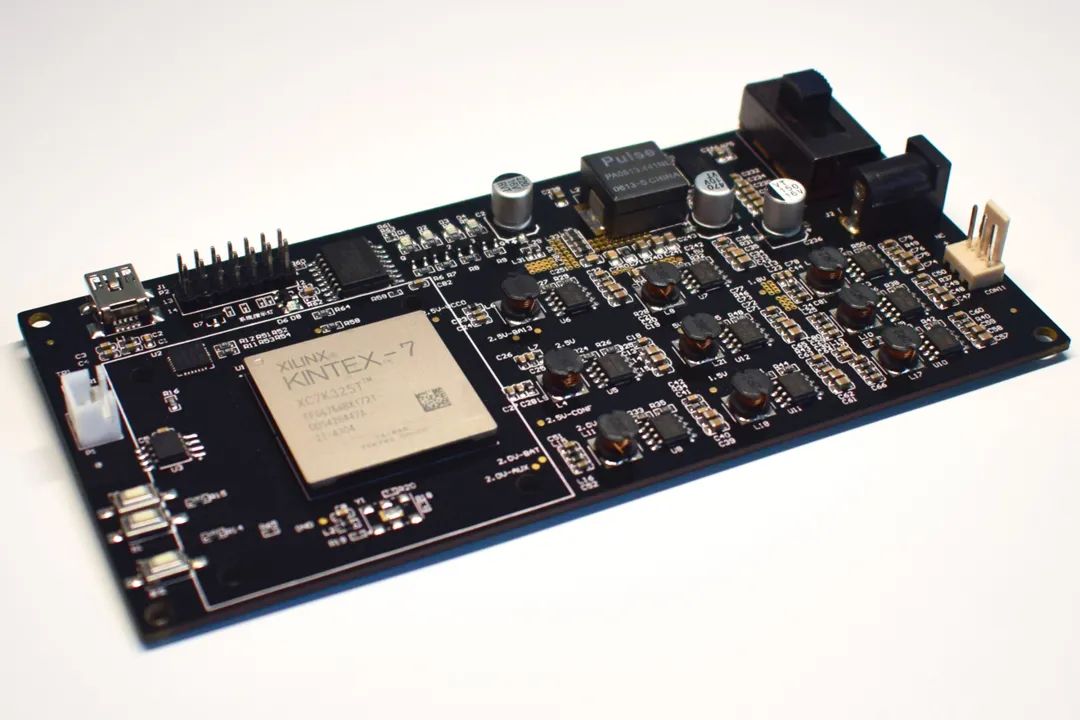

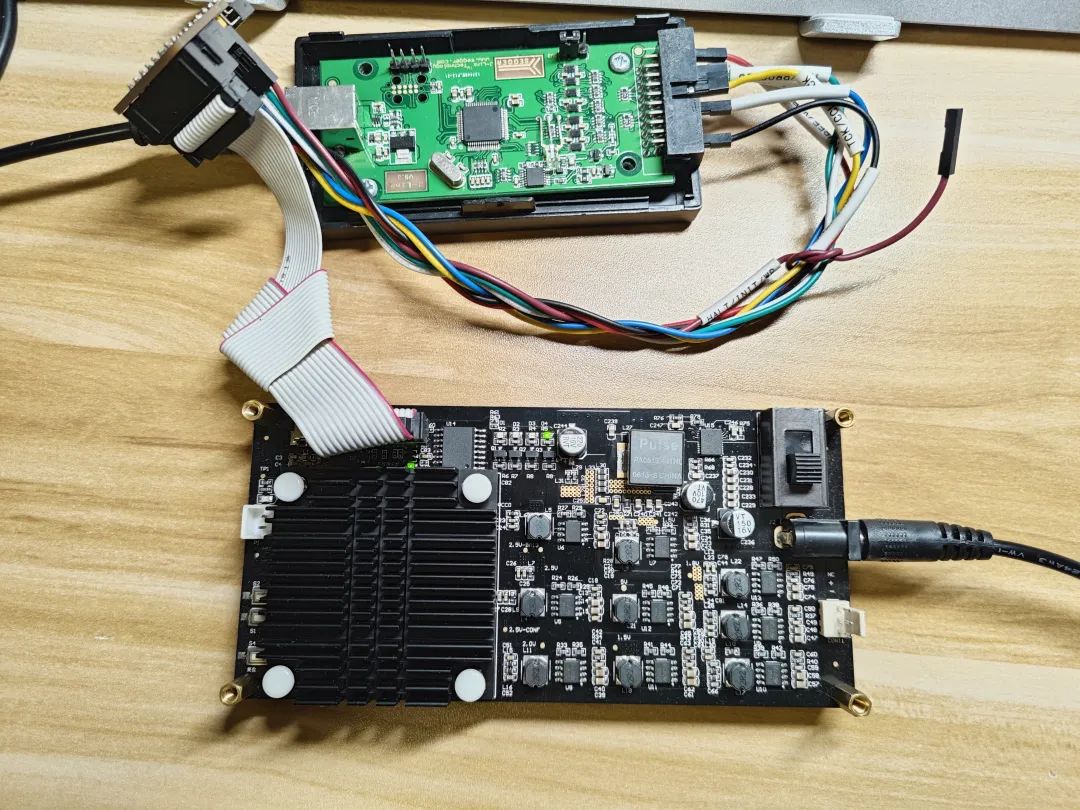

Xilinx FPGA Multiboot设计与实现(Spartan-6和Kintex-7示例)

业余无线电是什么?