01

SerDes简介

1.减少布线冲突(非独立时钟嵌入在数据流中,解决了限制数据传输速率的Signal时钟的Jilter问 题);带宽高 ;

2.引脚数目少 ;

3.抗噪声、抗干扰能力强(差分传输);

4.降低开关噪声;

5.扩展能力强;

SerDes支持非常多的的主流工业标准,比如Serial RapidIO ,FiberChannel(FC),PCI-Express (PCIE),Advanced Switching Interface,Serial ATA(SATA),1-Gb Ethernet,10-Gb Ethernet(XAUI),Infiniband 1X,4X,12X等。

02

SerDes结构

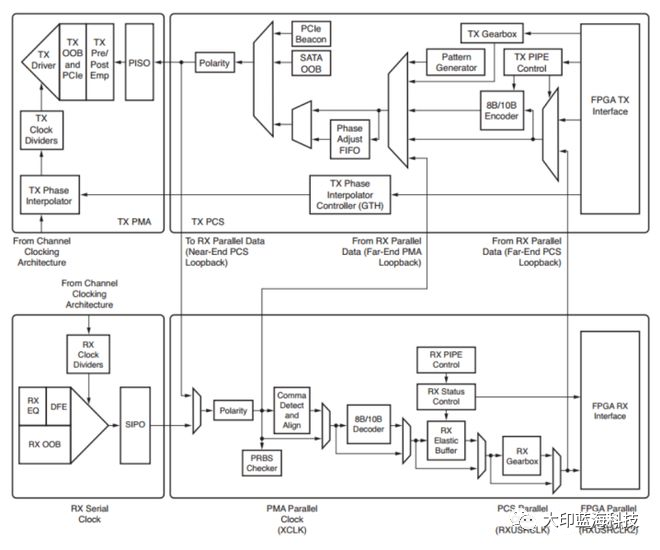

SerDes收发器内部的电路物理层结构图

3.PMD层,负责串行信号通信。

涉及模块:

1.TXPLL:这个模块主要使用具有1ps以下的抖动的时钟为参考,输出数GHZ级的时钟。

2.RXCDR(时钟恢复):这个模块是一个复杂的控制回路,作用是来追踪传入数据的平均相位, 并不管Path上的任何SI或失真,通常是通过复杂的相位旋转器或CDR驱动的锁相环来完成的。

3.TXdriver:这个模块把序列化模块转化为差分信号。

4.RX均衡器:此模块用连续的时间均衡器以及DFE(裁决反馈均衡器)来均衡高速效应,通常 需要一个自动增益的电路来促进均衡效果,RX均衡器通常以状态机逻辑和软件的形式来实现 自动校准。

2.接收(RX)即串转并 简单的来说就是输入的串行信号经过线性均衡器均衡后,去除了高速时钟的jilter后,CDR从数 据中恢复Caputure时钟,并通过解串器转为对齐的并行信号,由驱动发出。

03

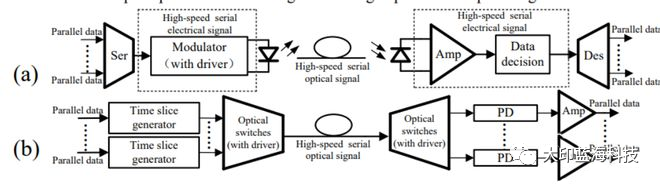

光SerDes解串器

04

SerDes主要包括以下几个部分:

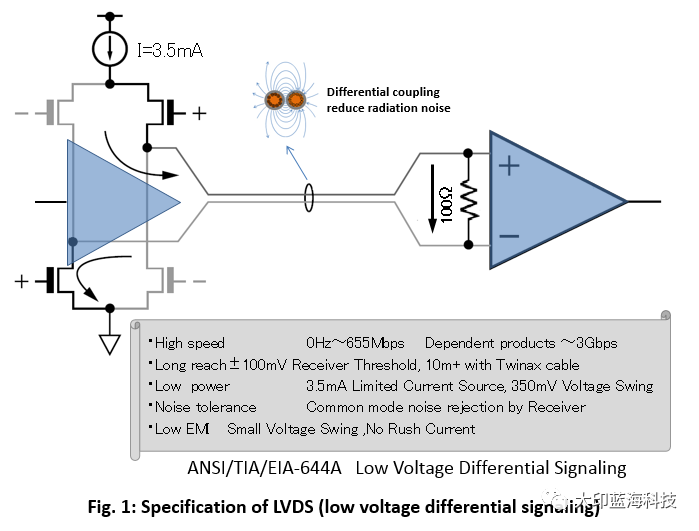

1、SerDes的前辈:LVDS SerDes,其中LVDS应该是大家比较熟悉的,这里不会展开,主要就是LVDS是1995年作为「ANSI/TIA/EIA-644」制定了标准规格的串行接口用物理层规格,为很多串行差分总线的发展奠定了基础。

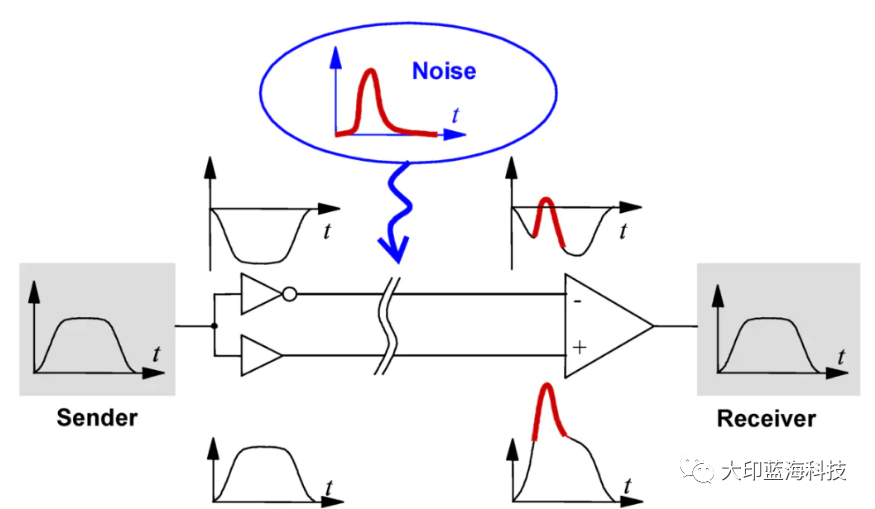

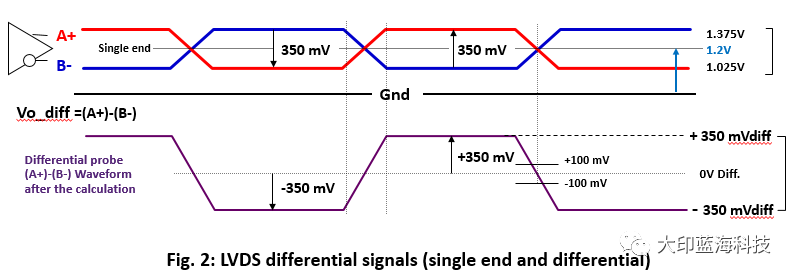

差分信号示意图

差分信号与传统的一根信号线一根地线(即单端信号)走线的做法相比,其优缺点分别是。

优点:

1.抗干扰能力强。干扰噪声一般会等值、同时的被加载到两根信号线上,而接收端关心的只是两信号的差值,所以外界的共模噪声可以被完全抵消。

2.能有效抑制电磁干扰(EMI)。由于两根线靠得很近且信号幅值相等,这两根线与地线之间的耦合电磁场的幅值也相等,同时他们的信号极性相反,按右手螺旋定则,那他们的磁力线是互相抵消的。两根线耦合的越紧密,互相抵消的磁力线就越多。泄放到外界的电磁能量越少。

3.时序定位准确。差分信号的接收端是两根线上的信号幅值之差发生正负跳变的点,作为判断逻辑0/1跳变的点的。而普通单端信号以阈值电压作为信号逻辑0/1的跳变点,受阈值电压与信号幅值电压之比的影响较大,不适合低幅度的信号。

4.发送端电流源始终导通,消除开关噪声带来的尖峰(单端技术中所需要)和大电流晶体管不断导通-关断造成的电磁干扰EMI。

缺点:

若电路板的面积非常吃紧,单端信号可以只有一根信号线,地线走地平面,而差分信号一定要走两根等长、等宽、紧密靠近、且在同一层面的线。这样的情况常常发生在芯片的管脚间距很小,以至于只能穿过一根走线的情况下。

05

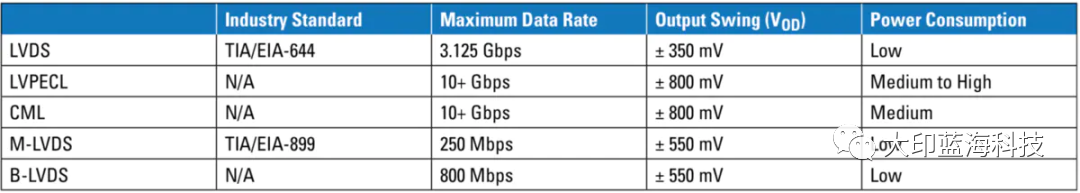

几种典型差分信号

为了实现高速数据传输,有多种差分技术可供选择。这些差分技术都有差分信号几个共同的优点,但是在性能、功耗和应用场景上有很大的区别。下图列举了最常用的几种差分信号技术和它们的主要参数。

各种差分技术的工业标准

06

发挥高速的数据传输的作用

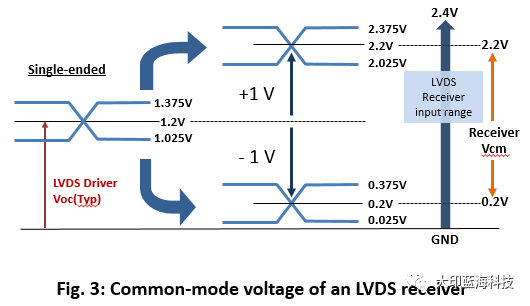

LVDS是1995年作为「ANSI/TIA/EIA-644」制定了标准规格的串行接口用物理层规格(图1)。通过驱动3.5mA的稳定电流电源,可在100Ω終端时,以350mV这样非常低振幅的差动信号来高速传送数据。其数据传输速度在规格内限定最大为655Mbit/秒。但这并不是极限值。通过各半导体厂商独有的加工,可以完成3Gbit/秒左右的高速传输速度。

07

对配线扭曲和共通电压耐性强

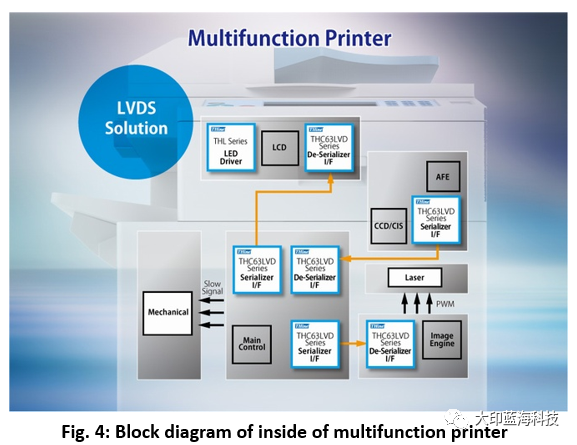

现在,LVDS SerDes有多种产品在销售中。接下来将以THine Electronics的产品系列为例进行详细介绍。

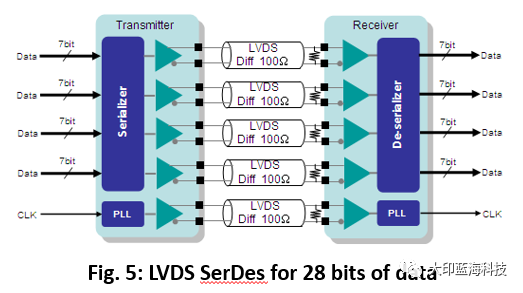

图5是LVDS SerDes的基本构成。

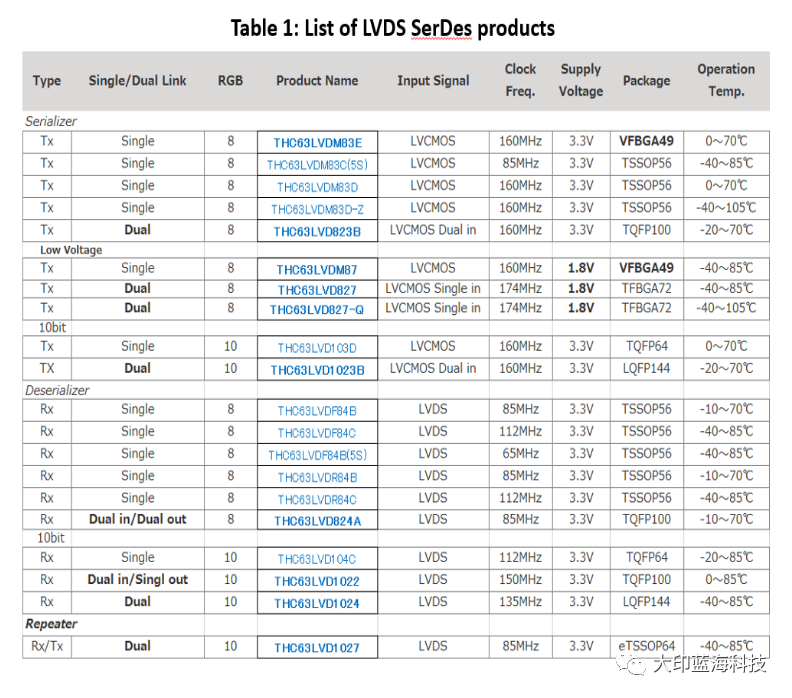

1、在工作电压为3.3V的普通产品以外,可在串行转换器上按照LVDS规格的同时提供1.8V的低工作电压的产品。一般情况下电源电压降低,LVDS规格中限定的1.2V的输出共通电压(Voc)就很难保持。在一些同行业的竞争对手生产的低电压产品中,Voc就常常会低于1.2V。但THine Electronics的「THC63LVDM87」和「THC63LVD827」可在达到1.8V的低工作电压环境时,输出共通电压(Voc)在到达收信侧的串行解串器时仍能维持最合适的1.2V。

2、产品涵盖可应对单连接和双连接的各个系列。比如RGB各10bit的图像信号传送用单连接的串行转换器「THC63LVD103D」和串行解串器「THC63LVD104C」,其双连接版则为串行转换器「THC63LVD1023B」和串行解串器「THC63LVD1024」。使用双连接产品可以简单地使数据传送带宽放大。比如单连接产品最多只能对应1080I;但使用双连接产品可以对应1080P。此外,我们还有RGB各8bit的双连接产品,具体产品有串行转换器「THC63LVD823B」和串行解串器「THC63LVD824A」等。这些产品可以应用于基板间及机箱内通路宽度较宽的数据通信用途上。

3、我们还有可以选择使用脉冲上升沿或脉冲下降沿来控制取得数据的时间的产品。在液晶屏等用途上会用脉冲下降沿;但一般的数据传输时所使用的串行接口则会使用脉冲上升沿。我们的产品中产品型号上如LVDR这样带「R」的产品是对应使用脉冲上升沿的;LVDF这样带「F」的产品则是对应使用脉冲下降沿。「LVDM」和「LVD」的产品则可以同时对应两种方式;可以通过pin设定来决定使用哪一种。

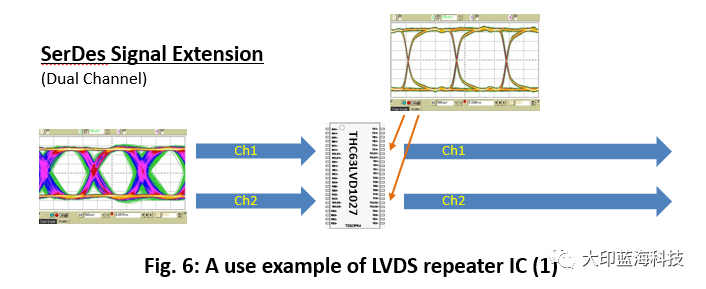

4、我们还有RepeaterIC产品。型号是「THC63LVD1027」。使用RepeaterIC,可以在接收LVDS SerDes输出的信号后,吸收通过配线时产生的扭曲及波动,调整成电压轴和时间轴都在理想状态下的LVDS信号后再一次传输(图6)。

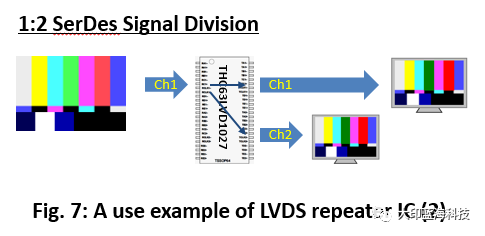

这样就可以使数据的传输距离(配线长度)大幅度加长。将其设置在传送路径的中部可使传送距离(配线长度)延伸2倍。此外,还能使至今仍很困难的1个频的图像信号输入分配到2频这样一种LVDS SerDes的信号分配成为可能(图7)。

5、可对应的时钟频率范围在8M~160MHz这一较大范围。比如「THC63LVD103D」等产品就能对应较大的时钟频率范围。频率范围大就能适用于各种并串通路;也能提高设计的灵活性。

6、我们还有将LVDS的输出控制在更低振幅的产品。如前所述:LVDS SerDes一般在3.5mA的电流电源与100Ω的終端阻力下使用。因此振幅也在350mV。使用LVDS低振幅型的RS(Reduce Swing),可使振幅降低到200mV。因此可以抑制EMI达到低耗电。

此外,我们还有适合搭载在摄像机模组等小型电子设备上的、实际面积为5mm×5mm及超小的49pin VFBGA封印产品;适用车载设备的则有工作温度范围在−40~+105℃这样广的范围下的产品;这些都是我们的特点。

综上所述,THine Electronics有着众多LVDS SerDes产品,可以对应各种不同用途。但是,仅靠LVDS SerDes还不能满足所有的串行接口需求。要对应要求有4K的倍速和鲜艳的色彩、8K这样的高分辨率信号以及高速的远距离传输的用途就比较困难。因此THine Electronics开发出了更高速的串行接口技术。

08

关于HDMI 采用的TMDS过渡调制差分信号

过渡调制差分信号,也被称为最小化传输差分信号(TMDS:Transition Minimized Differential signal),是指通过异或及异或非等逻辑算法将原始信号数据转换成10位,前8位数据由原始信号经运算后获得,第9位指示运算的方式,第10位用来对应直流平衡(DC-balanced,就是指在编码过程中保证信道中直流偏移为零,电平转化实现不同逻辑接口间的匹配),转换后的数据以差分传动方式传送。

过渡调制差分信号,也被称为最小化传输差分信号,是指通过异或及异或非等逻辑算法将原始信号数据转换成10位,前8位数据由原始信号经运算后获得,第9位指示运算的方式,第10位用来对应直流平衡(DC-balanced,就是指在编码过程中保证信道中直流偏移为零,电平转化实现不同逻辑接口间的匹配),转换后的数据以差分传动方式传送。这种算法使得被传输信号过渡过程的上冲和下冲减小,传输的数据趋于直流平衡,使信号对传输线的电磁干扰减少,提高信号传输的速度和可靠性

在上世纪九十年代晚期,Silicon Image公司开始采用面板连接、数字可视接口(DVI)和高清多媒体接口(HDMI)的形式向显示行业推广其所有权标准——最小化传输差分信号(TMDS:Transition Minimized Differential signal)。在该情况下,发射端混合了具有在铜导线上降低EMI特性的更高级编码算法,从而使得接收端具有健壮的时钟恢复性能。

8位/10位编码是一个二阶处理,它是将一个8位的输入信号转换成10位的编码。和LVDS相似的是,它采用了差分信号来降低EMI及提高精确的信号传输速率。还和LVDS相似的是,它是一个串行的传输设计。

应用: DVI技术已成功的应用于PC领域,HDMI技术也成功的推向了消费电子市场。但是,TMDS并没有因此成为广泛使用的面板接口标准。相反,没有专利费的LVDS已被普遍使用。此外,当前的DVI版本并不能更新,而且具有物理上、功能上及成本上的局限。

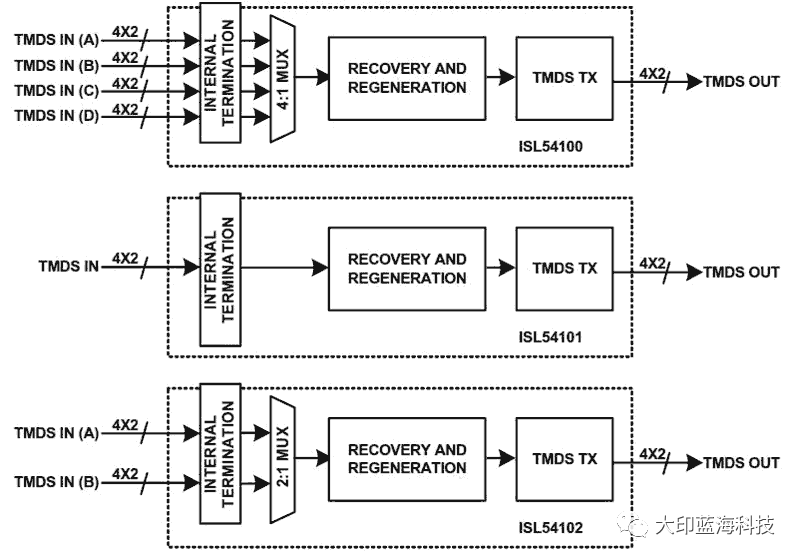

HDMI 4:1 Mux & Repeater - ISL54100 (with CDR Regeneration)

声明:

11月09日-10日将在上海举办一期SerDes课程,本期短期课程旨在通过提供 SerDes 空间所需的系统级和电路级概念来弥补这些差距。课程将从传统的模拟架构开始,逐步发展到今天基于 DSP 的均衡和定时恢复。本课程从传统的模拟混合信号 SerDes 架构开始,该架构如今仍适用于 UCI、HBM 和 XSR 解决方案。之后,我们将转向 ADC-DSP 解决方案。

--点击图片即转至课程页面

今天小编带来了:ISSCC2023套餐,里面有文章、Short Course、PPT、Tutorial等,同学可以拿回去自己学习研究。

1、深入理解SerDes(Serializer-Deserializer)之一

2、深入理解SerDes(Serializer-Deserializer)之二

3、科普:深入理解SerDes(Serializer-Deserializer)之三

4、资深工程师的ESD设计经验分享

5、干货分享,ESD防护方法及设计要点!

6、科普来了,一篇看懂ESD(静电保护)原理和设计!

7、锁相环(PLL)基本原理 及常见构建模块

8、当锁相环无法锁定时,该怎么处理的呢?

9、高性能FPGA中的高速SERDES接口

10、什么是毫米波技术?它与其他低频技术相比有何特点?

11、如何根据数据表规格算出锁相环(PLL)中的相位噪声

12、了解模数转换器(ADC):解密分辨率和采样率

13、究竟什么是锁相环(PLL)

14、如何模拟一个锁相环

15、了解锁相环(PLL)瞬态响应

16、如何优化锁相环(PLL)的瞬态响应

17、如何设计和仿真一个优化的锁相环

18、锁相环(PLL) 倍频:瞬态响应和频率合成

19、了解SAR ADC

20、了解 Delta-Sigma ADC

21、什么是数字 IC 设计?

22、什么是模拟 IC 设计?

23、什么是射频集成电路设计?

24、学习射频设计:选择合适的射频收发器 IC

25、连续时间 Sigma-Delta ADC:“无混叠”ADC

26、了解电压基准 IC 的噪声性能

27、数字还是模拟?I和Q的合并和分离应该怎么做?

28、良好通信链路性能的要求:IQ 调制和解调

29、如何为系统仿真建模数据转换器?

30、干货!CMOS射频集成电路设计经典讲义(Prof. Thomas Lee)

31、使用有效位数 (ENOB) 对 ADC 进行建模

32、以太网供电 (PoE) 的保护建议

33、保护高速接口的设计技巧

34、保护低速接口和电源电路设计技巧

35、使用互调多项式和有效位数对 ADC 进行建模

36、向 ADC 模型和 DAC 建模添加低通滤波器

37、揭秘芯片的内部设计原理和结构

38、Delta-Sigma ADCs中的噪声简介(一)

39、Delta-Sigma ADCs中的噪声简介(二)

40、Delta-Sigma ADCs 中的噪声简介(三)

41、了解Delta-Sigma ADCs 中的有效噪声带宽(一)

42、了解Delta-Sigma ADCs 中的有效噪声带宽(二)

43、放大器噪声对 Delta-Sigma ADCs 的影响(一)

44、放大器噪声对 Delta-Sigma ADCs 的影响(二)

45、参考电压噪声如何影响 Delta Sigma ADCs

46、如何在高分辨率Delta-Sigma ADCs电路中降低参考噪声

47、时钟信号如何影响精密ADC

48、了解电源噪声如何影响 Delta-Sigma ADCs

49、运算放大器简介和特性

50、使用 Delta-Sigma ADCs 降低电源噪声的影响

51、如何设计带有运算放大器的精密电流泵

52、锁定放大器的基本原理

53、了解锁定放大器的类型和相关的噪声源

54、用于降低差分 ADC 驱动器谐波失真的 PCB 布局技术

55、干货!《实用的RFIC技术》课程讲义

56、如何在您的下一个 PCB 设计中消除反射噪声

57、硅谷“八叛徒”与仙童半导体(Fairchild)的故事!

58、帮助你了解 SerDes!

1、免费公开课:ISCAS 2015 :The Future of Radios_ Behzad Razavi

2、免费公开课:从 5 微米到 5 纳米的模拟 CMOS(Willy Sansen)

3、免费公开课:变革性射频毫米波电路(Harish Krishnaswamy)

4、免费公开课:ESSCIRC2019-讲座-Low-Power SAR ADCs

5、免费公开课:ESSCIRC2019-讲座-超低功耗接收器(Ultra-Low-Power Receivers)

6、免费公开课:CICC2019-基于 ADC 的有线收发器(Yohan Frans Xilinx)

7、免费公开课:ESSCIRC 2019-有线与数据转换器应用中的抖动

8、免费公开课:ISSCC2021 -锁相环简介-Behzad Razavi

9、免费公开课:ISSCC2020-DC-DC 转换器的模拟构建块

10、免费公开课:ISSCC2020-小数N分频数字锁相环设计

11、免费公开课:ISSCC2020-无线收发器电路和架构的基础知识(从 2G 到 5G)

12、免费公开课:ISSCC2020-从原理到应用的集成变压器基础

13、免费公开课:ISSCC2021-射频和毫米波功率放大器设计的基础

14、免费公开课:ISSCC 2022-高速/高性能数据转换器系列1(Prof. Boris Murmann)

15、免费公开课:ISSCC 2022-高速/高性能数据转换器系列2(Dr. Gabriele Manganaro)

16、免费公开课:ISSCC 2022-高速/高性能数据转换器系列3(Prof. Pieter Harpe)

17、免费公开课:ISSCC 2022-高速/高性能数据转换器系列4(Prof. Nan Sun)

点击下方“公众号”,关注更多精彩

半导体人才招聘服务平台