本文来自“2023新型算力中心调研报告(2023)”。更多内容参考“《海光CPU+DCU技术研究报告合集(上)》 ”,“《海光CPU+DCU技术研究报告合集(下)》 ”和“龙芯CPU技术研究报告合集”,“UCIe白皮书(终版)”。

UniversalChiplet Interconnect Express (UCIe)® 是一个开放的行业互连标准,可以实现小芯片之间的封装级互连,具有高带宽、低延迟、经济节能的优点。能够满足整个计算领域,包括云端、边缘端、企业、5G、汽车、高性能计算和移动设备等,对算力、内存、存储和互连不断增长的需求。UCIe 具有封装集成不同Die的能力,这些Die可以来自不同的晶圆厂、采用不同的设计和封装方式。

实现Chiplets封装集成的动机有很多。为了满足不断增长的性能需求,芯片面积不断增加,有些设计甚至会超出掩模版面积的限制,比如具有数百个核心的多核 CPU,或扇出非常大的交换[曹1] 电路(Switch)。即使在设计不超过面积限制的情况下,改用多个小芯片集成封装的方式也更有利于提升良率,实现芯片的跨市场复用。另外,多个相同Die的集成封装能够适用于大规模的应用场景。

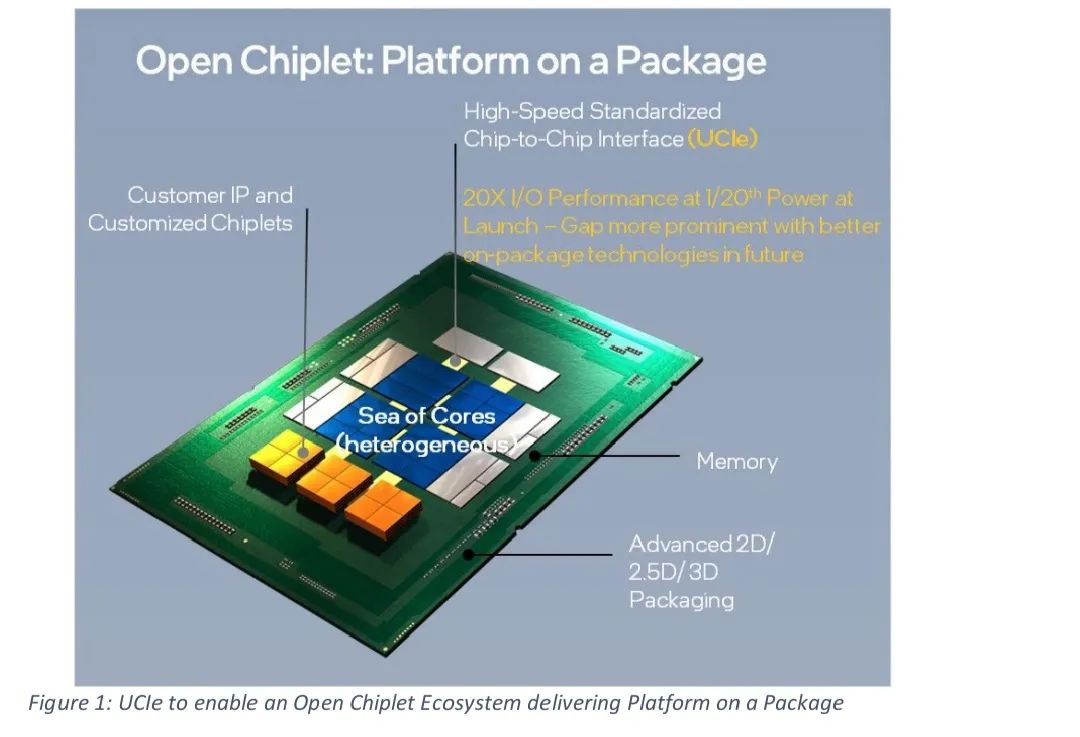

图1:UCIe开启开放式封装级生态系统交付平台

实现Chiplet封装集成的另一个动机是为了从产品和项目的角度降低整体投资组合成本,并抢占产品市场。例如,图 1 所示的处理器核心可以最先进的工艺节点,用更高的成本换取极致的节能性能,而内存和 I/O 控制器功能可以复用已经建立好的旧工艺节点(n -1 或 n-2)。采用这种划分方式,可以减小Die的面积,从而提高产量。如图 2 所示,跨工艺节点的 IP 移植成本很高,而且随着工艺节点的进步,该成本增长非常迅速。若采用多Die集成模式,由于Die的功能不变,我们不必对其IP进行移植,便可在节省成本的同时实现抢占市场的可能。Chiplet封装集成模式还可以使用户能够自主选择Die的数量和类型,从而针对不同的产品类型做出不同的权衡。例如,用户可以根据自己的具体需求挑选任意数量的计算、内存和I/O Die,并无需针对具体需求进行Die的自主设计,这有利于降低产品的SKU成本。

Chiplet的封装集成允许厂商能够以快速且经济的方式提供定制解决方案。如图 1 所示,不同的应用场景可能需要不同的计算加速能力,但可以使用同一种核心、内存和 I/O。Chiplet的封装集成还允许厂商根据功能需求对不同的功能单元应用不同的工艺节点,并实现共同封装。例如,内存、逻辑、模拟和光学器件可以被应用不同的工艺技术,然后和Chiplet封装到一起。由于相比板级互连,封装级互连具有线长更短、布线更紧密的优点,因此,像内存访问这种需要高带宽的应用场景都可以以封装级集成的方式实现(例如HBM,High Bandwidth Memory)。

UCIe是封装互连的战略性成果,它以前瞻性的方式渗入各种应用模型,并蓄势待发,志在扭转行业未来。

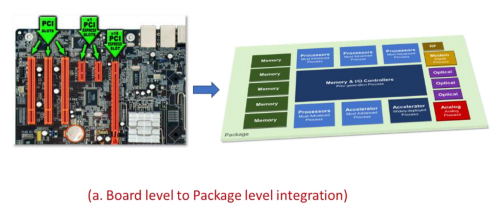

UCIe 的 In package 本质就是将整个芯片封装视作主板,在基板上组装大量的芯粒,包括各种处理器、收发器,以及硬化的 IP。整体而言,UCIe 是一个基于并行连接的高性能系统接口,主要是面向 PCIe/CXL 设备(芯片)的“ 组 装”,如 CPU、GPU、DSA、FPGA、ASIC 等的互联。随着人工智能时代的到来,异构计算已经是显学,原则上,只要功率密度允许,这些异构计算单元的高密度集成可以交给 UCIe 完成。

△ UCIe的In package 本质就是将整个芯片封装视作主板

除了集成度的考虑,标准化的 Chiplet 也带来了功能和成本的灵活性,对于不需要的单元,在制造时不参与封装即可——而对于传统的处理器而言,对部分用户无用的单元常常成为无用的“暗硅”,意味着成本的浪费。一个典型的例子就是 DSA,如英特尔第四代可扩展至强处理器中的若干加速器,用户可以付费开启,但是,如果用户不付费呢?这些 DSA 其实已经制造出来了。

UCIe 包括协议层(Protocol Layer)、适配层(Adapter Layer)和物理层(Physical Layer)。协议层支持 PCIe 6.0、CXL 2.0 和 CXL 3.0,也支持用户自定义。根据不同的的封装等级,UCIe 也有不同的 Package module。通过用 UCIe 的适配层和 PHY 来替换 PCIe/CXL 的 PHY 和数据包,就可以实现更低功耗和性能更优的 Die-to-Die 互连接口。

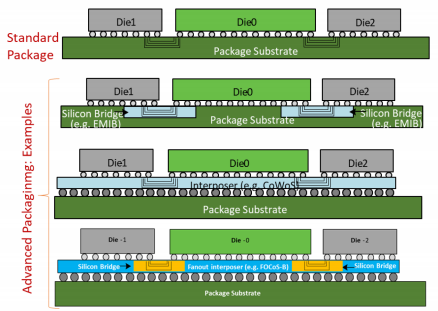

△ UCIe 对两种封装的划分

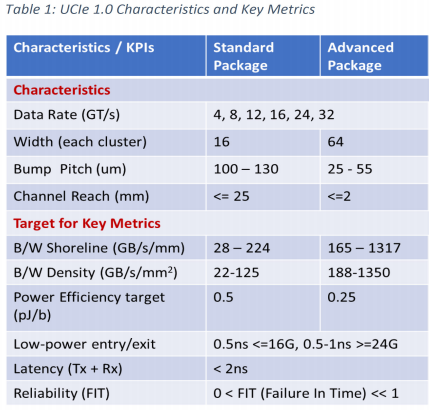

UCIe 考虑了两种不同等级的封装:标准封装(Standard Package)和先进封装(Advanced Package),凸块间距、传输距离和能耗将有数量级的差异。譬如对于先进封装,凸块间距(Bump Pitch)为 25~55μm,对应的是采用硅中介层为代表的 2.5D 封装技术的特点。以英特尔的 EMIB 为例,当前的凸块间距即为 50μm 左右,未来将向 25μm,甚至 10μm 演进。台积电的 InFO、CoWoS 也会有类似的规格和演进。而标准封装(2D)的规格对应的是目前应用最为广泛的有机载板。

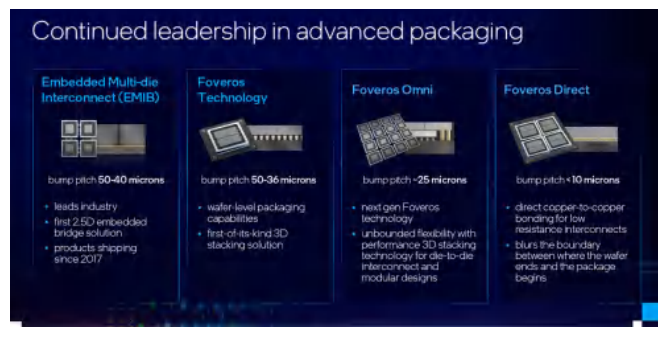

△ 英特尔先进封装的凸块间距演进

不同封装的信号密度也是有本质差异的,如标准封装模块对应的是 16 对数据线(TX、RX),而高级封装模块包含 64 对数据线,每 32 个数据管脚还提供 2 个额外的管脚用于 Lane 修复。如果需要更大的带宽,可以扩展更多的模块,且模块的频率是可以独立的。

△ UCIe 规划了两种等级封装的性能目标

当然,UCIe 没有必要急于跟进封装技术的极限,更高密度的键合通常还是为私有(协议)接口准备的,典型的如存储器(SRAM、HMB、3D NAND)的内部。UCIe 能够满足通用总线的连接需求即可,如 PCIe、UPI、NVLink 等。值得一提的是,UCIe 对高速 PCIe 的深度捆绑,注定了它“嫌贫爱富”的格局。

《FMS 2023闪存峰会CXL合集(1)》

3、数据中心绿色设计白皮书(2023)

4、新型数据中心高安全技术体系白皮书

数据中心绿色设计白皮书(2023)

存储系统性能和可靠性基础知识

云基建专题:AI驱动下光模块趋势展望及弹性测试

精华:数据库系统的分类和评测研究

可重构计算:软件可定义的计算引擎

近存及存内计算专题简介

集装箱冷板式液冷数据中心技术规范

浸没式液冷发展迅速,“巨芯冷却液”实现国产突破

两相浸没式液冷—系统制造的理想实践

浸没液冷服务器可靠性白皮书

天蝎5.0浸没式液冷整机柜技术规范

AIGC加速芯片级液冷散热市场爆发

某液冷服务器性能测试台的液冷系统设计

《智能存储与磁盘故障预测合集》

《内存技术应用研究及展望合集》

免责申明:本号聚焦相关技术分享,内容观点不代表本号立场,可追溯内容均注明来源,发布文章若存在版权等问题,请留言删除,谢谢。

温馨提示:扫描二维码关注“全栈云技术架构”公众号,点击阅读原文进入“全栈云技术知识”星球获取10000+技术资料。