先进封装路线图

芝能智芯出品

【Advanced Packaging and Heterogeneous Integration】

信息与通信技术(ICT)引发了前所未有的数据激增,要求对其处理、存储和安全性提出创新性解决方案。传统半导体技术依赖特征尺寸的缩小,但已经接近其物理极限。随着行业力图提高系统性能和能效,转向新技术节点的速度减缓。"More Moore"(传统晶体管尺寸缩放)和"More than Moore"(异构集成)的整合变得迫在眉睫。异构集成是实现具有成本效益的封装系统(SiPs)的关键,对于实现下一代计算和通信系统至关重要。由异构集成支持的先进封装提供了在产品密度和尺寸方面进行创新的替代途径。异构集成将是未来的关键技术方向,对应对ICT领域的重大变革提出了要求,包括需要用于智能界面的模拟硬件、新型内存和存储解决方案、应对新兴安全挑战的硬件、人工智能(AI)以及应对普通计算带来的能耗指数级增长。

ICT行业面临的主要挑战之一是能源消耗的指数级增长,这已经超过了尺寸缩放所取得的改进。能源消耗每三年翻倍一次,迫切需要探索新的计算范式。路线图总体目标是发现具有全新计算轨迹的计算范式和架构,实现能效提高超过1,000,000倍的显著改进,主要重点是开发能够无缝集成模拟和数字系统的技术。这种集成涵盖了广泛领域,包括神经形态计算和量子计算、传感技术、光子学和无线通信。通过在这些领域实现成功集成,为ICT领域的变革性进展铺平道路。

异构集成技术的进步对于满足ICT领域预期的地震性变化至关重要,包括:

总体目标:发现具有全新计算轨迹的计算范式和架构,实现能效提高超过1,000,000倍的显著改进。

章节目标:开发集成模拟和数字系统的技术,包括神经形态计算、量子计算、传感技术、光子学和无线通信。

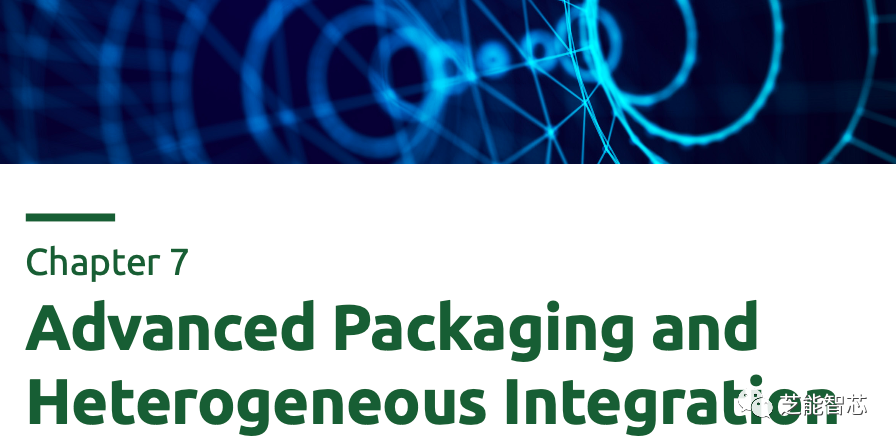

提早介入设计流程

在设计过程的早期阶段,需要参与系统和封装的分析,将设计划分为各种芯片片段,并评估在计算、数据传输和制造成本方面的必要权衡。设计和验证工具(例如SystemVerilog)需要整合封装设计和规划知识,以支持协同设计工作流程。对异构集成系统的早期预测性分析是至关重要的,以最小化在架构/微体系结构定义和设计实施之间的迭代成本。

异构集成系统的综合工具

为了实现芯片-封装协同设计,有必要在综合流程的每个步骤中考虑封装,包括架构定义、RTL设计、布局与布线、验证以及时序/功耗分析。新的一套工具还需要在彼此之间具有顺畅的接口,并支持未来的芯片片段设计工具包。异构集成综合的独特挑战包括芯片片段之间时序分析、热/机械应力分析,以及各个组件的电源传递和完整性。

测试与可靠性

异构系统包含具有显著不同电气、机械和热性质的多个组件。未来对异构系统的测试需要提供足够的模块性,以应对每个组件的特定测试方法,平衡覆盖范围、复杂性和成本。内建自测试(例如内建自测试BIST)是一种首选解决方案,但需要更多关于多个功能的联合测试的研究。随着2.5D/3D集成中各个组件之间的热/机械相互作用不断增加,可靠性评估需要从当前的每个单独模块的经验/统计方法转向构建物理可靠性模型,描述它们在产品级别上的相关性。

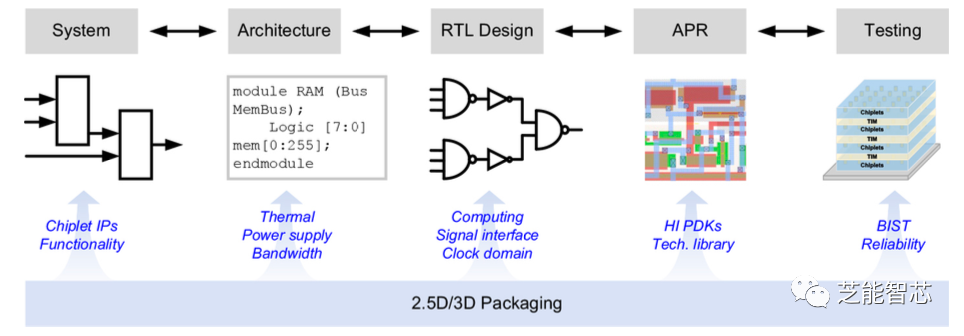

下一代互联技术

在使用更细的晶体管节点(小于20纳米)缩小芯片的成本优势已经不再明显。这就需要采取一种新方法,即将单片式芯片分解成较小的单元,或者称之为芯片片段。为了通过异构集成实现设备芯片片段和被动组件的功能扩展,基板必须从芯片载体转变为集成平台。这个集成平台的推动特性需要新的先进封装方法来满足这些基本要求,包括:

芯片片段的广泛应用预计将持续增长,因为行业朝着为每个应用定制的更高性能和低功耗解决方案发展,下一代封装技术需要支持这种芯片片段的爆炸性增长。