注 ▲射频美学 ▲ ,一起学习成长

这是射频美学的第1427期分享。

来源 | 整编;

微圈 | 进微信群,加微信: RFtogether521 ;

备注 | 昵称+地域+产品及岗位方向 (如大魔王+上海+芯片射频工程师);

宗旨 | 看到的未必是你的,掌握底层逻辑才是。

CP是对wafer进行测试,检查fab厂制造的工艺水平,CP测试的项目较多,较全。FT是对package进行测试,检查封装厂制造的工艺水平,FT测的项目较少,但都是关键项目,条件严格。

对于测试项来说,有些测试项在CP时会进行测试,在FT时就不用再次进行测试了,节省了FT测试时间,但也有很多公司只做FT不做CP(如果FT和封装yield高的话,CP就失去意义了)。但是有些测试项必须在FT时才进行测试(不同的设计公司会有不同的要求)。

在测试方面,CP比较难的是探针卡的制作,并行测试的干扰问题。FT相对来说简单一点。

还有一点,memory测试的CP会更难,因为要做redundancy analysis,写程序很麻烦。

CP在整个制程中算是半成品测试,目的有2个,

•1是监控前道工艺良率,•2是降低后道成本(避免封装过多的坏芯片),

其能够测试的项比FT要少些。

最简单的一个例子,碰到大电流测试项CP肯定是不测的(探针容许的电流有限),这项只能在封装后的FT测。

不过许多项CP测试后,FT就可以免掉不测了(可以提高效率),所以有时会觉得FT的测试项比CP少很多。

CP不是制造(FAB)测的!而CP的项目是从属于FT的(也就是说CP测的只会比FT少),项目完全一样的;不同的是卡SPEC而已;

因为封装都会导致参数漂移,所以CP测试SPEC收的要比FT更紧以确保最终成品FT良率。

还有相当多的DH把wafer做成几个系列通用的die,在CP是通过trimming来定向确定做成其系列中的某一款,这是解决相似电路节省光刻版的最佳方案;

所以除非你公司的wafer封装成device是唯一的,且WAT良率在99%左右,才会盲封的。

CP是把坏的Die挑出来,可以减少封装和测试的成本。可以更直接的知道Wafer 的良率。

FT是把坏的chip挑出来;检验封装的良率。

现在对于一般的wafer工艺,很多公司都把CP给省了,减少成本。

CP对整片Wafer的每个Die来测试,而FT则对封装好的Chip来测试。CP Pass 才会去封装。然后FT,确保封装后也Pass。

WAT是Wafer Acceptance Test,对专门的测试图形(test key)的测试,通过电参数来监控各步工艺是否正常和稳定;

CP是wafer level的chip probing,是整个wafer工艺,包括backgrinding和backmetal(if need),对一些基本器件参数的测试,如vt(阈值电压),Rdson(导通电阻),BVdss(源漏击穿电压),Igss(栅源漏电流),Idss(漏源漏电流)等,一般测试机台的电压和功率不会很高;

FT是packaged chip level的Final Test,主要是对于这个(CP passed)IC或Device芯片应用方面的测试,有些甚至是待机测试;

Pass FP还不够,还需要做process qual 和product qual CP 测试对Memory来说还有一个非常重要的作用,那就是通过MRA计算出chip level 的Repair address,通过Laser Repair将CP测试中的Repairable die 修补回来,这样保证了yield和reliability两方面的提升。

Pass FP:这里的"Pass FP"可能指的是通过Failure Analysis(故障分析)的过程。在这个过程中,对可能存在的故障或问题进行检测和识别,并对其进行修复和改进。

process qual:过程质量保证(process qual)是指通过严格控制生产或服务过程的质量标准,以确保产品或服务的质量达到预期水平。

product qual:产品品质保证(product qual)是一种质量控制方法,以确保产品或服务的质量符合客户的需求和期望。

CP 测试:这里的"CP"可能指的是Copy Protection(复制保护)。这是一种保护数字内容免遭未经授权的复制、分发或展示的技术。这种测试的目的是为了确保复制保护机制的有效性和安全性。

MRA:MRA可能指的是Memory Read Access(内存读取访问)。这通常涉及到在计算机内存中读取数据的过程。

chip level:在电子工程中,"chip level"通常指的是在芯片级别进行操作或分析。这可能涉及到对集成电路(Integrated Circuit)或其他微型电子设备进行测试、修复或改进。

Rerepair address:这可能指的是在内存中用于修复或替换数据的地址。这通常涉及到数据存储和访问的过程。

Laser Repair:激光修复是一种用于修复或替换半导体芯片中损坏部分的工艺。这种技术使用激光束来消除损坏的电路元件,并替换为新的、健康的元件。

yield:这里指的是生产率或产量。这是衡量生产效率或生产出的产品数量的指标。

reliability:可靠性是指产品或服务在特定条件下、在一定时间内完成特定功能的能力。这里的"reliability"指的是产品或服务的可靠性水平。

这里的“DH”指的是“Design House”,即设计公司。这些公司通常为电子设备制造商提供芯片设计和芯片组解决方案。它们可能会将wafer(晶圆)做成几个系列通用的die(芯片),以提供给不同的客户使用。

“WAT”可能是指“Wafer Acceptance Test”,即晶圆接受测试。这是在半导体制造过程中进行的一种测试,用于确保晶圆的质量和可靠性。

“device”在这里指的是通过WAT测试后的芯片设备,即将wafer封装成一个个独立的芯片。

“盲封”在这里可能指的是在不知道芯片具体功能或规格的情况下进行封装。通常情况下,为了确保封装的质量和可靠性,需要进行严格的测试和验证。如果公司的晶圆封装成芯片的过程是唯一的,且WAT良率在99%左右,那么就可以进行盲封,即在不了解芯片具体功能或规格的情况下进行封装。

据我所知盲封的DH很少很少,风险实在太大,不容易受控。

•WAT:wafer level 的管芯或结构测试•CP:wafer level 的电路测试含功能•FT:device level 的电路测试含功能 CP=chip probing FT=Final Test

CP 一般是在测试晶圆,封装之前看,封装后都要FT的。不过bump wafer是在装上锡球,probing后就没有FT

FT是在封装之后,也叫“终测”。意思是说测试完这道就直接卖去做application。

CP用prober,probe card。FT是handler,socket CP比较常见的是room temperature=25度,FT可能一般就是75或90度 CP没有QA buy-off(质量认证、验收)

CP两方面

监控工艺,所以呢,觉得probe实际属于FAB范畴控制成本。Financial fate。我们知道FT封装和测试成本是芯片成本中比较大的一部分,所以把次品在probe中reject掉或者修复,最有利于控制成本

FT: 终测通常是测试项最多的测试了,有些客户还要求3温测试,成本也最大。至于测试项呢,如果测试时间很长,CP和FT又都可以测,像trim项,加在probe能显著降低时间成本,当然也要看客户要求。关于大电流测试呢,FT多些,但是我在probe也测过十几安培的功率mosfet,一个PAD上十多个needle。有些PAD会封装到device内部,在FT是看不到的,所以有些测试项只能在CP直接测,像功率管的GATE端漏电流测试Igss CP测试主要是挑坏die,修补die,然后保证die在基本的spec内,function well。FT测试主要是package完成后,保证die在严格的spec内能够function。

关于3温测试:这是一种特殊的测试方法,它要求在三个不同的温度下对产品进行测试,通常是常温(25℃左右)、高温(如60℃或70℃)和低温(如-20℃或-40℃)。这种测试的目的是为了检查产品在不同温度下的性能和可靠性,以确保产品能在不同环境下正常工作。

关于Trim项:Trim在这里可能指的是微调或者校准的意思。在电子产品测试中,Trim测试通常指的是对一些可以调整的参数进行微调或校准,以确保产品的性能达到最佳。例如,在测试一个频率调整的振荡器时,Trim测试可能包括在不同的频率设置下测试振荡器的性能,以找到最佳的工作频率。

关于加在probe能显著降低时间成本:这可能指的是在测试过程中使用一些特定的测试工具或设备(probe),这些工具或设备可以更快地完成某些测试,从而显著降低测试所需的时间和成本。例如,使用自动化测试设备进行功能测试,可以比手动测试更快、更准确地完成测试,从而降低测试时间和成本。

关于客户要求:客户要求通常是指在产品设计和生产过程中,客户对产品的性能、功能、质量、可靠性等方面的要求。这些要求可能会影响测试的策略和方法,例如客户可能要求进行更严格的测试以保证产品的质量和可靠性。

•CP的难点在于,如何在最短的时间内挑出坏die,修补die。•FT的难点在于,如何在最短的时间内,保证出厂的Unit能够完成全部的Function。

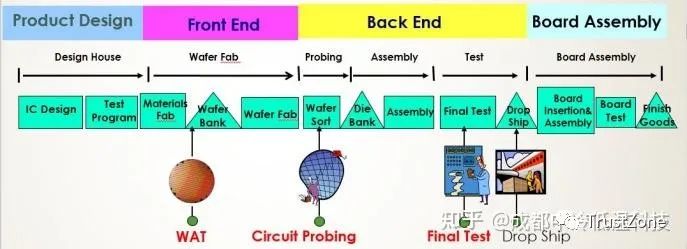

半导体生产流程由

•晶圆制造,•晶圆测试,•芯片封装•封装后测试组成,

而测试环节主要集中在

•WAT,•CP•FT

三个环节。

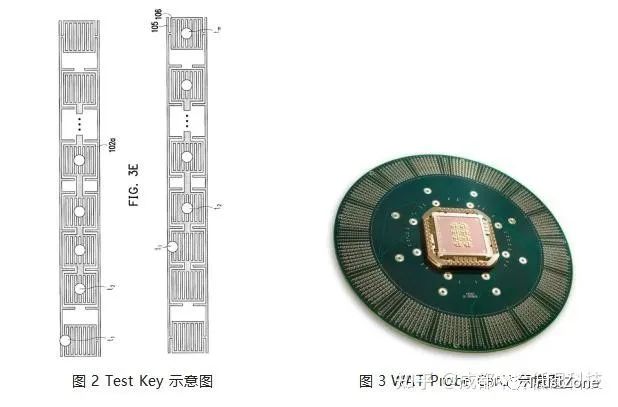

WAT(Wafer Acceptance Test)测试,也叫PCM(Process Control Monitoring),对Wafer 划片槽(Scribe Line)测试键(Test Key)的测试,通过电性参数来监控各步工艺是否正常和稳定.

例如CMOS的电容,电阻, Contact,Metal Line 等,一般在wafer完成制程前,是Wafer从Fab厂出货到封测厂的依据,测试方法是用Probe Card扎在Test Key的Metal Pad上,Probe Card另一端接在WAT测试机台上,由WAT Recipe自动控制测试位置和内容,测完某条Test Key后,Probe Card会自动移到下一条Test Key,直到整片Wafer测试完成。

WAT测试有问题,超过SPEC,一般对应Fab各个Module制程工艺或者机台Shift,例如Litho OVL异常,ETCH CD 偏小,PVD TK偏大等等。WAT有严重问题的Wafer会直接报废。

WAT测试:这是对半导体晶圆(Wafer)的接受测试,用于监控各步工艺是否正常和稳定。它也被称为PCM(Process Control Monitoring),是一种通过电性参数来检验半导体制造过程中工艺控制的方法。

划片槽(Scribe Line)和测试键(Test Key):这是在半导体制造过程中用于WAT测试的两个关键元素。划片槽是沿着晶圆边缘的窄条,用于后续的切割(dicing)过程。测试键则是设在划片槽内或者边缘的特定区域,用于WAT测试。电性参数:这些参数包括电容、电阻、接触以及金属线路等,这些都是在制造过程中需要监控的重要指标。它们反映了半导体器件的电气特性,如电流传导能力、电压承受能力等。

Probe Card:这是一种测试工具,用于连接WAT测试机台和测试键。它的一端与测试键的金属pad接触,另一端连接到WAT测试机台。

WAT Recipe:这应该是某种自动控制测试位置和内容的软件或者程序,它可以根据预先设定的参数来指导Probe Card进行准确的测试。

SPEC:这应该是特定于WAT测试的规格或者标准,超出这个规格或者标准可能意味着半导体制造过程中的某些工艺或者机台存在问题。

Module制程工艺或者机台Shift:这是指在半导体制造过程中,如光刻(Litho)、蚀刻(Etch)、薄膜沉积(PVD)等工艺模块出现问题,或者是机台的运行状态发生变化。

Litho OVL异常、ETCH CD 偏小、PVD TK偏大:这些都是对半导体制造过程中可能出现的问题的描述。其中Litho OVL异常可能指的是光刻过程中的光学临近效应(Optical Proximity Effect)异常;ETCH CD 偏小可能指的是蚀刻后线条宽度小于预期;PVD TK偏大可能指的是薄膜沉积过程中的厚度偏差。

报废:如果WAT测试出现严重问题,比如大量电性参数超出规格,或者连续出现工艺问题,那么整片半导体晶圆会被判定为不合格,进行报废处理。

IC测试键(Test Key)是指用于测试半导体芯片上电路性能和可靠性的特定键。这些键通常在芯片制造过程中设置,用于在生产线上进行自动化测试。测试键的设计和位置取决于芯片的类型和功能。

通过使用测试键,可以测试芯片的电性能、功能和可靠性。测试键通常会连接到芯片上的电路,以便在测试期间测量电流、电压和其他电气参数。此外,测试键还可以用于验证芯片的功能,例如通过施加特定的输入信号并检查输出信号来测试芯片的逻辑功能。

测试键对于确保芯片的质量和可靠性非常重要。通过使用测试键,可以检测到制造过程中的缺陷和问题,并及时采取措施进行修复和改进。因此,测试键是确保半导体芯片质量和性能的重要工具之一。

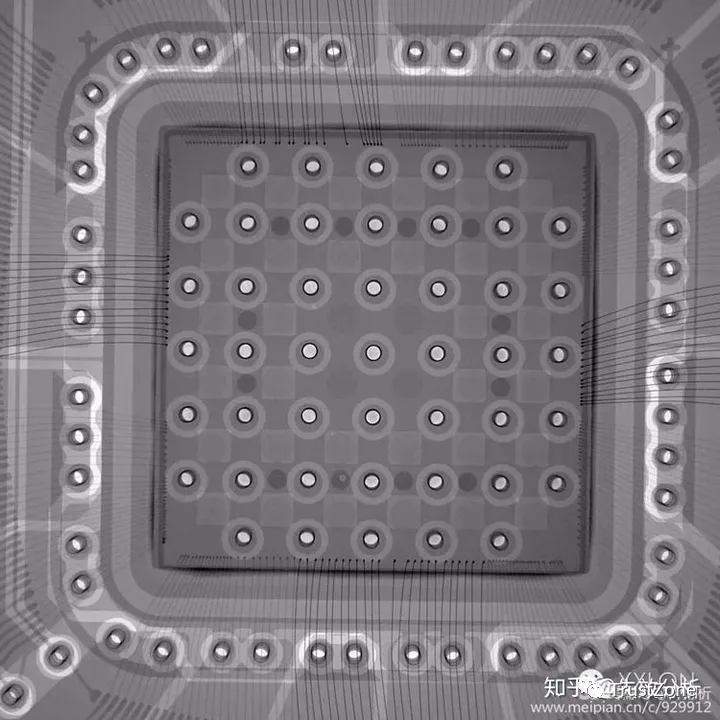

CP(Circuit Probing)也叫“Wafer Probe”或者“Die Sort”,是对整片Wafer的每个Die的基本器件参数进行测试,例如Vt(阈值电压),Rdson(导通电阻),BVdss(源漏击穿电压),Igss(栅源漏电流),Idss(漏源漏电流)等,把坏的Die挑出来,会用墨点(Ink)标记,可以减少封装和测试的成本,CP pass才会封装,一般测试机台的电压和功率不高,CP是对Wafer的Die进行测试,检查Fab厂制造的工艺水平。

CP测试程序和测试方法优化是Test Engineer努力的方向,下面介绍几种降低CP测试成本的方法。

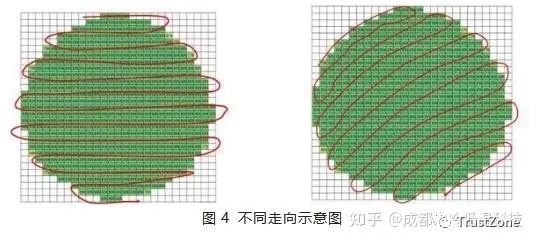

•1.同一个Probe Card可以同时测多个Die,如何排列可以减少测试时间?假设Probe Card可以同时测6个Die,那么是2×3排列还是3×2,或者1×6,都会对扎针次数产生影响,不同的走针方向,也会产生Test时间问题。•2.随着晶圆尺寸越来越大,晶圆上的Die越来越多,很多公司CP Test会采用抽样检查(Sampling Test)的方式来减少测试时间,至于如何抽样,涉及不同的Test Recipe,一些大数据实时监控软件可以在测试的同时按照一定算法控制走针方向,例如抽测到一个Die失效后,Probe Card会自动围绕这个Die周围一圈测试,直到测试没有问题,再进行下一个Die的抽测,这种方法可以明显缩短测试时间。

FT(final test)是对封装好的Chip进行Device应用方面的测试,把坏的chip挑出来,FT pass后还会进行process qual和product qual,FT是对package进行测试,检查封装造厂的工艺水平。

FT的良率一般都不错,但由于FT测试比CP包含更多的项目,也会遇到Low Yield问题,而且这种情况比较复杂,一般很难找到root cause。

广义上的FT也称为ATE(Automatic Test Equipment),一般情况下,ATE通过后可以出货给客户,但对于要求比较高的公司或产品,FT测试通过之后,还有SLT(System Level Test)测试,也称为Bench Test。

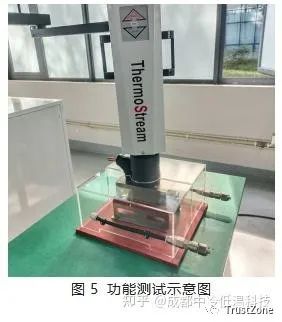

SLT测试比ATE测试更严格,一般是功能测试,测试具体模块的功能是否正常。成都中冷低温的ThermoStream TS-780高低温冲击气流仪以速度、精度和可靠性作为基本设计标准,提供了非常先进的温度测试能力。

温度转换从-55℃到+125℃之间转换约10秒,并有更广泛的温度范围-80℃到+225℃; 经长期的多工况验证,满足更多生产环境和工程环境的要求。

TS-780应用于提供老化测试、特性分析、高低温温变测试、温度冲击测试、失效分析等可靠性试验,用于芯片、微电子器件、集成电路 (SOC、FPGA、PLD、MCU、ADC/DAC、DSP 等) 、闪存 Flash、UFS、eMMC 、PCBs、MCMs、MEMS、IGBT、传感器、小型模块组件等电子元器件/模块冷热测试。

•WAT是在晶圆制造过程中进行的测试,通过对Die与Die之间Scribe Line Test Key电学性能的测试,来监控Fab制程的稳定性;•CP测试是制造完成后,封测之前进行的电学测试,把坏的Die标记出来,减少封装的成本;•FT是Die切割,打磨,封装后进行器件功能性的测试,可以评价封测厂的封装水平,只有所有的测试都通过后,才可以应用到产品上。

声明: 欢迎转发本号原创内容,转载和摘编需经本号授权并标注原作者和信息来源为射频美学。 本公众号目前传播内容为本公众号原创、网络转载、其他公众号转载、累积文章等,相关内容仅供参考及学习交流使用。由于部分文字、图片等来源于互联网,无法核实真实出处,如涉及相关争议,请跟我们联系,我们致力于保护作者知识产权或作品版权,本公众号所载内容的知识产权或作品版权归原作者所有。