在当今快节奏的世界中,半导体设计的创新是一项永恒的需求。对更快、更准确、更创新的解决方案的需求为探索生成式人工智能(#GenerativeAI)在半导体设计开发领域的潜力铺平了道路。能做到吗?当然可以!在本系列文章中,我们将深入探讨令人兴奋的实验,展示生成式人工智能如何彻底改变半导体设计。

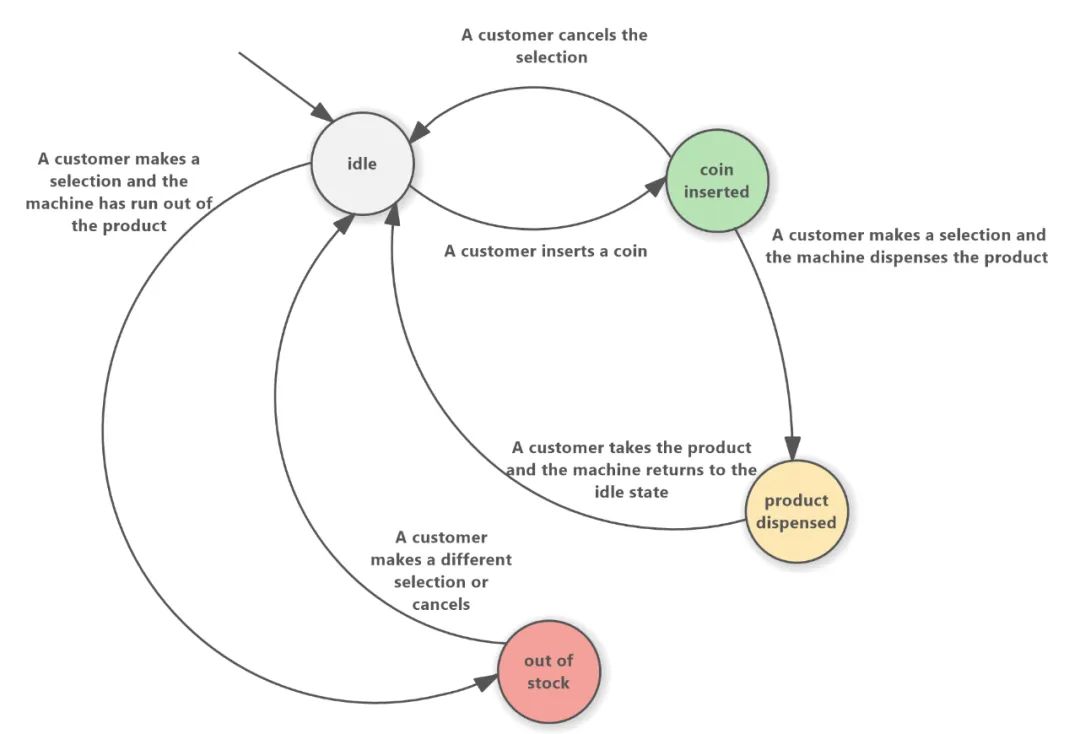

实例 1 - 从 FSM 图到 SV 代码

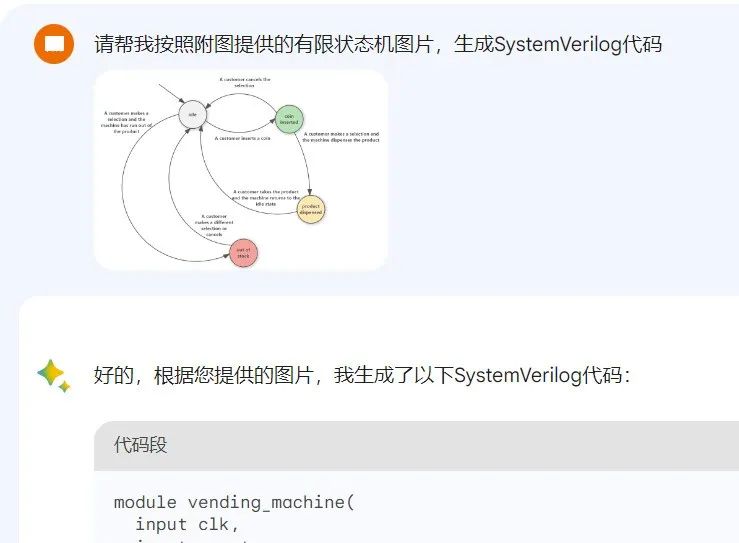

在本例中,谷歌的生成式人工智能模型--BARD 被用来生成一个自动售货机 FSM 的 SystemVerilog 实现。

状态机图片:

代码如下:

// Vending machine FSM// Disclaimer: This code is not tested for correctnessmodule vending_machine (input clk,input reset,input coin_inserted,input product_selected,input product_dispensed,output reg dispense_product,output reg return_coin);// Define the stateslocalparam [2:0] IDLE = 3'b000;localparam [2:0] COIN_INSERTED = 3'b001;localparam [2:0] PRODUCT_SELECTED = 3'b010;localparam [2:0] PRODUCT_DISPENSED = 3'b011;localparam [2:0] OUT_OF_STOCK = 3'b100;// Define the registersreg [2:0] current_state;// Transition logicalways @(posedge clk or posedge reset) beginif (reset) begincurrent_state <= IDLE;end else begincase (current_state)IDLE: beginif (coin_inserted) begincurrent_state <= COIN_INSERTED;end else begincurrent_state <= IDLE;endendCOIN_INSERTED: beginif (product_selected) begincurrent_state <= PRODUCT_SELECTED;end else begincurrent_state <= COIN_INSERTED;endendPRODUCT_SELECTED: beginif (product_dispensed) begincurrent_state <= PRODUCT_DISPENSED;end else if (out_of_stock) begincurrent_state <= OUT_OF_STOCK;end else begincurrent_state <= PRODUCT_SELECTED;endendPRODUCT_DISPENSED: begincurrent_state <= IDLE;endOUT_OF_STOCK: begincurrent_state <= IDLE;endendcaseendend// Output logicalways @(posedge clk) begincase (current_state)PRODUCT_DISPENSED: begindispense_product <= 1'b1;enddefault: begindispense_product <= 1'b0;endendcaseendalways @(posedge clk) begincase (current_state)OUT_OF_STOCK: beginreturn_coin <= 1'b1;enddefault: beginreturn_coin <= 1'b0;endendcaseendendmodule

有限状态机在芯片设计中得到广泛应用,以下是生成式人工智能如何发挥关键作用: