3.2 的工作原理(HOW WORKS)

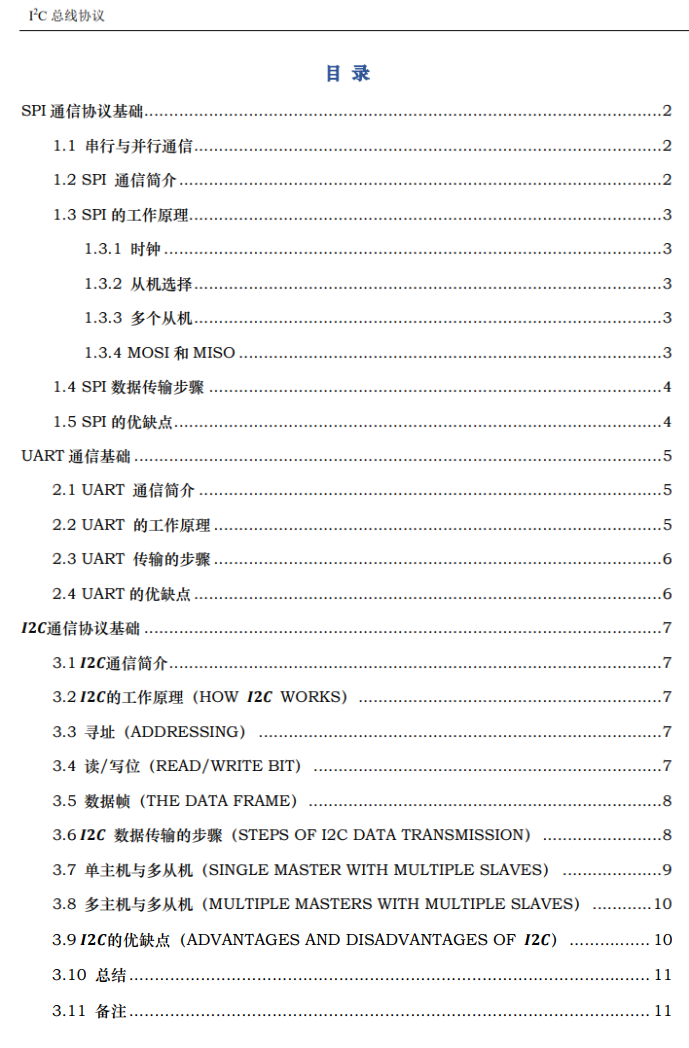

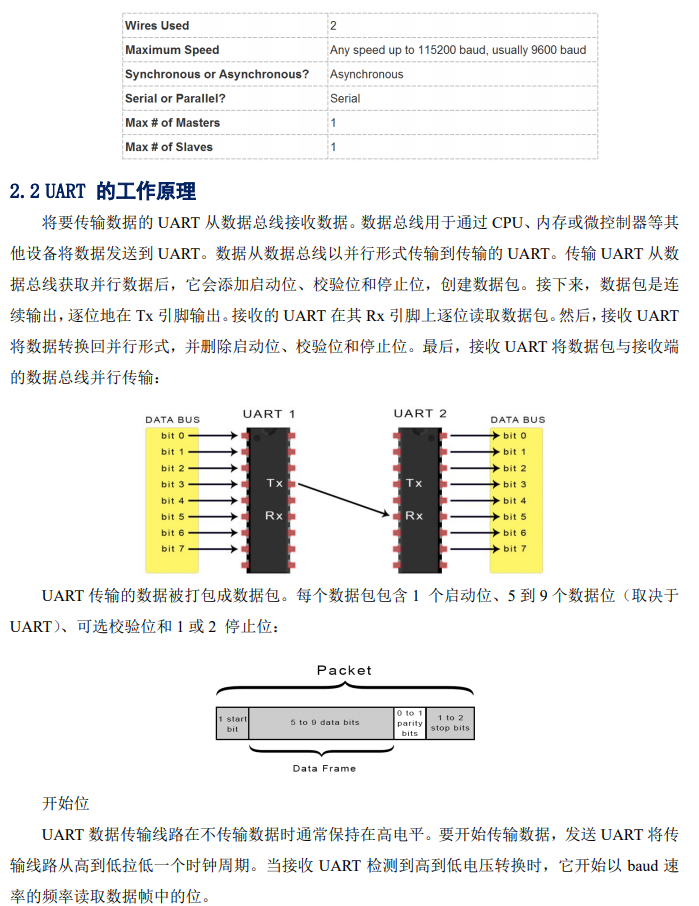

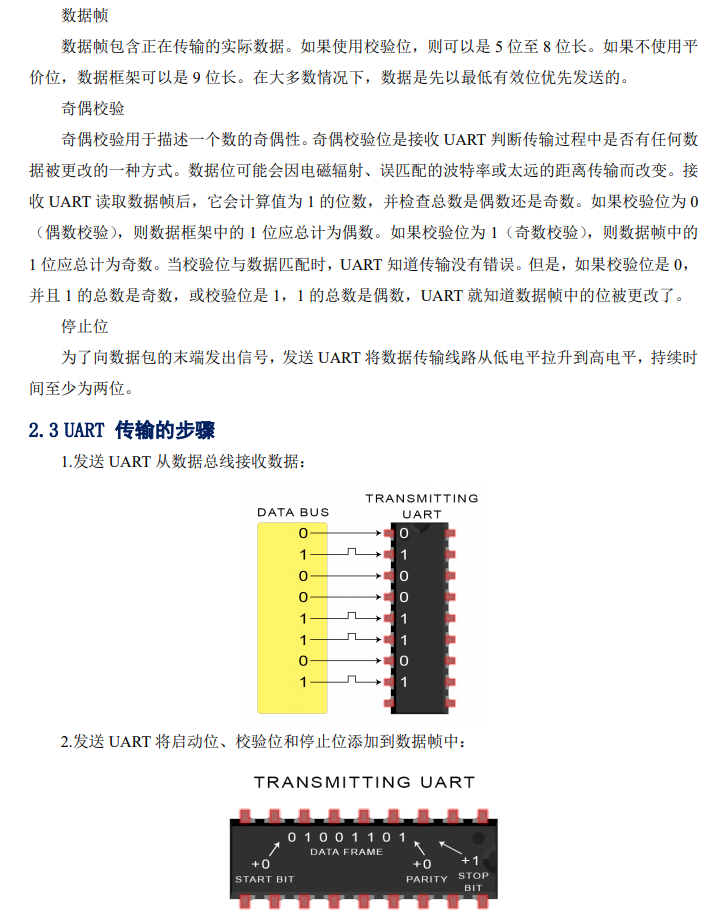

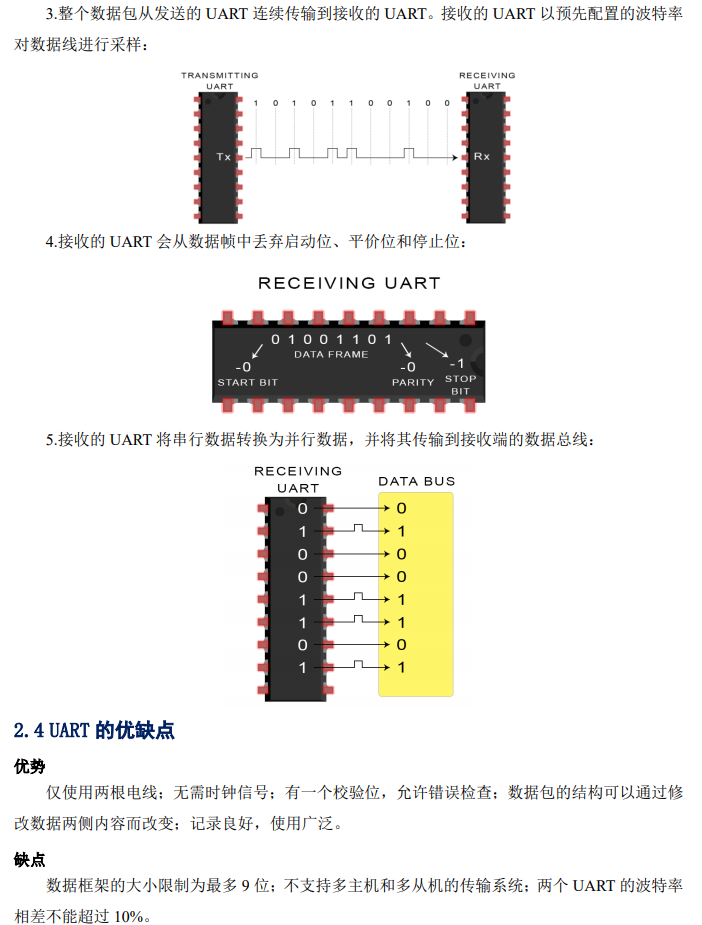

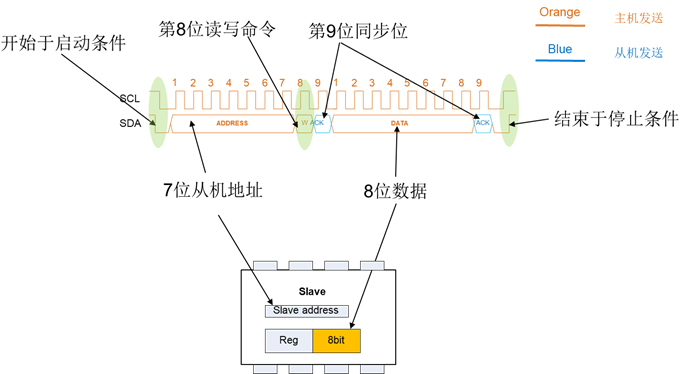

使用 ,数据在消息中传输。消息被分解成数据帧。每条消息都有一个地址帧,其中包含从机的二进制地址,以及一个或多个包含正在传输数据的数据帧。该消息还包括每个数据帧之间的启动和停止条件、读/写位以及ACK/NACK位:

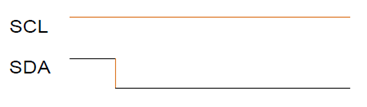

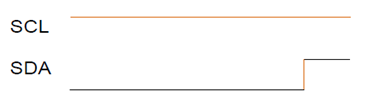

启动条件(StartCondition):SDA 线在SCL线从高到低切换之前从高电位切换到低电位。

停止条件(StopCondition):SDA 线在SCL线从低到高切换之后从低电位切换到高电位。

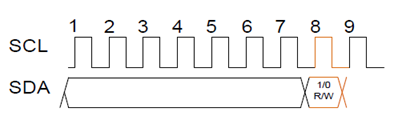

地址帧(AddressFrame):每个从机都有唯一的7位或10位数列,主机可以通过该序列识别从机,主机如果需要向从机发送/接收数据,首先要发送对应从机的地址,然后会匹配总线上挂载的从机的地址。

读/写位(Read/Write Bit):指定主机是向从机发送数据(低电位)还是请求从机发送数据(高电位)的1个位。

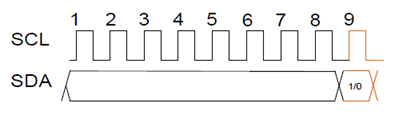

ACK/NACK位(ACK/NACK Bit):在一条消息中,每一帧后都跟随1个确认应答(ACK)/非确认应答(NACK)位。如果一个地址帧或数据帧是被成功接收,一个确认应答位(ACK bit)将从接收设备返回给发送设备。

3.3 寻址(ADDRESSING)

没有像SPI这样的从机片选接口线,所以它需要另一种方式让从机知道数据被发送到它,而不是另一个从机。它需要通过寻址来实现。地址帧始终是新消息中开始位后的第一帧。

主机将它想要与之沟通的从机的地址发送给与之相连的每一个从机。然后,每个从机将从主机发送的地址与自己的地址进行比较。如果地址匹配,它会向主发送低电压ACK位。如果地址不匹配,从机什么都不做,SDA线仍然很高。

3.4 读/写位(READ/WRITE BIT)

在地址帧的末尾包含一个单独的位,用于通知从机,主机是否想向它写数据还是想从它接收数据。如果主机要将数据发送给从机,读/写位是低电位;如果主机请求来自从机的数据,则该位为高电位1。

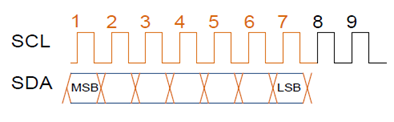

3.5 数据帧(THE DATA FRAME)

在主机检测到从机发出的ACK位后,第一个数据帧已准备好发送。

数据帧始终为8位长,并且首先发送最重要的位。每个数据帧后面都立即有ACK/NACK 位,以验证帧是否已成功接收。在发送下一个数据帧之前,主机或从机(取决于谁发送数据)必须接收ACK位。

在发送完所有数据帧后,主机可以向从机发送停止条件以停止传输。停止条件是在SCL线路上从低到高过渡后,SDA线的电压从低到高过渡,SCL线保持高位。

3.6 数据传输的步骤(STEPS OF I2C DATATRANSMISSION)

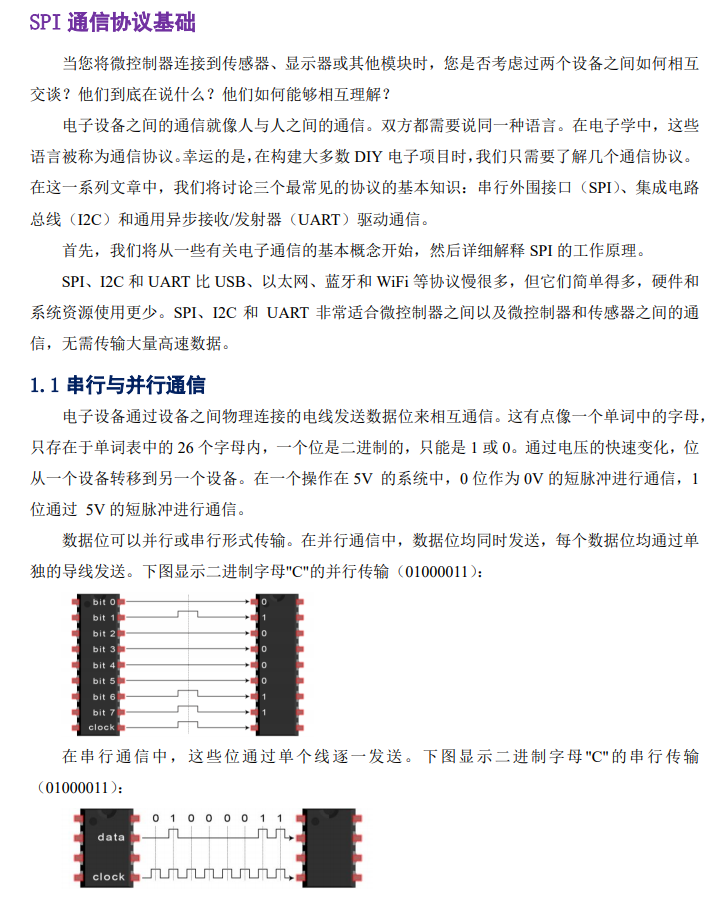

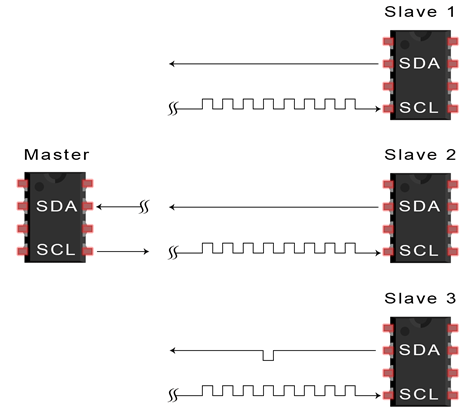

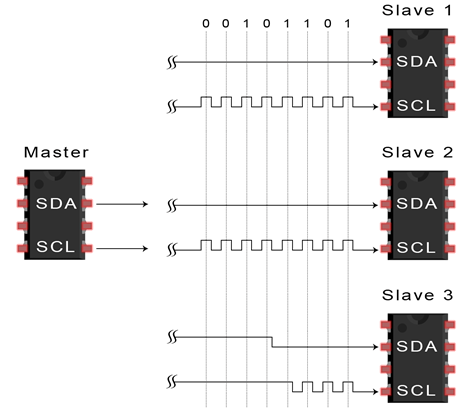

1. 主机发送启动条件给每一个连接的从机,在SCL线从高到低切换之前,主机将SDA线从高切换到低电平即可触发启动条件,即在SCL高电平时候给SDA一个下降沿,如下图所示,注意箭头的时序方向:

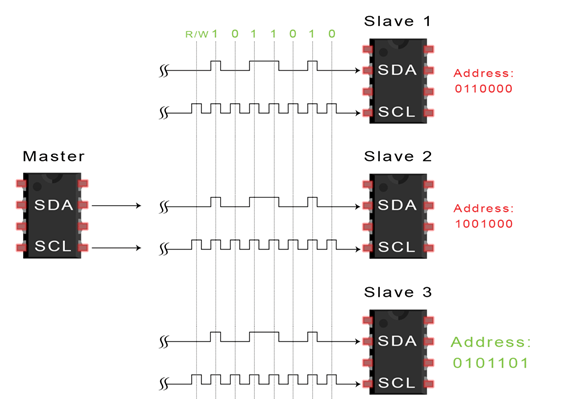

2. 主机发送它想与之沟通的7位或10位从机地址,以及读/写位:

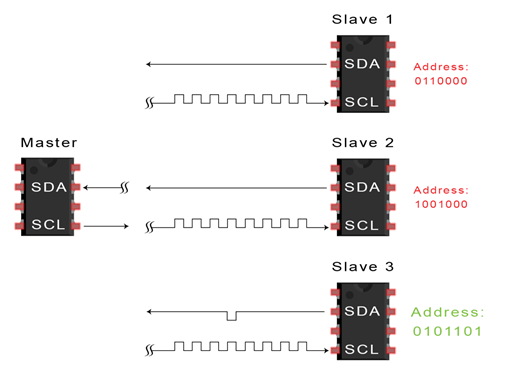

3. 每个从机将从主机发送的地址与自己的地址进行比较。如果地址匹配,则从机通过将SDA 线拉低1个位来返回ACK位。如果主机的地址与从机自己的地址不匹配,则从机会将SDA线留在高电位(通过上拉电阻)。地址匹配的从机返回ACK位如下图所示:

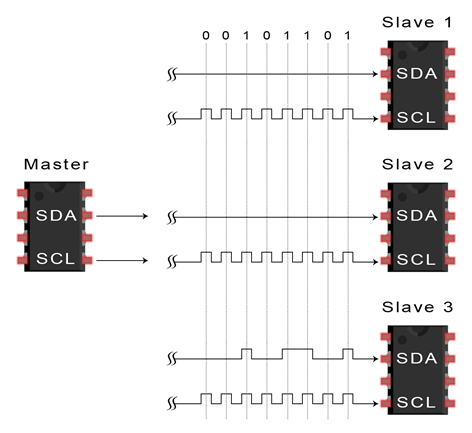

4.主机发送或接收数据帧:

5. 传输每个数据帧后,接收设备会将另一个ACK 位返回给发件人,以确认成功接收帧:

6. 为了停止数据传输,主机发送一个停止条件给从机,通过在SDA拉高之前先拉高SCL,即在SCL高电平时候给SDA一个上升沿,如下图所示,注意箭头表示的传输顺序:

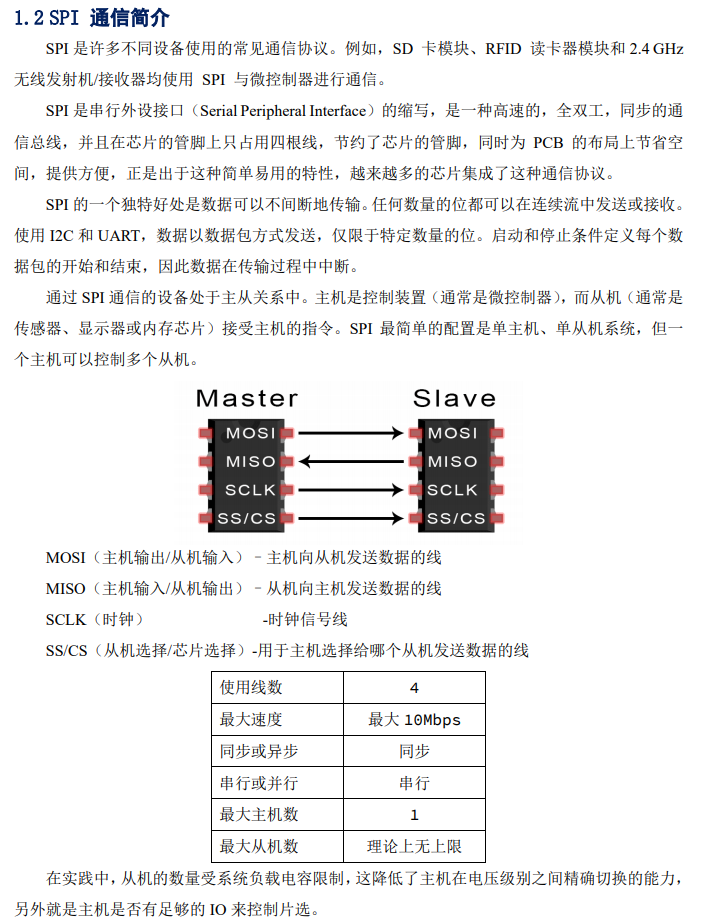

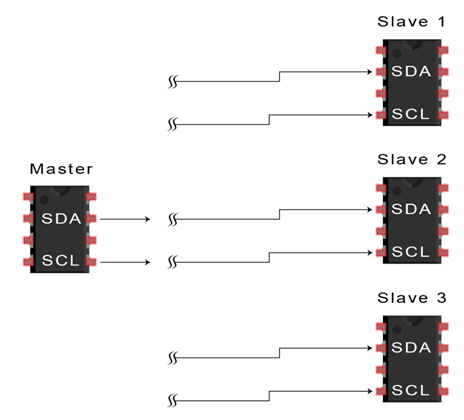

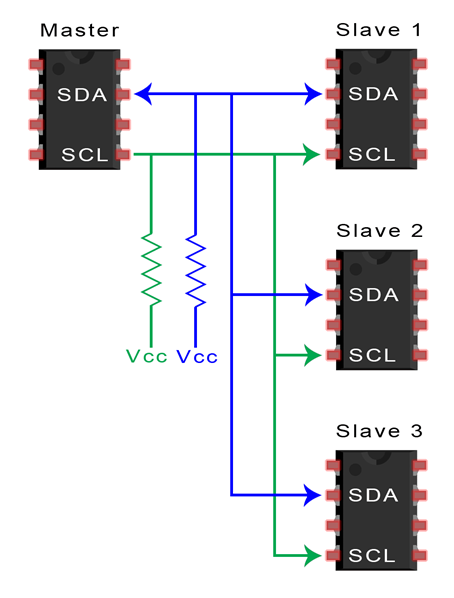

3.7 单主机与多从机(SINGLE MASTER WITH MULTIPLE SLAVES)

由于 使用寻址,因此可以实现单个主机控多个从机。使用7位地址理论上可提供 128(2^7)个唯一地址。使用10位地址并不常见,但理论上可提供1024(2^10)个唯一地址。要将多个从机连接到单个主机,请像下面这样将它们连接起来,并用4.7K Ohm上拉式电阻器将SDA和SCL线连接到Vcc:

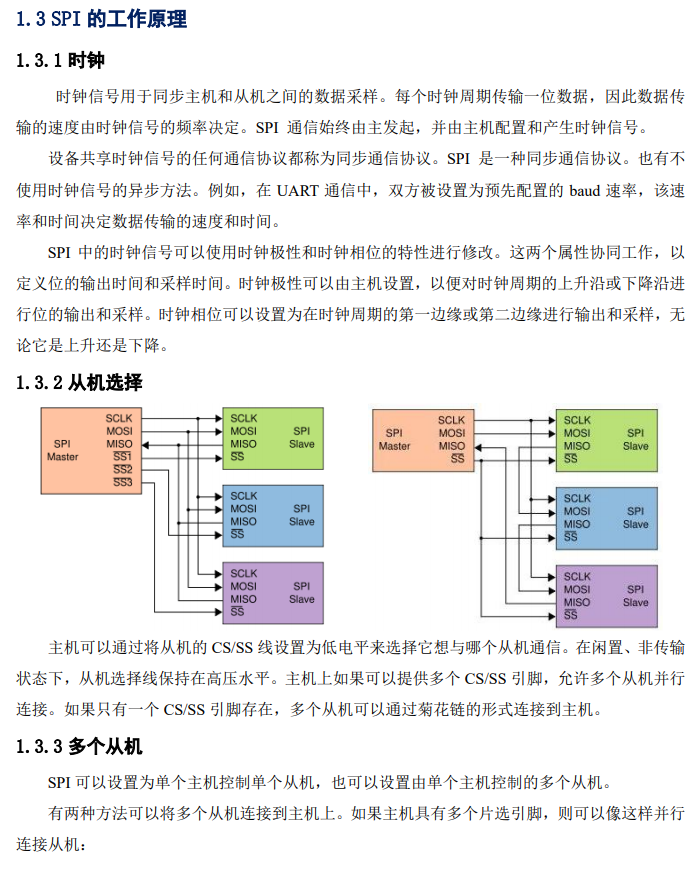

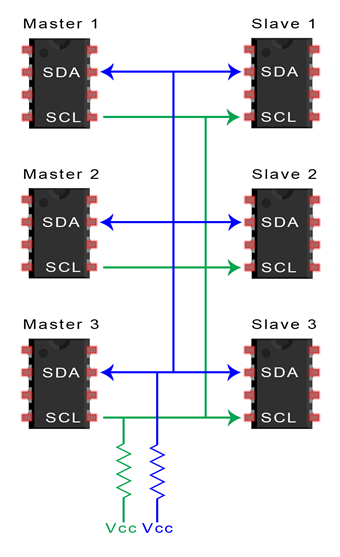

3.8 多主机与多从机(MULTIPLE MASTERS WITH MULTIPLE SLAVES)

多个主机可以连接到一个单一的从机或多个从机。在多主机系统总,当两个主机尝试同时通过SDA线发送或接收数据时,问题就出现了。为了解决这个问题,每个主机在传输消息之前需要检测SDA线是低电平还是高电平。如果SDA线为低电平,则意味着另一个主机正控制着总线,该主机应等待发送消息。如果SDA线被拉高,则传输消息是安全的。

要将多个主机连接到多个从机,请按下图连接,并使用4.7K Ohm上拉式电阻器将SDA和 SCL线连接到Vcc:

3.9 的优缺点(ADVANTAGES AND DISADVANTAGES OF )

优势:

仅使用两根电线

支持多个主和多个奴隶

ACK/NACK 位确认每个帧都成功传输

硬件不如UART复杂

众所周知和广泛使用的协议

缺点:

数据传输速率低于SPI

数据框架的大小限制为8位

实现所需的硬件比SPI更复杂

3.10 总结

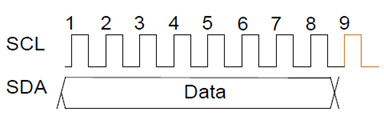

总线由9bit的块构成。开始条件:当SCL是高电平时候SDA从高到底跳变的下降沿,作为开始条件。在总线上的所有从机都要开始注意了:

地址位为紧跟开始条件的7bit数据,主机想要与该地址从机沟通:

读写位为紧跟7bit地址后的第8位作为读写选择位:该位用于表示主机是想读从机的数据还是想往从机里写数据:为1表示读;为0表示写。

主机和从机之间的同步位:0表示ACK;1表示NACK。0:我在或数据已接收。1:没有我或数据未接收。

数据字节:在地址字节后的8位是来自主机或从机的数据字节。至于来自谁,要看读写位。当写周期,主机发送数据;当读周期,从机发送数据:

停止条件:当SCL是高电平时,数据线SDA从低电平跳变到高电平产生的上升沿作为停止条件。主机通知从机本次沟通结束。

完整的总线协议时序,如下图所示:

3.11 备注

本笔记图中带箭头的表示时序传递的优先顺序,箭头表示数据传输的方向或先发生的时序。1.10小结没有标注箭头,以左侧作为先发生的时序,请勿与前面的图弄混。

声明:本文由21ic论坛网友gaoyang9992006翻译自外网和飞利浦相关技术文档,并辅以自己理解。如需高清版PDF文件,请点击文末“阅读原文”进行查看和下载。

END

作者:gaoyang9992006

→点关注,不迷路←